Fターム[5F044KK19]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 電極部 (1,724) | バンプ (984) | 製法 (235)

Fターム[5F044KK19]に分類される特許

141 - 160 / 235

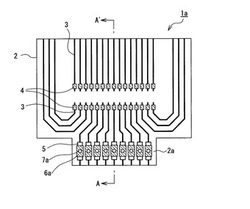

配線基板及びそれを用いた半導体装置ならびにその製造方法

【課題】配線基板にコネクタを装着した場合に、コネクタの導電パッドと配線基板の端子とを確実に接触させ、固定できる配線基板を提供する。

【解決手段】絶縁性基材2と、絶縁性基材2の表面に形成された導体配線3と、導体配線3の長手方向を横切って導体配線3の両側の絶縁性基材上2の領域に亘り形成された第1の突起電極4と、絶縁性基材2の表面に形成され、導体配線3と接続された端子5と、端子5の表面に形成された第2の突起電極6aとを備える。第2の突起電極6aに、端子5の表面が露出されるように形成された開口部7aを備える。

(もっと読む)

基板に取り付けられたスタッドバンプを伴う、フリップチップパッケージング用の可融性入出力相互接続システムおよび方法

【課題】基板に対して、微細なピッチの電極を持つ半導体チップをフェースアップ接続できる方法を提供する。

【解決手段】基板42にある各入出力ボンドパッド50上に、それぞれに対応するスタッドバンプ52を形成し、チップ40にある各入出力ボンドパッド46上に可融材料層48をを形成し、そのスタッドバンプ52上に、裏返しにしたチップ40の入出力ボンドパッド46を位置合わせして載せ加熱することにより、各スタッドバンプ52が、チップ40上のそれぞれに対応する入出力ボンドパッド46と融着されて、基板42にある各入出力ボンドパッド50がチップ40上のそれぞれに対応する入出力ボンドパッド46に電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板と回路基板との接合を確実に達成する。

【解決手段】一対の基板を構成する半導体基板と回路基板との各表面にそれぞれ形成された電極の間に絶縁材料が埋め込まれて、絶縁材料が接着性を発現する第1の温度にて、半導体基板が回路基板に対して傾けられ、仮固定されて、仮固定した複数の一対の基板が真空引きされて、仮固定した複数の一対の基板の表面に均等に圧力を加えて、一対の基板を接合し、圧力を維持するとともに、絶縁材料が硬化する第2の温度にて、接合された絶縁材料が硬化させられて、電極同士が固相拡散を発現もしくは電極同士が融解する第3の温度にて、接合された電極間に金属接合が形成されるようになる。

(もっと読む)

半導体装置の製造方法

【課題】バンプ電極の形成にあたり物理的被着法とめっき法の2種類の方法を用いることによって、半導体装置の小型化、高集積化及び鉛(Pb)フリー化への対応を図りつつ製造の歩留まりを上げて生産性の向上を図るとともに、高い信頼性を確保した半導体装置の製造方法を提供する。

【解決手段】基板3上の外部端子5を覆う絶縁膜6に外部端子5に通じる開口Hを形成する工程と、開口H内において外部端子5上に物理的被着法によりバンプ電極7を生成する第1の金属膜9を形成する工程と、第1の金属膜9及び絶縁膜6の開口H周縁上において無電解めっき法によりバンプ電極7を生成する第2の金属膜11を形成する工程と、第1の金属膜9と第2の金属膜11を溶融しつつ、絶縁膜6上の第2の金属膜11を開口H内に集めてバンプ電極7を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】配線基板にの導体配線に形成された突起電極の位置が、導体配線の長さ方向にずれても、半導体素子の電極パッドと突起電極が対向する面積を十分な大きさに確保可能な半導体装置を提供する。

【解決手段】絶縁性基材1、絶縁性基材上に整列して設けられた複数本の導体配線2、及び複数本の導体配線の各々に形成された突起電極を備えた配線基板と、配線基板上に搭載された半導体素子とを備える。突起電極と半導体素子の電極パッドとが電気的に接続され、半導体素子の中心線と電極パッドとの間の距離が、配線基板の半導体素子の搭載部の中心線C2と導体配線との間の距離dよりも大きい。

(もっと読む)

電子部品の製造方法

【課題】良好な精度で電極パッド上に電気接続部を形成し、信頼性の良好な電子部品を製造する。

【解決手段】電極パッドに対応する穴部が形成されたマスクを用いて、該電極パッド上に半田ボールを設置する第1の工程と、前記半田ボールを加熱して、前記電極パッド上に電気接続部を形成する第2の工程と、を有する電子部品の製造方法であって、前記マスクには、該マスクと前記電極パッドの間隔を保持するとともに該マスクの撓みを防止する撓み防止構造体が設置されていることを特徴とする電子部品の製造方法。

(もっと読む)

半導体チップの順応性インターフェースを形成する方法

【課題】順応性のあるインターフェースを提供する。

【解決手段】半導体チップの順応性インターフェースを形成する方法は、第1の面、第2の面、第2の面にある複数の端子140及び第1の支持構造体の第1の面にある多孔弾性層を有する第1の支持構造体100を提供する工程と、弾性の多孔層が第1の支持構造体と第2の支持構造体との間に配置されかつ第1の支持構造体を第2の支持構造体から隔てるように、第2の支持構造体120の第1の面を多孔層に当接させる工程と、第1の硬化性液体が第1の支持構造体と第2の支持構造体との間に配置されるように、当接工程の後に第1の硬化性液体を多孔層内に配置する工程と、複数の端子をプラテンと係合させることによって複数の端子を互いに略共面整合させる工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】フラックス洗浄における処理時間の短縮化を図る。

【解決手段】薬液に高圧エアーを混入した洗浄液を、高速回転する第1のステージ14a上に配置された複数の半田ボール及び多数個取り基板9に吹き付けてフラックス残渣を浮かせ、さらに第1のステージ14aの横に配置された第2のステージ16a上に多数個取り基板9を移載した後、高速回転する第2のステージ16a上に配置された前記複数の半田ボール及び多数個取り基板9に純水を吹き付けて洗浄する。これにより、前記洗浄液や前記純水を全体に均一に、かつ素早く行き渡らすことができ、短時間でフラックスを洗浄することができる。その結果、フラックス洗浄処理の処理時間を短縮できる。

(もっと読む)

半導体チップ搭載回路の製造方法および実装回路

【課題】半導体チップ搭載回路が導通不良を起こしてしまうことを防止することができる半導体チップ搭載回路の製造方法およびその実装回路を提供すること。

【解決手段】本発明の半導体チップ搭載回路1の製造方法は、主に3つの工程からなる。第1工程においては、実装回路10の接続端子12の表面上に円錐らせん状の接触子2を半田めっき形成する。第2工程においては、接触子2に半導体チップ20のバンプ21を押しつけて導通検査する。最終の第3工程においては、押圧された接触子2を溶融して接続端子12とバンプ21とを接合する。つまり、半導体チップ20および実装回路10が導通検査に合格した状態のままで接合するので、半導体チップ搭載回路1が導通不良を起こすことが極めて少なくなる。

(もっと読む)

配線基板およびその製造方法ならびに電子装置

【課題】半導体光検出素子などの電子素子を搭載するための配線基板において、高精度な平面を有した電子素子搭載部を有する配線基板を提供すること。

【解決手段】絶縁基板1の表面に複数の配線層5が形成された配線基板であって、複数の配線層5の各上面に金属柱端子2を立設し、金属柱端子2の側面に、絶縁被膜4を形成した。

絶縁基板1に影響されることなく立設した金属柱端子2に集中して研磨を行なうことができ、複数の金属柱端子2からなる電子素子3の搭載面をきわめて高い平坦度にすることができる。

(もっと読む)

半導体装置の製造方法及び電気的接続部の処理方法

【課題】外部端子の信頼性が向上する半導体装置の製造方法及び電気的接続部の処理方法を提供する。

【解決手段】半導体装置の製造方法は、(a)半導体基板20と電気的に導通する電気的接続部12,14に、酸を含むペーストを設けること、このとき電気的接続部12,14の材料である金属の還元反応が終了するまで所定時間放置すること、(b)電気的接続部12,14を洗浄することにより、ペーストを電気的接続部12,14から除去すること、(c)電気的接続部12,14に導電部材を設けること、を含む。

(もっと読む)

ハンダ回路基板の製造方法

【課題】プリント配線板上回路電極表面に粘着性を付与し、該粘着部にハンダ粉末を付着させる回路形成法において、ハンダ層の高さが不均一となったり、ハンダバンプが欠損する事のない方法の提供。

【解決手段】プリント配線板上の導電性回路電極表面に粘着性を付与し、該粘着部にハンダ粉末を付着させ、ハンダ回路を形成するハンダ回路基板の製造方法において、回路電極部分をレジストで覆い、導電性回路電極部分に開口部を設け、該開口部の面積を円形とした場合の直径をD1、ハンダ粉末の直径をD2とし、回路電極部分のレジストの厚さをD3とした場合、該各開口部に、D1、D2、D3の間に式(1)の関係のハンダ粉粒子を1個だけ付着させることを特徴とするハンダ回路基板の製造方法。

1>(D1−2×((D2−D3)×D3)1/2)/D2≧0・・・・(1)

(もっと読む)

集積回路パッケージ用サブストレート基板およびその製造方法

【課題】集積回路パッケージ用サブストレート基板に、実装ライン毎に異なる種類の予備半田を設置し、かつ、それによる製造コストの増加を防ぐ方法を提供する。

【解決手段】外層に、予備半田の種類によらず共通の、バンプ接合パッド4をアレイ状に並べたパターンと、半導体集積回路チップの実装領域の認識マーク用パッド5と、前記認識マーク用パッド5の近傍に形成した副認識マーク用パッド6を有し、前記バンプ接合パッド4に設置した予備半田を有し、かつ、第1の種類の予備半田を設置する場合に前記副認識マーク用パッド6に前記予備半田を設置し、第2の種類の前記予備半田を設置する場合に前記副認識マーク用パッド6に前記予備半田を設置しない集積回路パッケージ用サブストレート基板を製造する。

(もっと読む)

半導体装置を実装した回路装置及び半導体装置の実装方法

【課題】 リフロー時の半導体装置と配線基板との収縮差によって生じる応力を緩和して、バンプに生じるクラック等の不具合を防止する

【解決手段】 半導体装置2がバンプ3を介して配線基板5上にフリップチップ実装されている回路装置1であって、前記バンプ3は、半田酸化膜除去作用を有する第一の熱硬化性樹脂4で被覆されている。

(もっと読む)

基板間配線パターンの接続方法及び接続構造

【課題】2つの基板の配線パターンを電気的に確実に接続させる。しかも、接続のために部品数が増加することや接続工程が複雑化することが無い。

【解決手段】表面に導電部となる金属膜を形成した第1の基板11に対し、電極パターン12を形成する金属膜の箇所にレーザ光によって熱エネルギーを照射しその金属膜を溶かして膜表面に盛り上がったバンプ15を形成する。続いて、第1の基板の電極パターンに対し、間に異方導電性接着フィルム31を介在させて第2の基板21の電極パターン22を対向配置させる。この状態で第2の基板の背面から加圧及び加熱して第2の基板の電極パターンを第1の基板の電極パターンのバンプに押圧し、異方導電性接着フィルムを第1の基板と第2の基板との隙間において熱硬化させることで第1の基板の電極パターンと第2の基板の電極パターンを接続する。

(もっと読む)

素子、素子の製造方法、基板、基板の製造方法、実装構造体、実装方法、発光ダイオードディスプレイ、発光ダイオードバックライトおよび電子機器

【課題】基板上に素子を実装する場合に、基板上の配線と素子とを確実に電気的に接続することができ、しかもバンプのさらなる微細化、多ピン接続が可能な実装構造体および実装方法を提供する。

【解決手段】配線基板10の配線12上に弾性体からなる凸部13の少なくとも先端部の表面が導電膜14で被覆された構造の突起部15を少なくとも一つ形成する。素子20上にバンプ22を形成する。配線基板10上に接着剤30を塗布し、この接着剤30に素子20を仮実装する。素子20を配線基板10に対して加圧することにより、配線基板10上の突起部15の少なくとも先端部を素子20のバンプ22に埋没させる。その後、接着剤30を硬化させ、素子20と配線基板10とを接着固定する。

(もっと読む)

電子部品の製造方法

【課題】 基板上に導電性接着剤を用いて接合・固定された電子部品素子を有する電子部品の製造方法であって、周囲の温度変化等が加わった場合であっても接合部分の電気的接続及び機械的接合の信頼性に優れた電子部品を提供する。

【解決手段】 複数の電極ランド11a,11bを有する基板12上に、電子部品素子1Cを導電性接着剤を用いて接合・固定する電子部品の製造方法であって、第1の導電性接着剤7,8を、電子部品素子1Cの第1の導電性接着剤による接合部分の接合界面の面積よりも大きな領域に塗布し、硬化させた後、第1の導電性接着剤7,8の不要部分を除去し、しかる後第2の導電性接着剤14,15を用いて電子部品素子1Cを電極ランド11a,11bに接合する、電子部品の製造方法。

(もっと読む)

多層セラミック電子部品、多層セラミック基板、および多層セラミック電子部品の製造方法

【課題】表面実装型電子部品が実装されるセラミック台座部を備え、高密度実装が可能で、信頼性の高い多層セラミック電子部品、それに用いられる多層セラミック基板、多層セラミック電子部品を効率よく製造するための製造方法を提供する。

【解決手段】セラミック基材層1と、収縮抑制層2とを積層してなる多層セラミック素体3の第1主面4に、セラミック材料からなる台座部本体5と、下側端面6、上側端面7が台座部本体から露出し、下側端面の面積が上側端面の面積より大きい柱状厚膜導体8とを備えたセラミック台座部9であって、柱状厚膜導体の外周面と台座部本体との間に空隙Gを有するセラミック台座部を配設し、セラミック台座部上に、柱状厚膜導体と導通するように第1の表面実装型電子部品10を実装する。

上記空隙Gを、多層セラミック素体に近い下部から多層セラミック素体に遠い上部に向かって大きくなるようにする。

(もっと読む)

埋立パターン基板及びその製造方法

【課題】埋立パターン基板及びその製造方法を提供する。

【解決手段】表面に回路パターンが形成され、スタッドバンプにより回路パターンの層間の電気的導通が具現される印刷回路基板を製造する方法であって、(a)表面にシード層が積層されたキャリアフィルムのシード層にメッキ層を選択的に蒸着して回路パターン及びスタッドバンプを形成する段階と、(b)回路パターン及びスタッドバンプが絶縁層を向くようにキャリアフィルムを絶縁層に積層して加圧する段階と、(c)キャリアフィルム及びシード層を除去する段階と、を含む埋立パターン基板の製造方法は、銅(Cu)スタッドを用いて回路の層間接続を具現するので層間導通のためのドリリングの工程が不要になり、回路設計の自由度が高くなるとともに、ビアランド(Via land)が不要でありビアの大きさが小くなるので回路の高密度化が可能になる。

(もっと読む)

端子電極、半導体装置およびモジュール

【課題】異方性導電層を介して突起電極の接合を行う際に、ACF粒子を突起電極上に効率よく捕らえる。

【解決手段】感光性樹脂層4の露光・現像を行うことにより、パッド電極2上に開口部5を形成し、無電解メッキを用いることにより、パッド電極2に接続された導電層6を開口部5内の途中の高さまで形成し、感光性樹脂層4と導電層6との間に段差を設ける。

(もっと読む)

141 - 160 / 235

[ Back to top ]