Fターム[5F045AD11]の内容

気相成長(金属層を除く) (114,827) | 成膜条件−成膜温度 (8,040) | 700≦T<800℃ (666)

Fターム[5F045AD11]に分類される特許

141 - 160 / 666

半導体素子の製造方法および半導体素子

【課題】発光面積を大きくすることができて発光効率の高い棒状構造の半導体素子の製造方法を提供する。

【解決手段】この半導体素子の製造方法は、n型の半導体コア7の先端面7Aだけでなく側面7Bにもp型の半導体層10を形成するので、pn接合の面積を大きくでき、発光面積を大きくすることができ発光効率を向上できる。また、触媒金属6を用いてn型の半導体コア7を形成するので、n型の半導体コア7の成長速度を速くできる。このため、半導体コア7を長くでき、n型の半導体コア7の長さと比例関係になる発光面積を一層大きくすることができる。

(もっと読む)

発光半導体素子のための成長方法

複数の前駆体及びインジウム表面賦活剤を用いて1つ以上のn型層またはp型層を多重量子井戸(MQW)サブアセンブリに重ねて形成するため、MQWサブアセンブリが低温気相成長プロセスにかけられる、光電発光半導体素子を作製する方法が提供される。前駆体及びインジウム表面賦活剤は1つ以上のキャリアガスを用いてそれぞれの流量で気相成長プロセスに導入され、キャリアガスの少なくとも1つはH2を含む。インジウム表面賦活剤は低温気相成長プロセス中に形成されるp型層の結晶品質を向上させるに十分な量のインジウムを含み、それぞれの前駆体の流量及びキャリアガスのH2含有量はn型層またはp型層内のインジウム表面賦活剤からのインジウムのモル分率をほぼ1%未満に維持するように選ばれる。別の実施形態において、低温気相成長プロセスは低温TGにおいて実行され、ここで、TG≦TB±5%であり、TBはMQW障壁層成長温度である。他の実施形態も開示され、特許請求される。  (もっと読む)

(もっと読む)

化合物半導体基板とその製造方法

【課題】AlGaInP化合物半導体の成長温度を高くすることなく、低い酸素原子濃度を有し、表面欠陥の小突起が発生しにくいAlGaInP化合物半導体の製造方法、およびそれにより得られるAlGaInP化合物半導体基板を提供する。

【解決手段】筐体の内部に配置された反応炉の内部で化合物半導体基板を製造する方法であって、前記筐体の内部を酸素濃度が45ppm以下の雰囲気に保ったまま、ベース基板を筐体の内部であって反応炉の外部から、反応炉の内部に移動し、前記ベース基板を前記反応炉の内部に配置する段階(1)と、前記反応炉の内部に配置されたベース基板の上に化合物半導体を700℃以下でエピタキシャル成長させる段階(2)とを含む化合物半導体基板の製造方法。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】エピタキシャル成長により形成された結晶膜の成長面内における物性値を均一な値に近づける。

【解決手段】第1化合物半導体および第2化合物半導体を積層した積層半導体を含み、前記第1化合物半導体の所定物性値が第1面内分布を有し、前記第2化合物半導体の前記所定物性値が前記第1面内分布とは異なる第2面内分布を有し、前記積層半導体における前記所定物性値の面内分布の幅が、前記第1面内分布の幅または前記第2面内分布の幅より小さい半導体基板を提供する。

(もっと読む)

CMOSデバイス用シリコンウェハの製造方法

【課題】 同じ特性のn−MOSトランジスタとp−MOSトランジスタとを有し、n−MOSトランジスタに最適な応力による歪特性をもたらすSiGe膜と、p−MOSトランジスタに最適な応力による歪特性をもたらすSiC膜とを同一シリコン基材上に備えた、小さいサイズのトランジスタに対しても、最適な特性を持つCMOSデバイス用のシリコンウェハの製造方法の提供。

【解決手段】 CMOSデバイス用シリコンウェハの製造方法において、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に分離して製造する。

(もっと読む)

ZnO系化合物半導体の製造方法及び半導体発光素子

【課題】 安定したp型ZnO系半導体結晶を得ることが可能なZnO系化合物半導体の製造方法を提供する。

【解決手段】 ZnO系化合物半導体の製造方法は、単結晶表面を有する基板を準備する工程と、亜鉛ビームと、酸素を含むガスをラジカル化した酸素ラジカルビームと、N2ガスとO2ガスとを混合したガスをラジカル化した窒素ラジカルビームとを、前記基板上に同時に照射して、窒素添加p型ZnO系化合物半導体を結晶成長する工程とを有し、前記N2ガスとO2ガスとを混合したガスの混合比O2/N2が、0より大きく1以下である。

(もっと読む)

窒化物半導体エピタキシャル層の形成方法および窒化物半導体デバイスの製造方法

【課題】窒化物半導体基板から窒化物半導体エピタキシャル層を分離する際に窒化物半導体エピタキシャル層に与えるダメージが低く高品質な窒化物半導体エピタキシャル層の形成方法を提供する。

【解決手段】本窒化物半導体エピタキシャル層の形成方法は、転位密度が1×107cm-2以下の窒化物半導体基板10上に、ガスおよび電解液の少なくともいずれかにより化学的に分解する化学的分解層20を介在させて、少なくとも1層の窒化物半導体エピタキシャル層30を成長させる工程と、窒化物半導体エピタキシャル層30を成長させる工程中およびこの工程後の少なくともいずれかにおいて、ガスおよび電解液の少なくともいずれかを用いて化学的分解層20を分解させることにより、窒化物半導体基板10から窒化物半導体エピタキシャル層30を分離する工程と、を備える。

(もっと読む)

窒化物薄膜成膜装置

【課題】常圧下で窒化源を用いたIII−V族半導体薄膜の結晶成長を行う窒化物薄膜成膜装置において、ガスの流量を維持しつつ、成膜されるシリコン窒化膜の膜厚を均一にすることができる窒化物薄膜成膜装置を提供する

【解決手段】基板10の表面に、常圧下において窒化源を用いてIII−V族窒化物半導体薄膜を成膜するためのシランガスとアンモニアガスとを含むガスを供給源としてシリコン窒化膜を成膜する窒化物薄膜成膜装置100であって、基板が載置されるサセプタ12aと、サセプタを下面から加熱するヒータ13と、サセプタの上面の前記ヒータによる均熱領域内に、基板の上流側に設けた基板の上面より高さが高い石英製のリング(障壁部材)11とを備えることを特徴とする。

(もっと読む)

半導体基板とその製造方法

【課題】立方晶炭化珪素(3C−SiC)に対してより格子ミスマッチの少ないバッファ層を形成することで、高品位(高品質)な炭化珪素単結晶膜を形成した半導体基板と、その製造方法を提供する。

【解決手段】少なくとも一面に単結晶シリコンを有するシリコン基板1と、単結晶シリコン上に設けられた、コバルトシリサイドを主に含んでなるコバルトシリサイド層(2a、2b、2c)を一層以上有したバッファ層2と、バッファ層2上に設けられた、炭化珪素単結晶膜3と、を含む半導体基板10。

(もっと読む)

半導体、半導体素子、半導体の製造方法および半導体素子の製造方法

【課題】 非極性面上に低抵抗な半導体結晶が形成された半導体を提供する。

【解決手段】 本発明の半導体は、基板101と、前記基板101の主面上に積層されたp型層108および109とを含み、前記基板主面は、非極性面であり、前記p型層108および109は、III族窒化物半導体およびII族酸化物半導体の少なくとも一方から形成され、且つ、前記p型層108および109の上面が、前記基板主面と面方位が異なるファセット面を含むことを特徴とする。

(もっと読む)

半導体基板の製造方法

【課題】立方晶炭化珪素の単結晶膜を高品位(高品質)に作製することができる、半導体基板の製造方法を提供する。

【解決手段】少なくとも一面に単結晶シリコンを有する基板(シリコン基板1)の一面1a上に、炭素を主に含んでなる炭素層を形成する工程と、炭素層に電磁波を照射して加熱し、炭化珪素を含む炭化緩衝層3を形成する工程と、を含む半導体基板5の製造方法。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】反応炉内の堆積膜に十分にクラックを発生させ、それにより、成膜処理中における堆積膜の剥離や、パーティクルの発生を抑制する。

【解決手段】第1の温度に設定された反応炉内に基板を搬入する工程と、反応炉内を前記第1の温度よりも高い第2の温度に設定する工程と、第2の温度に設定された前記反応炉内で基板に対して成膜処理を行う工程と、成膜処理後の基板を前記反応炉内より搬出する工程と、成膜処理後の基板を搬出後、反応炉内に前記基板がない状態で、反応炉内を強制冷却して反応炉内の温度を前記第1の温度よりも低い第3の温度まで降下させつつ反応炉内をガスパージする工程と、反応炉内の温度を第3の温度に所定の時間保持した状態で反応炉内をガスパージする工程とを有する半導体装置の製造方法を提供する。反応炉内の温度を第3の温度に所定の時間保持することにより、反応炉内に付着した堆積膜により効果的に亀裂を発生させ、亀裂により生じた微細パーティクルを効率的に反応炉外に排出する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】例えば500℃以上700℃以下の低温において、原子状酸素Oの濃度をウエハ積層方向に渡りコントロールし、酸化膜の膜厚分布をウエハ積層方向に渡り均等化する。

【解決手段】処理室内の複数枚の基板が配列される基板配列領域の一端側から酸素含有ガスと水素含有ガスとを混合部を介して供給してその他端側に向かって流すと共に、処理室内の基板配列領域に対応する途中の複数箇所から水素含有ガスを供給して他端側に向かって流すことで複数枚の基板を酸化処理する工程を有し、混合部内で酸素含有ガスと水素含有ガスとを反応させて原子状酸素を含む酸化種を生成させ、酸化種を混合部内から処理室内に噴出させる噴出口の位置にて酸化種の濃度が最大となるようにする。

(もっと読む)

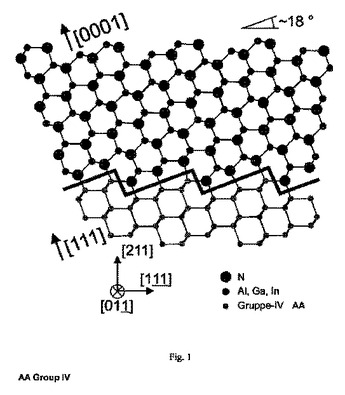

半極性ウルツ鉱型III族窒化物をベースとする半導体層、及び当該窒化物をベースとする半導体部材

III族窒化物層は、電子工学及び電子光学の分野で適用範囲が広い。このような層の成長は通常、サファイア、SiC、近年ではSi(111)のような基板上で行われる。この際に得られる層は通常、成長方向において極性、及び/又はC軸配向性である。電子光学における多くの適用にとって、またSAWにおける音響的な適用でも、非極性、又は半極性III族窒化物層の成長は、関心の対象であり、また必要とされている。本方法により、極性が低減されたIII族窒化物層の容易かつ安価な成長が、事前に基板を三次元構造化することなく、可能になる。  (もっと読む)

(もっと読む)

電流密度操作を用いた電力発光ダイオード及び方法

390−415nmの波長で発光する発光ダイオードデバイスは、活性領域を有したバルクガリウム及び窒素含有基板を有している。このデバイスは約175Amps/cm2を超える電流密度を有している。また、このデバイスは、ロールオフが約5%未満の絶対効率である外部量子効率を有している。 (もっと読む)

半導体発光素子の製造方法およびランプ、電子機器、機械装置

【課題】大電流が印加されることにより高い発光出力が得られる半導体発光素子を製造できる半導体発光素子の製造方法を提供する。

【解決手段】第1有機金属化学気相成長装置において、基板11上に、第1n型半導体層12aを積層する第1工程と、第2有機金属化学気相成長装置において、第1n型半導体層12a上に、第1n型半導体層12aの再成長層12dと第2n型半導体層12bと発光層13とp型半導体層14とを順次積層する第2工程とを具備し、第2工程において、第2n型半導体層12を形成する際の基板温度を、発光層13を形成する際の基板温度よりも低くする半導体発光素子の製造方法とする。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】加熱室内の圧力調整を容易とし、薄膜の膜質や膜厚分布の均一性を改善する。

【解決手段】基板を処理する処理室と、処理室内に処理ガスを供給するガス供給手段と、ガス供給手段に設けられるガス加熱部と、を備え、ガス加熱部は、処理室内に供給する処理ガスを予め所定温度に加熱する加熱室と、加熱室内の圧力を検出する圧力検出手段と、圧力検出手段の検出する圧力情報に基づき加熱室内の圧力を調整する圧力調整手段と、を有する。

(もっと読む)

化合物半導体膜の製造方法、化合物半導体膜及び半導体デバイス

【課題】化合物半導体結晶中への亜鉛の取り込み量を増やすことができる化合物半導体膜の製造方法、化合物半導体膜及び当該化合物半導体膜を用いた半導体デバイスを提供することを目的とする。

【解決手段】亜鉛をドープするp型化合物半導体膜のエピタキシャル成長時に、亜鉛含有原料(例えば、ジエチル亜鉛;DEZn)と共に所定範囲の供給量のSb含有原料(例えば、トリスジメチルアミノアンチモン;TDMASb)を供給することにより、化合物半導体膜(例えば、InGaAs膜)中への亜鉛の取り込み量を増やす。

(もっと読む)

カーボンナノチューブ製造用基材の製造方法、カーボンナノチューブの製造方法、半導体装置、及び半導体装置の製造方法

【課題】イオン注入法を用いつつ触媒元素の成長核が形成されたカーボンナノチューブ製造用基材の製造方法、この基材を用いたカーボンナノチューブの製造方法、半導体装置、及び半導体装置の製造方法を提供すること。

【解決手段】カーボンナノチューブ製造用基材の製造方法は、表面に絶縁膜25が位置し且つ所定の結晶方位を有する基板21’に対し、この基板21’を1000℃以下の所定温度に調節した状態にて、触媒元素のイオンを注入することで、触媒元素を含む成長核27を、基板21’と絶縁膜25との界面に形成させる成長核形成工程を有する。

(もっと読む)

窒化物系半導体装置の製造方法

【課題】異種基板から良質のGaN系半導体層が得られる窒化物半導体装置の製造方法を提供する。

【解決手段】本発明による窒化物系半導体装置の製造方法は、基板上にAlN核生成層を成長させる段階と、上記AlN核生成層上にGaNバッファ層を成長させる段階と、上記基板をアニーリングする段階とを含み、上記AlN核生成層はAlNの結晶核の臨界半径より大きくAlNの臨界弾性厚さより薄い厚さを有するように形成され、上記GaNバッファ層はGaNの結晶核の臨界半径より大きくGaNの臨界弾性厚さより薄い厚さを有するように形成され、上記アニーリング時間はL2/DGa(L;Gaの拡散距離、DGa;上記AlN核生成層におけるGaの拡散係数)より大きい。

(もっと読む)

141 - 160 / 666

[ Back to top ]