Fターム[5F045DB09]の内容

気相成長(金属層を除く) (114,827) | 半導体層の選択成長 (353) | マスクレス成長 (38)

Fターム[5F045DB09]に分類される特許

1 - 20 / 38

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

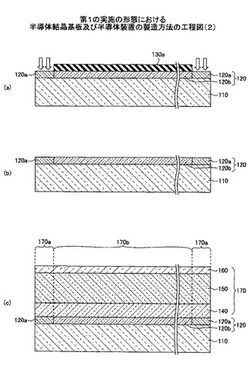

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

炭化珪素単結晶の製造方法

【課題】p層とn層を順次積層させなくても、多形や転位の引継ぎを抑制しつつ、貫通転位を低減できるSiC単結晶の製造方法を提供する。

【解決手段】縦型MOSFETのドレインリークなどのリークを引き起こす転位は貫通らせん転位であるということに基づき、Alイオンの注入および活性化アニール後に溶融KOHエッチング等を行うことにより、リーク部に相当する場所に非常に深いエッチピット1bを形成する。そして、その表面に、エッチピット1bの側壁部に成長した部分同士が互いに接触する条件にてSiC成長層4をエピタキシャル成長させることで、SiC成長層4に転位が引き継がれないようにする。これにより、貫通らせん転位1aが存在しない表面を有するSiC成長層4を得ることが可能となる。したがって、p層とn層を順次積層させなくても、多形や転位の引継ぎを抑制しつつ、貫通転位を低減できるSiC単結晶を製造することができる。

(もっと読む)

UV線を用いたシリコン含有膜の低温エピタキシャル成長

【課題】シリコン含有及び/又はゲルマニウム含有膜の一括的又は選択的エピタキシャル堆積の清浄な基板表面を調製する方法を提供する。更に、シリコン含有及び/又はゲルマニウム含有膜を成長させる方法であって、基板洗浄方法と膜成長方法の双方が750℃未満、典型的には約700℃〜約500℃の温度で行われる前記方法を提供する。

【解決手段】洗浄方法と膜成長方法は、シリコン含有膜が成長している処理容積において波長が約310nm〜約120nmの範囲にある放射線の使用を用いる。反応性洗浄又は膜形成成分化学種の具体的な分圧範囲と組み合わせたこの放射線の使用は、業界で以前に知られている温度より低い温度で基板洗浄とエピタキシャル膜成長を可能にする。

(もっと読む)

選択成膜方法、成膜装置、及び構造体

【課題】炭素を含む膜を選択成長させること。

【解決手段】主面上にトレンチとポストが形成された基板13上に、選択的に炭素を有した膜を、プラズマCVD法により堆積する選択成膜方法である。基板を設置する反応室11において、第1電力により、膜の原料ガスのプラズマを生成し、反応室と連通し、区画された補助空間21において、第2電力により、基板に対してエッチング性を有するガスのプラズマを生成して、反応室に、イオン及びラジカルを供給する。反応室において、基板の主面に垂直方向に電界を発生させるバイアス電圧を制御して、基板のポストの上面、トレンチの側面及び底面に至るイオン量を制御する。第1電力、第2電力、バイアス電圧を制御することにより、基板の前記ポストの上面、トレンチの側面及び底面のうちの選択された1つの面、又は、2つの面に対して、膜を成膜する。

(もっと読む)

III族窒化物半導体の成長方法

【課題】比較的小さい膜厚で結晶性の良いIII族窒化物半導体の結晶を成長させることができるIII族窒化物半導体の成長方法を提供する。

【解決手段】本発明のIII族窒化物半導体の成長方法は、基板(10)上に、III族窒化物半導体の結晶核(40)を島状に形成する第1の工程と、窒素源ガスを供給しながら珪素源ガスとIII族源ガスを交互に供給することにより、前記結晶核(40)を島状に成長させる第2の工程と、該第2の工程後、窒素源ガスとIII族源ガスを供給し、前記島状の結晶核(40)からIII族窒化物半導体を各々成長させ、層状のIII族窒化物半導体(45)を形成する第3の工程と、を具備することを特徴とする。

(もっと読む)

エピタキシャルウエハの製造方法

【課題】 半導体ウエハの端面に角張った形状の結晶層を成長させることなく、半導体ウエハ上に厚い単結晶層を成長させることができる技術を提供する。

【解決手段】 半導体ウエハ10上に単結晶層30が形成されたエピタキシャルウエハの製造方法であって、平坦な上面12と、平坦な下面14と、上面12と下面14を接続する端面16を有する半導体ウエハ10の端面16上に、アモルファス層20を形成するアモルファス層形成工程と、アモルファス層形成工程後に、半導体ウエハ10の上面12上に、80μm以上の厚みを有する単結晶層30を気相成長させる単結晶層形成工程を有する。

(もっと読む)

窒化物半導体層の成長方法、及びそれにより形成される窒化物半導体基板

【課題】 窒化物半導体層の成長方法、及びそれにより形成される窒化物半導体基板を提供する。

【解決手段】 基板を準備し、該基板上に窒化物半導体ドットを形成し、窒化物半導体ドット上に窒化物半導体層を成長させる窒化物半導体層の成長方法である。このように成長された窒化物半導体層を基板から分離して、窒化物半導体基板として使用できる。

(もっと読む)

窒化物半導体の成長方法

【課題】安価に、反りの少ない窒化物半導体を成長することができる窒化物半導体の成長方法を提供する。

【解決手段】本発明の窒化物半導体の成長方法は、気相成長法により、基板10上に、窒化物半導体の結晶からなる第1凹凸構造30を形成し、該第1凹凸構造30の凸部の上部から窒化物半導体を選択的に成長させることにより、前記第1凹凸構造30上に、窒化物半導体の結晶からなる第2凹凸構造32を形成することを特徴とする。

(もっと読む)

窒化物半導体デバイス

【課題】 ウエハ−プロセスで基板の上に製造された素子単位をチップ分離する際に研磨、切断などの工程を減らすことができ、基板を繰り返し使用できる窒化物半導体デバイス作製方法によって作製したデバイスを提供する。

【解決手段】 閉曲線をなす結晶成長速度の遅い欠陥の集合した欠陥集合領域Hと結晶成長速度の速い低欠陥の領域ZYの位置が予め決まっている窒化物半導体欠陥位置制御基板Sを用い、低欠陥領域ZYにデバイスの内部が、欠陥集合領域Hに境界線が来るように窒化ガリウム基板の上に窒化物半導体層(上層部B)をエピタキシャル成長させ、レーザ照射或いは機械的手段で欠陥位置制御基板Sと成長層(上層部B)を上下方向横方向に同時分離し、基板は繰り返し使用する。作製されたデバイスは端面が成長によるファセットで形成されている。

(もっと読む)

半導体デバイスおよび半導体構造の製造方法

【課題】 半導体結晶材料の作製またはこの半導体結晶材料を含む構造を提供する。

【解決手段】 第1の半導体結晶材料の表面の粗さは、低減されている。半導体デバイスは、第1の結晶材料の表面上に低欠陥の歪んだ第2の半導体結晶材料を含む。歪んだ第2の半導体結晶材料の表面の粗さは、低減されている。一実施例は、第1および第2の半導体結晶材料間の界面境界の不純物を減少させるプロセスパラメータを作成することによって、粗さが低減された表面を得ることを含む。一実施の形態では、第1の半導体結晶材料は、アスペクト比トラッピング技術を用いて欠陥をトラップするのに十分なアスペクト比を有する絶縁体の開口によって限定されることができる。

(もっと読む)

薄膜堆積方法およびその装置

【課題】本発明は、従来のCVD装置で用いることの出来なかった材料により成膜を可能にし、さらに不純物が混じらない高品質の成膜を可能とした薄膜堆積方法および装置を提供することを目的とする。

【解決手段】非平衡プラズマにより原料ガス14に与えるエネルギーと、原料ガス14より生成する目的の反応生成物固有のポテンシャルエネルギーとの差分のエネルギーを求め、ポテンシャルエネルギーが不足の場合、前記差分のエネルギーを補充するレーザ光19の波長を求め、ポテンシャルエネルギーが余剰の場合、差分のエネルギーを誘導放出により放出するレーザ光19の波長を求め、非平衡プラズマ化された原料ガス14に、求めた波長のレーザ光19を照射して、原料ガス14の基底準位を前記ポテンシャルエネルギーに遷移し、原料物質より目的の反応生成物を解離または分解し、被成膜物質12に堆積して成膜する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】選択性及び基板面内の膜厚均一性を保ちながら十分厚いエピタキシャル膜を成長

させることができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】

表面に少なくともシリコン露出面とシリコン酸化膜もしくはシリコン窒化膜の露出面とを備える基板を処理室内に搬入する工程と、

前記処理室内の前記基板を所定の温度に加熱した状態で前記処理室内に、少なくともシリコンを含む第1の処理ガスとエッチング系の第2の処理ガスとを共に供給する第1のガス供給工程と、

前記処理室内に、前記第2の処理ガスよりエッチング力の強いエッチング系の第3の処

理ガスを供給する第2のガス供給工程と、

を少なくとも含み、前記第1のガス供給工程と前記第2のガス供給工程とを少なくとも1回以上実施し、前記基板表面のシリコン露出面に選択的にエピタキシャル膜を成長させる。

(もっと読む)

イオンの注入による窒化物半導体の形成方法及びこれを利用して製造した電子素子

【課題】本発明は、イオンの注入による窒化物半導体の形成方法及びこれを利用して製造した電子素子に関する。

【解決手段】本発明は、基板100の表面に1E17イオン/cm2超過、5E18イオン/cm2以下のドーズ量及び30〜50keVの注入エネルギーでライン/スペースパターンからなるイオン注入領域120を形成した後、金属窒化物薄膜130を水平成長させることにより、窒化物薄膜の格子欠陥を減少させ、よって電子素子の効率を向上させることができるようにする。

(もっと読む)

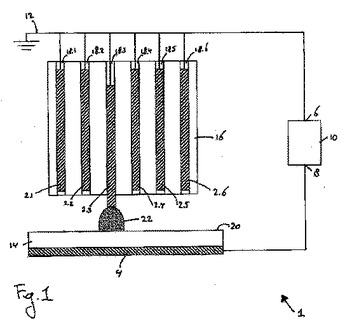

基板の表面をパターニングするためにプラズマ放電を起こすデバイス

基板の表面をパターニングするためにプラズマ放電を起こすデバイスは、第1の放電部分を含む第1の電極および第2の放電部分を含む第2の電極と、第1および第2の電極間に高電圧差を発生させる高電圧源と、第1の電極を基板に対して位置決めする位置決め手段とを含み、位置決め手段は、第1の放電部分と第2の放電部分との間の距離が高電圧差のプラズマ放電を助長するのに十分に小さい第1の位置、および第1の放電部分と第2の放電部分との間の距離が高電圧差のプラズマ放電を防止するのに十分に大きい第2の位置に、第1の電極を第2の電極に対して選択的に位置決めするように構成される。  (もっと読む)

(もっと読む)

基板構造体及びこの基板構造体を除去する方法

【課題】 半導体層と基板をエッチングで分離する効率を高め、かつプロセスにかかる費用を抑えることができる、基板構造体を除去する方法の提供。

【解決手段】 本発明の基板構造体を除去する方法は、基板上にフォトリソグラフィーエッチング方式で複数の柱状体を製作し、前記複数の柱状体上にIII族窒化物半導体層を成長させ、化学エッチング方式で複数の柱状体をエッチングし、前記III族窒化物半導体層と前記基板を分離する。

(もっと読む)

半導体をその基板から分離する方法

【課題】 本発明の目的は半導体をその基板から分離する方法を提供することである。

【解決手段】 複数の棒状体を基板上に形成し、複数の棒状体上で半導体層をエピタキシー成長させ、更に、複数の棒状体の間の空隙にエッチング液を注入することによって、半導体層をその基板から分離する。複数の棒状体の間の空隙がエッチングの反応面積を大幅に増加させることができるため、本発明による方法によれば、エッチングによって半導体層を基板から分離する効率を向上させ、製造工程のコストを低減させることができ、しかも、基板に使われる材料も前記分離方法に制限されない。

(もっと読む)

化合物半導体基板およびその製造方法

【課題】反りが抑制され、結晶性を低下させることなく、高品質なSiC膜が形成された化合物半導体基板およびその製造方法を提供する。

【解決手段】Si基板10の表面10aに、前記Si基板10の表面10aに該表面10aにおける幅Wおよび該表面10aからの深さDが、SiC膜20の厚さよりも大きい溝部30を形成し、前記Si基板10の表面10aに、前記溝部30によって島状にそれぞれ分離された複数のSiC島部20aとして、SiC膜20を形成する。

(もっと読む)

半導体素子及び結晶成長基板

【課題】ピエゾ電界の悪影響を派生問題なく効果的に緩和若しくは最小化する。

【解決手段】各非縦方向成長部4の上面では、xy平面に平行にr面が結晶成長し、これらの個々のr面は、側壁面1bの近傍に若干のボイド5を形成しつつも、ストライプ溝Sを完全に覆い隠すまで結晶成長して、最終的には略一連の平坦面が形成される。この時以下の結晶成長条件下で50分間、非縦方向成長部4のファセット成長を継続する。このファセット成長の条件設定は、継続的かつ順調なファセット成長を促進する上で重要である。また、下記の結晶成長速度は、r面に垂直な方向の結晶成長速度である。

結晶成長温度 : 990〔℃〕

結晶成長速度 : 0.8〔μm/min〕

供給ガス流量比(V/III 比): 5000

(もっと読む)

窒化物系半導体発光素子およびその製造方法

【課題】製造プロセスが複雑になるのを抑制することが可能で、かつ、発光効率の低下を抑制することが可能な窒化物系半導体発光素子を提供する。

【解決手段】この窒化物系半導体レーザ素子50(窒化物系半導体発光素子)は、n型GaN基板1の(1−100)面からなる主表面上に下地層2を介して形成され、(1−100)面を主面とする発光層6を有する半導体レーザ素子層3と、半導体レーザ素子層3の発光層6を含む領域の端部に形成され、発光層6の主面((1−100)面)に対して略垂直な方向に延びる(000−1)面からなる光出射面20aと、(000−1)面からなる光出射面20aと対向する領域に形成され、半導体レーザ素子層3の成長面からなり、光出射面20aに対して角度θ1(約62°)傾斜した方向に延びる反射面20cとを備える。

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】シード層の結晶欠陥を低減し、良質なSiC基板を製造する。

【解決手段】本発明の半導体基板の製造方法は、絶縁層20上にSiC層30を備えた半導体基板1の製造方法である。支持基板10上に絶縁層20とSi層50とが順次形成されてなるベース基板100のSi層50に、絶縁層20を露出させる溝部40を形成し、溝部40によってSi層50を複数の島状のSi部55に区画するSi部区画工程と、Si部55を炭化して島状のシード部65を形成し、シード部65からなるシード層60を形成するシード層形成工程と、シード部65をエピタキシャル成長させて島状のSiC部35を形成し、SiC部35からなるSiC層30を形成するSiC層形成工程と、を有する。

(もっと読む)

1 - 20 / 38

[ Back to top ]