Fターム[5F048BA02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997)

Fターム[5F048BA02]の下位に属するFターム

3層以上 (202)

基板と直上の層が同型 (184)

基板と直上の層が異型 (194)

Fターム[5F048BA02]に分類される特許

401 - 417 / 417

パワートランジスタ装置及びそれを用いたパワー制御システム

【課題】 トレンチ構造のトランジスタを使用するパワーMOSトランジスタを過電流から保護し、信頼性を向上させる。

【解決手段】 パワーMOSトランジスタ(11)と該パワーMOSトランジスタの電流を検出して外部の制御回路(30)に供給する検出信号を生成するための電流検出用トランジスタ(12)およびパワーMOSトランジスタの電流を検出して所定以上の電流が流れたときに強制的にパワーMOSトランジスタのゲート電圧を下げることにより電流を抑える保護回路を構成する素子(14,RS1)を同一半導体チップに設けるようにした。

(もっと読む)

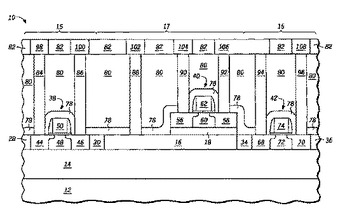

パワー半導体デバイス

垂直絶縁ゲート電界効果パワー・トランジスタ(3)は、2つのトランジスタ・セル(TC3)の間毎の境界において周辺ゲート構造(G31,G32)を有する複数の並列のトランジスタ・セル(TC3)を有する。ゲート構造(G31,G32)は、独立して動作可能となるように互いに絶縁された第1(G31)および第2(G32)のゲートを含む。第1のゲート(G31)は、トレンチ・ゲート(21,22)であり、第2のゲート(G32)は、少なくとも絶縁平面状ゲート部分(13,14)を有する。第1(G31)および第2(G32)のゲートが同時に動作することによって、デバイス(3)のソース領域(16)とドレイン領域(12)の間に伝導チャネル(23c,23b)が形成される。デバイス(3)は、トレンチ・ゲート・デバイスのオン状態抵抗値に近づくオン状態抵抗値を有し、スイッチング性能がDMOSデバイスより良好であり、安全動作領域がトレンチ・ゲート・デバイスより良好である。デバイス(3)は、安定化出力電圧を供給するための回路構成(50)(図14)中でロー側パワー・トランジスタ(6)と直列に接続されたハイ側パワー・トランジスタとすることができる。デバイス(3)は、負荷(L)に電流を供給するための回路構成(60)(図15)中でスイッチとすることもできる。これらの回路構成(50,60)は、第1のゲート(G31)用の電極(G311)に、供給される固定電位を加えるための端子(Vcc,VF)と、第2のゲート(G32)用の電極(G321)に変調電位を加えるためのゲート・ドライバ回路(573、673)とを含む。  (もっと読む)

(もっと読む)

センス構造体を備える半導体デバイス

パワーセル(14)及びセンスセル(16)に分割される複数のセルを備えるパワー半導体デバイスが記載されている。センスセル(16)の複数のグループ(30、32)がもたらされる。本デバイスは、センスセル(16)のグループの縁においてもたらされる効果の補償を可能にする。  (もっと読む)

(もっと読む)

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】更なる微細化を促進できる半導体装置の製造方法を提供すること。

【解決手段】 第1の半導体層1上に、第1半導体層1よりも絶縁化し難い第2半導体層3を形成する工程と、第2半導体層3の上面から第1半導体層1にかけて、第2半導体層3、及び第1半導体層1を露出させる溝7を形成する工程と、溝7から露出する第1半導体層1、及び第2半導体層3を絶縁化し、溝を、絶縁化した第1半導体層9で閉じる工程とを具備する。

(もっと読む)

高く、かつ広い作動電圧レンジのためのバイアス回路を備えるゲートドライバー出力ステージ

【課題】ICデバイスの通常の最大電圧定格よりも高い電圧において、より広い電圧レンジで作動できるゲートドライバーを提供する。

【解決手段】 簡単で、低コストのゲートドライバー、およびバイアス回路は、NMOSトランジスタおよびPMOSトランジスタのような構成部品の通常の部品のブレークダウン電圧を超える、より広い作動電圧レンジを可能にしている。回路を実現するために、バルクおよびPタイプの基板として、エピタキシャル層を備えるCMOSプロセスを使用する。

(もっと読む)

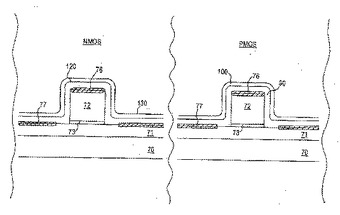

チャネルキャリア移動度向上のための高応力ライナーを備えたSi−Geに基づく半導体デバイス

応力ライナーを用いることで、Si−Geデバイスのトランジスタのチャネル領域のキャリア移動度が増加される。一実施形態においては、緩和ソース/ドレイン領域を覆う高圧縮膜あるいは高引っ張り応力膜を適用する。他の実施形態としては、ポストシリサイドスペーサを除去した後、P−チャネルトランジスタあるいはN−チャネルトランジスタのゲート電極(72)および歪みソース/ドレイン領域(71)にそれぞれ、高圧縮応力膜(90)あるいは高引っ張り応力膜(120)を適用する。  (もっと読む)

(もっと読む)

バイポーラ・デバイス、トランジスタ・デバイス、ならびにトランジスタおよびバイポーラ相補型金属酸化膜半導体(BiCMOS)デバイスを製造する方法

【課題】

バイポーラ・デバイス、トランジスタ・デバイス、ならびにトランジスタおよびバイポーラ相補型金属酸化膜半導体(BiCMOS)デバイスを製造する方法を提供することを目的とする。

【解決手段】

コレクタ(112)、コレクタの上方の真性ベース(118)、コレクタに隣接するシャロートレンチ分離領域(114)、真性ベースの上方の隆起外部ベース(202)、外部ベースの上方のT字形のエミッタ(800)、エミッタに隣接するスペーサ(700)、および、スペーサによりエミッタから分離されるシリサイド(400)層を有する、バイポーラ相補形金属酸化膜半導体(BiCMOS)またはNPN/PNPデバイスを開示する。

(もっと読む)

パワー半導体装置およびそのための方法

パワー・トランジスタは、複数のトランジスタ・セルを含む。トランジスタ・セルは、それぞれ、第1主表面を覆う第1電極相互接続領域へ結合された第1電極、第1主表面を覆う制御電極相互接続領域へ結合された制御電極、および、第2主表面を覆う第2電極相互接続領域へ結合された第2電極を有する。各トランジスタ・セルは、チャネル領域においてほぼ一定のドーピング濃度を有する。誘電性プラットフォームはエピタキシャル層の終端として使用され、実質的に平坦な等電位線を維持する。パワー・トランジスタは、500メガヘルツを越える周波数で動作し、5ワットを超える電力を放散する無線周波数への応用に特に利用価値がある。パワー・トランジスタがそのような厳しい条件下で効率的に動作することができるように、半導体ダイおよびパッケージが設計される。 (もっと読む)

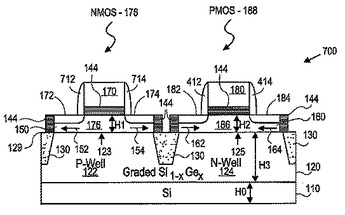

CMOS用歪トランジスタの集積化

【解決手段】CMOSデバイスに関連する本発明の様々な実施形態は、(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

(もっと読む)

パワー半導体デバイスおよびその製造方法

改善されたパワーデバイスに対するさまざまな実施例と同様に、その製造方法,多種多様のパワーエレクトロニックアプリケーションにおける使用に対して、当該パワーデバイスを組み込んだパッケージングおよび回路が開示されている。本発明の1つのアスペクトは、多くの電荷調整法および寄生容量を低減する他の方法を組み合わせることによって、改善された電圧性能,速いスイッチング速度および低いオン抵抗を有するパワーデバイスに対する異なる実施例に至る。本発明の別のアスペクトは、低電圧,中程度の電圧および高電圧のデバイスに対する、改善された終端構造を与える。パワーデバイス製造の改善された方法は、本発明の他のアスペクトによって与えられている。例えば、トレンチの形成,トレンチ内部の誘電体層の形成,メサ構造の形成および基板厚さを低減する工程のような、特定の処理ステップに対する改善が示されている。本発明の他のアスペクトによると、電荷調整パワーデバイスは、例えば同じチップ上のダイオードのような、温度および電流の検出部を組み込んでいる。本発明の他のアスペクトは、パワーデバイスに対する等価直列抵抗(ESR)を改善し、パワーデバイスと同じチップ上にさらなる回路を組み込み、電荷調整パワーデバイスのパッケージングに対する改善を与える。  (もっと読む)

(もっと読む)

電圧発生回路と半導体集積回路装置

第1電流がエミッタに流れるようにされた第1トランジスタと、上記第1トランジスタよりも大きな電流密度となるような第2電流がエミッタに流れるようにされた第2トランジスタとのベース,エミッタ間の電圧差を第1抵抗に流して定電流を形成し、それと直列にして第2抵抗を回路の接地電位側に設け、上記第1トランジスタと第2トランジスタのコレクタと電源電圧との間に第3抵抗と第4抵抗とを設け、上記第1と第2トランジスタの両コレクタ電圧とCMOS構成の差動増幅回路に供給して、出力出力電圧を形成するとともに、かかる出力電圧を上記第1トランジスタと第2トランジスタのベースに共通に供給する。 (もっと読む)

スタック状テンプレート層の局部的なアモルファス化及び再結晶化によって形成される、選択された半導体結晶配向を有するプレーナ型基板

【課題】 異なる配向の半導体が共通のBOX層上に配置された、プレーナ型ハイブリッド配向半導体基板構造体を形成するための、より簡単で優れた方法を提供すること。

【解決手段】 異なる結晶配向の半導体層を有するプレーナ型基板を製造するための、スタック状テンプレート層の局部的なアモルファス化及び再結晶化を用いる方法が提供される。本発明の方法を用いて構築されるハイブリッド配向半導体基板構造体、及び、デバイスの性能を高めるために異なる表面配向上に配置された少なくとも2つの半導体デバイスを含む種々のCMOS回路と一体化されたこうした構造体が提供される。

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

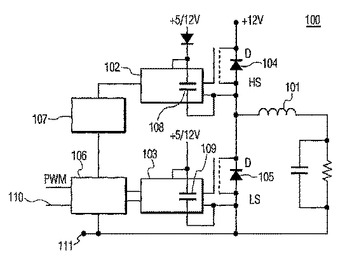

集積VRMパワー電界効果トランジスタ用の集積インタフェース回路構造

ダウンコンバータは、インタフェース部を含み、当該インタフェース部は、当該ダウンコンバータを、複数のスイッチ(104、105)と、それぞれのスイッチのドライバ回路からなる複数のドライバ回路(102、103)とに接続し、前記複数のドライバ回路と前記複数のスイッチとが、集積回路上で組み合わされている。前記複数のドライバ回路は、上側ドライバ回路(102)と下側ドライバ回路(103)とを含む。前記複数のドライバ回路が、前記複数のスイッチと共に集積されることで、寄生インダクタンス、特に電力供給の際の寄生インダクタンスが減少する。  (もっと読む)

(もっと読む)

パンチスルー・ダイオードおよびそれを処理する方法

ショットキーのような動作を有するモノリシック集積パンチスルー・ダイオード。これは、ショットキー金属領域(16)が第1のpドープ・ウェル(9)の表面の少なくとも一部に堆積されるときに実現される。ショットキー金属領域(16)およびpドープ・ウェル(9)は、ショットキー・ダイオードの金属−半導体−遷移を形成する。順方向特性が0.5V未満の電圧降下を有するので、発明のPTダイオードの過電圧保護は改善される。  (もっと読む)

(もっと読む)

パワー半導体装置

【課題】

【解決手段】 ユニットセル部UCPの周囲及びゲートパット部GPPの周囲を第1方向D1乃至第4方向D4に関して完全に取り囲むチップ周辺部CPP内に、ツエナーダイオード11を配設する。ツエナーダイオード11は、各層が第1方向D1乃至第4方向D4に沿って延在した、N+型層1B−P型層33−N+型層32−P型層31−N+型層1Aの構造を有する。

(もっと読む)

401 - 417 / 417

[ Back to top ]