Fターム[5F048BB05]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558)

Fターム[5F048BB05]の下位に属するFターム

N型ドープ多結晶Si (1,205)

P型ドープ多結晶Si (956)

Fターム[5F048BB05]に分類される特許

2,381 - 2,397 / 2,397

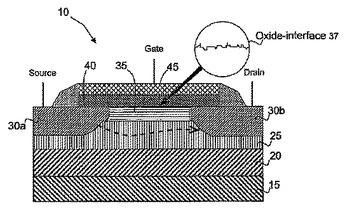

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

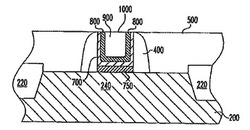

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

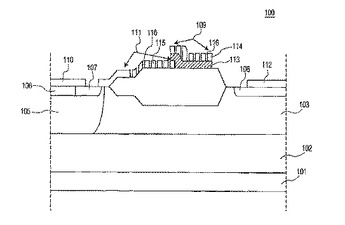

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

非対称の側壁スペーサの形成方法

集積回路半導体デバイスの製造プロセスに統合可能な非対称スペーサの形成方法が提供される。この方法は、基板上にゲート構造(15)を形成するステップと、ゲート構造および基板の上に側壁層(10)を形成するステップとを含み、側壁層は、ゲート構造の第1の側壁の上に第1の部分を含む。第1の部分に隣接して、フォトレジスト構造(11)が形成され、イオンビームにさらされる。フォトレジスト構造は、第1の部分の少なくとも一部をイオンビームから遮蔽するように働く。照射中、ウェハは、イオンビーム(13、17)の経路と、第1の側壁の表面との間に、非直交傾斜角が存在するように配向される。遮蔽されていない側壁部分への放射ダメージにより、その後に続くエッチングがより高速に進むため、非対称スペーサの形成が可能である。  (もっと読む)

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

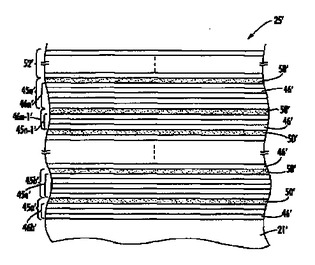

バンド設計超格子を有するMOSFETを有する半導体装置

半導体装置は、基板と、該基板に隣接する少なくとも一つのMOSFETとを有する。MOSFETは、超格子チャンネルを有し、該超格子チャンネルは、複数の積層された層群を有する。またMOSFETは、超格子チャンネルと水平方向に隣接するソースおよびドレイン領域と、超格子上に設置されたゲートと、を有し、超格子チャンネルを通って、積層された層群と平行な方向に電荷キャリアの輸送が生じる。超格子チャンネルの各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取り込まれた、少なくとも一つの非半導体分子層を有し、超格子チャンネルは、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

半導体集積回路

【課題】 本発明の目的は、高速・低消費電力の半導体集積回路を提供することにある。

【解決手段】 動作状態にある回路と待機状態にある回路を混在するようにして、回路毎にバックゲート電圧を設定可能にする。

【効果】 待機時には小電流とし低消費電力性を得て、動作時には大電流として高速性を得ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

パワー半導体装置

【課題】

【解決手段】 ユニットセル部UCPの周囲及びゲートパット部GPPの周囲を第1方向D1乃至第4方向D4に関して完全に取り囲むチップ周辺部CPP内に、ツエナーダイオード11を配設する。ツエナーダイオード11は、各層が第1方向D1乃至第4方向D4に沿って延在した、N+型層1B−P型層33−N+型層32−P型層31−N+型層1Aの構造を有する。

(もっと読む)

SOI基板の作製方法

【課題】 バックゲート電極を有するSOI基板を貼り合わせ法により形成する場合に、段差平坦化用polySi層の形成を不要とし、また、貼り合わせの歩留まりを向上させ、製造コストを低下させる。

【解決手段】基板貼り合わせ法によるSOI基板の作製方法において、第1の半導体基板1に段差を形成し、段差の形成面上に、所定の深さの開孔部8を有する研磨ストッパー用絶縁膜3を形成し、研磨ストッパー用絶縁膜3上にpolySiを堆積して開孔部8にpolySiを充填し、さらにディッシング防止用酸化膜9を形成し、これを平坦化することによりバックゲート電極BGを形成し、この平坦化面上に第2の半導体基板7を貼り合わせ用酸化膜10を介して貼り合わせることにより、バックゲート電極BGを有するSOI基100Aを作製する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の高集積化、高速度化が進んでも、保護回路を構成するトランジスタがその機能を十分果たすことが可能な構造を提供する。

【解決手段】 保護回路が形成された第1導電型ウエル領域5aと、この第1導電型ウエル領域5aに上部は素子分離領域2に隔てられ、素子分離領域2の底面より下では、接合されている高不純物濃度の第2導電型ウエル領域4とを備えている。第1導電型ウエル領域は、素子分離領域を越えて第2導電型ウエル領域に入り込んでいるか素子分離領域の幅の半分より第2導電型領域側に入り込んでいる。過電流は保護回路のトランジスタのソース/ドレイン領域間を流れずに、ドレイン領域から空乏層が延びて第1導電型ウエル領域の第2導電型ウエル領域に入り込んだ部分に接触して、ドレイン領域と第2導電型ウエル領域に入り込んだ部分との間を流れるようになる。

(もっと読む)

半導体装置

【課題】 チップ内に形成されるコンデンサの容量を小さくしてスイッチング速度を向上させた半導体装置を提供する。

【解決手段】 N型半導体基板22上に複数のMOSFET21を形成すると共に、形成されたMOSFET21のポリシリコンゲート電極28をチップ終端部分にまで引き伸ばしてゲート電極引き出し部35を設け、さらに該ゲート電極引き出し部35のポリシリコンゲート電極28の直下にフィールド酸化膜32を設けてなるもので、フィールド酸化膜32が、MOSFET21のゲート酸化膜27より厚い膜厚となっている。

(もっと読む)

エンベディッドアレイを備えた半導体装置及びその製造方法並びに記録媒体

【課題】僅かな開発期間延長で、エンベディッドアレイ中のトランジスタの不要領域を削除することにより消費電力を低減する。

【解決手段】(S1)基本セルが格子状に配列されたエンベッディッドアレイを備えた半導体集積回路を設計して製造し、(S2)製造された半導体集積回路の動作が要求仕様を満たすかどうかを試験し、(S4)該動作が要求仕様を満たす場合に、コンタクトホールのレイアウトデータに基づき基本セルの不使用領域を検出して削除することにより該エンベディッドアレイのレイアウトパターンデータを修正し、(S5)修正されたレイアウトパターンのマスクを作成し、(S6)該マスクを修正前のマスクと置き換えて、不使用領域が削除された半導体集積回路を製造する。

(もっと読む)

2,381 - 2,397 / 2,397

[ Back to top ]