Fターム[5F048BE04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ウェル (5,077) | 同型多ウェル (525)

Fターム[5F048BE04]に分類される特許

121 - 140 / 525

半導体装置およびその製造方法

【課題】MOSトランジスタとバイポーラトランジスタとを同時に形成する構成において、ダイオード電流の特性を安定化させつつ、MOSトランジスタの加工精度を維持する。

【解決手段】半導体装置100は、MOSトランジスタ形成領域(210、220)と、エミッタ取出領域202、ベース取出領域204、およびコレクタ取出領域206を含むバイポーラトランジスタ形成領域200とを含む。各領域は、素子分離絶縁膜110で分離されており、各領域の表面には、シリサイド層124が形成されている。素子分離絶縁膜110は、少なくともエミッタ取出領域202と接する箇所の表面高さがエミッタ取出領域202の基板102の表面高さ以上で、かつ、少なくともエミッタ取出領域202と接する箇所の表面高さがMOSトランジスタ形成領域(210、220)と接する箇所の表面高さよりも高く形成されている。

(もっと読む)

集積回路装置及び電子機器

【課題】アナログ処理の特性の向上を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、信号が入力されるパッドPANTと、パッドPANTを介して入力される信号についてのアナログ処理を行うアナログ回路と、アナログ回路の信号入力ノードとパッドPANTとの間に設けられるキャパシターCAを含む。パッドPANTとキャパシターCAの一端とが、最上層金属層ALEで形成されるパッド配線LNPにより接続される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置

【課題】耐圧を確保すると共に、回路を構成する面積の増大を抑えることのできる半導体装置の静電保護回路を提供する。

【解決手段】静電保護回路は、第1の導電型のウエル64内に形成された第2の導電型の領域であるドレイン68を一部の外部端子に接続され、ゲート74と第1の導電型のウエル64内に形成された第2の導電型の領域であるソース66を共通接続された第1のMOSトランジスタと、第1の導電型のウエル84内に形成された第2の導電型の領域であるドレイン88を第1のMOSトランジスタのゲートとソースに共通接続され、ゲート94と第1の導電型のウエル84内に形成された前記第2の導電型の領域であるソース86を電源端子56に共通接続された第2のMOSトランジスタとを有し、それぞれのMOSトランジスタは、ドレインをコレクタとしウエルをベースとし、ソースをエミッタとする寄生トランジスタを形成する。

(もっと読む)

半導体集積回路

【課題】同一ウェル領域にしきい値の異なる絶縁ゲート電界効果トランジスタが形成された半導体集積回路を提供する。

【解決手段】第1抵抗を有する第1領域14a、14b、14cと第1抵抗より高い第2抵抗を有する第2領域15a、15bとが連接してなる第2導電型のウェル領域13と、第1領域14b、14cに形成された絶縁ゲート電界効果トランジスタ16、17と、を具備する。ウェル領域13の一端からウェル領域13の他端に通電し、電圧降下によりウェル領域13内に電圧分布を生じさせる。

(もっと読む)

半導体装置の製造方法

【課題】高耐圧な半導体装置の製造方法を提供する。

【解決手段】半導体層に対してマスクを用いて選択的にイオン注入を行い、半導体層に第1導電型の第1の半導体領域と、前記第1の半導体領域よりも第1導電型不純物濃度が低い第1導電型の第2の半導体領域とを同時に形成する工程と、第1の半導体領域上に第2導電型のソース領域を形成する工程と、第2の半導体領域上であってソース領域との間にゲート電極を挟む位置に第2導電型のドレイン領域を形成する工程と、半導体層におけるゲート電極とドレイン領域との間の表層部にドレイン領域に接しドレイン領域よりも不純物濃度が低い第2導電型のドリフト領域を形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】n型MISトランジスタを有する半導体装置の特性ばらつきを低減させる。

【解決手段】シリコン基板1上のメモリ領域RMに形成された、n型導電型である第1トランジスタQ1は、ホウ素を含むメモリ用チャネル領域CH1と、メモリ用ゲート電極GE1の両側壁側下に形成された、n型のメモリ用エクステンション領域ET1および酸素を含む拡散防止領域PA1とを有している。ここで、拡散防止領域PA1はメモリ用エクステンション領域ET1を内包するようにして形成されている。また、拡散防止領域PA1は、少なくともその一部が、メモリ用エクステンション領域ET1とメモリ用チャネル領域CH1との間に配置されている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】半導体基板SUBの表面に、ソース領域SOおよびドレイン領域DRを有する高耐圧横型MOSトランジスタが完成される。そのトランジスタを平面視において取り囲む溝DTRが半導体基板SUBの表面に形成される。そのトランジスタ上を覆うように、かつ溝DTR内に中空SPを形成するようにトランジスタ上および溝DTR内に絶縁膜IIAが形成される。層間絶縁膜IIにトランジスタのソース領域SOおよびドレイン領域DRの各々に達するコンタクトホールCHが形成される。

(もっと読む)

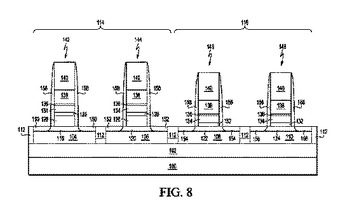

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】

高温、長時間のアニールを必要とすることなく、低いオン抵抗を実現可能な高耐圧MOSトランジスタを含む半導体装置を提供する。

【解決手段】

半導体基板の高耐圧トランジスタ用第1導電型領域上にゲート電極を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第1のマスクをイオン注入マスクとして、ゲート電極を貫通する加速エネルギで第1導電型の不純物イオンを注入して、ソース領域で深く、ゲート電極下方で浅いチャネルドーズ領域を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第2のマスク及びゲート電極をイオン注入マスクとして第2導電型の不純物をイオン注入してソースエクステンション領域を形成し、半導体装置を製造する。

(もっと読む)

半導体集積回路

【課題】ソフトエラー耐性やラッチアップ耐性の更なる向上が求められている。

【解決手段】CMOSレイアウトを有する半導体集積回路を以下のように構成する。その半導体集積回路(1)は、基板(2)と、基板(2)に、第1方向に沿って形成されたNウェル(5)と、基板(2)に、第1方向に沿って形成され、素子分離領域(7)を介してNウェル(5)の隣に形成されたPウェル(6)とを備えていることが好ましい。そして、素子分離領域(7)よりも下の基板(2)に形成され、第1方向と異なる第2方向に沿って形成されたディープNウェル(3)と、第2方向に沿って形成され、ディープNウェル(3)に隣接して形成されたディープPウェル(4)とを具備することが好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置

【課題】寄生容量を増やさずにソフトエラー率を低減することのできる半導体装置を提供する。

【解決手段】半導体基板の主表面に形成された第1導電型ウェルと、第1導電型ウェルの表面に形成されたトランジスタと、半導体基板の主表面に形成された素子分離絶縁領域と、第1導電型ウェルの表面に前記トランジスタと素子分離絶縁領域を隔てて形成され、底面の深さがおおよそ当該素子分離絶縁領域の底面と等しく、第1導電型ウェルより不純物濃度が高い第1導電型高濃度領域と、第1導電型高濃度領域の表面に形成されたウェルコンタクト電極と、を備える。

(もっと読む)

半導体集積回路

【課題】順方向基板バイアス電圧をかけたときの、Vthの異なるトランジスタの速度の向上率をほぼ均等にすることのできる半導体集積回路を提供する。

【解決手段】低VthのPMOSトランジスタが形成されるNウェル領域(WN)11へは、基板バイアス供給部VP1から基板バイアスVbsP1を供給し、高VthのPMOSトランジスタが形成されるNウェル領域(WN)12−1、12−2、12−3へは、基板バイアス供給部VP2から基板バイアスVbsP2を供給する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子の特性や信頼性を向上させることが可能な半導体装置およびその製造方法を提供する。

【解決手段】Hfを含む高誘電率ゲート絶縁膜3上にゲート電極13、14を有する相補型電界効果型トランジスタにおいて、ゲート電極13、14の少なくともゲート絶縁膜3に接する部分は、Ni組成が40%を超えない結晶化したNiシリサイドを主成分とし、pチャネル上のゲート電極14に含まれるNiシリサイドとゲート絶縁膜3との界面にB、Al、Ga、In、Tlの中の少なくともひとつの元素を含み、且つ、nチャネル上のゲート電極13に含まれるNiシリサイドとゲート絶縁膜3との界面にN、P、As、Sb、Biの中の少なくともひとつの元素を含む半導体装置を提供する。

(もっと読む)

半導体装置

【課題】 入出力部の電源配線の近傍にバイパスコンデンサを配置する場合、LSIの端子数が多くなると、バイパスコンデンサを配置するための領域を確保することが困難になる。

【解決手段】 半導体基板の表面に、電子回路素子が形成されている電子回路領域が画定される。半導体基板の上に、一方に基準電位が印加され、他方に電源電圧が印加される第1及び第2の配線が配置される。シールリングが、電子回路領域を取り囲むように、半導体基板の上に配置される。シールリングは、第1の配線に電気的に接続される。第1の不純物拡散領域が、シールリングよりも内側において、半導体基板の表層部に形成される。第1の不純物拡散領域の上に誘電体膜が配置される。誘電体膜の上に、シールリングに電気的に接続され、導電材料で形成されたキャパシタ導電膜が配置される。

(もっと読む)

121 - 140 / 525

[ Back to top ]