Fターム[5F048BG07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面・底面を絶縁物で分離するもの (666) | 複数MOS(CMOS)ですべて (452)

Fターム[5F048BG07]に分類される特許

101 - 120 / 452

半導体装置の作製方法

【課題】TFTを用いた半導体装置において、TFT中の汚染不純物を低減し、信頼性のあるTFTを得ることを課題とする。

【解決手段】ガラス基板上のTFTの被膜に存在する汚染不純物を、フッ素を含有する酸性溶液を被膜表面に接触させ、酸性溶液を一定方向に流すことにより、被膜表面の汚染不純物を除去することにより、信頼性のあるTFTを得ることができる。なお、酸性溶液は、フッ酸とフッ化アンモニウムの混合比が体積比で1:50のバッファードフッ酸を用いる。

(もっと読む)

半導体装置の作製方法

【課題】大面積な半導体装置を低コストに提供することを目的の一とする。または、nチャネル型トランジスタ及びpチャネル型トランジスタに最適な結晶面をチャネル形成領域とすることにより、性能向上を図ることを目的の一とする。

【解決手段】絶縁表面上に(211)面から±10°以内の面を上面とする島状の単結晶半導体層を形成し、単結晶半導体層の上面及び側面に接して形成し、且つ絶縁表面上に非単結晶半導体層を形成し、非単結晶半導体層にレーザー光を照射して非単結晶半導体層を溶融し、且つ、単結晶半導体層を種結晶として絶縁表面上に形成された非単結晶半導体層を結晶化して結晶性半導体層を形成し、結晶性半導体層を用いて、nチャネル型トランジスタ及びpチャネル型トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置が有する集積回路の多機能化を図ること、又は、炭化シリコン基板を用いて集積回路を形成する場合であっても集積回路の大面積化を図ることを目的とする。

【解決手段】基板上に第1の絶縁層を介して設けられた島状の炭化シリコン層と、炭化シリコン層上に設けられた第1のゲート絶縁層と、第1のゲート絶縁層上に設けられ且つ炭化シリコン層と重畳する第1の導電層とを有する第1のトランジスタと、基板上に第2の絶縁層を介して設けられた島状の単結晶シリコン層と、単結晶シリコン層上に設けられた第2のゲート絶縁層と、第2のゲート絶縁層上に設けられ且つ単結晶シリコン層と重畳する第2の導電層とを有する第2のトランジスタを設ける。

(もっと読む)

薄膜トランジスタ及び表示装置の作製方法

【課題】マスク数の少ない薄膜トランジスタの作製方法を提供する。

【解決手段】第1の導電膜102と、絶縁膜104と、半導体膜106と、不純物半導体膜108と、第2の導電膜110とを積層し、この上に多階調マスクを用いて凹部を有するレジストマスク112を形成し、第1のエッチングを行って薄膜積層体を形成し、第1の導電膜102がエッチングされた膜113に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層116Aを形成し、その後ソース電極及びドレイン電極等を形成することで、薄膜トランジスタを作製する。半導体膜としては結晶性半導体膜106を用いる。

(もっと読む)

半導体装置

【課題】柱状半導体層の周囲にゲート電極が形成される縦型トランジスタにおいては、各々の縦型トランジスタのゲート長より大きいゲート長を持つトランジスタを形成することが困難である。

【解決手段】基板上に形成された第1の拡散層上に2個の柱状半導体層によって形成された縦型トランジスタが隣接して形成されており、それらの縦型トランジスタは共通なゲート電極を備え、第1の柱状半導体層の上部に形成された第1の上部拡散層はソース電極に接続され、第2の柱状半導体層の上部に形成された第2の上部拡散層はドレイン電極に接続され、2個の縦型トランジスタが直列に接続されることによって、各々の縦型トランジスタの2倍のゲート長を持つトランジスタとして機能することを特徴とする半導体装置を提供する。

(もっと読む)

半導体構造体およびその製造方法(移動度が最適化された方位を有する半導体ナノワイヤ)

【課題】高いオン電流、低いオフ電流を与えるp型半導体ナノワイヤ・デバイス、n型半導体ナノワイヤ・デバイスを提供する。

【解決手段】各々が半導体リンク部30C,50Cと2つの隣接するパット部30A,30B,50A,50Bを含む半導体構造体で、半導体リンク部の側壁は、第1の半導体構造体の場合には正孔の移動度を最大化するように、第2の半導体構造体の場合には電子の移動度を最大化するように方位を定める。半導体構造体の酸化による薄化で、半導体リンク部の幅は、異なる結晶方位ごとに異なる速度で小さくされる。異なる量の薄化の結果、薄化後に得られる半導体ナノワイヤが目標とするサブリソグラフィ寸法となるように、予め決定される。異なる結晶面に対する異なる薄化速度を補償することによって、過剰な薄化又は不十分な薄化がなされることなく、最適なサブリソグラフィ幅を有する半導体ナノワイヤを形成する。

(もっと読む)

高耐圧半導体装置および高電圧集積回路装置

【目的】ワイヤ接続における高耐圧半導体装置において、複雑なプロセス製造工程も、複雑な裏面加工工程も一切伴わず、低コストで高耐圧化、高信頼性化を実現できる高耐圧半導体装置およびそれを用いた高電圧集積回路装置を提供することにある。

【構成】半導体基板100上に誘電体層101を介して半導体層102が形成され、半導体層102上にドレイン層113と、ドレイン層113を内包するように形成されたバッファ層112と、ドレイン層113と離間し、その周りを囲むように形成されたソース層114と、ソース層114を内包するように形成されたウエル層111と、半導体層102上にゲート絶縁膜を介して形成されたゲート電極110と、を備えた高耐圧半導体装置において、ドレイン層113及び、バッファ層112の平面形状が非連続または連続の環状とする。

(もっと読む)

半導体装置

【課題】SOI構造の半導体デバイスにおいて、SOI層の端部に発生する応力の影響がチャネル領域に及ぶことにより、N型トランジスタとP型トランジスタとの間でトランジスタ特性に偏りが生じることを改善し、一定のトランジスタ特性を有するSOI構造の半導体装置を提供する。

【解決手段】BOX層20の表面に形成された素子分離酸化膜により、互いに分離されているN型トランジスタNchおよびP型トランジスタPchにおいて。N型トランジスタNchのゲート電極40nの形成位置からP型半導体領域であるSOI層30nの端部までの距離が、P型トランジスタPchのゲート電極40pの形成位置からN型半導体領域であるSOI層30pの端部までの距離よりも大きい。

(もっと読む)

半導体素子およびその製造方法

【課題】チャンネル長および延長ソース/ドレイン領域のドーピング条件によって閾値電圧を調製できる半導体素子の提供。

【解決手段】SOI構造の半導体層の上に形成された高Vt素子と、前記半導体層の上に形成され、高Vt素子よりも低い閾値電圧を有する低Vt素子とを有し、高Vt素子と低Vt素子とはMOSFET素子であって、延長ソース領域と延長ドレイン領域との間の部分であるチャンネルを有し、高Vt素子は低Vt素子よりもチャンネル長が長いSOI構造の半導体素子。

(もっと読む)

半導体装置

【課題】電流特性の低下を防ぐ半導体装置を提供する。

【解決手段】nチャネル型の横型IGBT10では、N-エピタキシャル層4とはpベース11を介在させて隔てられているP+拡散層12と、エミッタ領域としてのN+拡散層13とには、金属シリサイド層9aが形成されている。一方、N-エピタキシャル層4との接合面がpn接合面となるコレクタ領域としてのP+拡散層14には、金属シリサイド層は形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置及びその製造方法を提供する。

【解決手段】BOX層1上のSOI層2に形成された部分空乏型のトランジスター10と、ダイオード20とを備え、トランジスター10は、SOI層2上に絶縁膜13を介して形成されたゲート電極14と、ゲート電極14の両側下のSOI層2に形成されたN型のソース15a又はドレイン15bとを有し、ダイオード20は、SOI層2の浅い部分に形成されたP型不純物層21と、SOI層2の深い部分に形成されたN型不純物層22と、を有する。P型不純物層21と、N型不純物層22は深さ方向に積層されており、P型不純物層21の側面とN型不純物層22の側面はそれぞれトランジスター10のボディ領域2に接している。

(もっと読む)

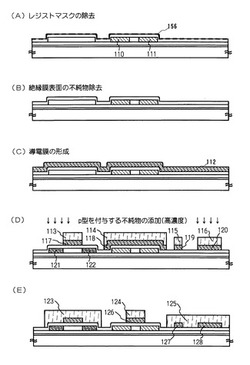

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】微結晶シリコンをチャンネル領域として用い、良好にリーク電流を抑制することが可能な薄膜トランジスタ及びその製造方法を提供する。

【解決手段】薄膜トランジスタ100は、図1に示すように、基板11と、ゲート電極112と、ゲート絶縁膜113と、半導体層(チャンネル領域)114と、エッチングストッパ膜115と、高濃度不純物含有アモルファスシリコン層116,117と、ドレイン電極118と、ソース電極119と、低濃度不純物含有半導体層120,121を備える。微結晶シリコンを用いたチャンネル領域114と、高濃度不純物含有アモルファスシリコン層116及び/又は高濃度不純物含有アモルファスシリコン層117との間に低不純物濃度半導体層120,121を設けることにより、良好にリーク電流を抑制することができる。

(もっと読む)

半導体表示装置の作製方法

【課題】高精彩・高解像度・高画質・低消費電力の小型半導体表示装置を提供すること。

【解決手段】本発明の半導体表示装置は、画素マトリクス回路、データ線駆動回路、および走査線駆動回路を有しており、これらの構成要素が多結晶TFTによって同一基板上に形成される。また、その製造方法における、触媒元素を用いた結晶性の助長化プロセス、および触媒元素のゲッタリングプロセスによって、小型にもかかわらず、高精細・高解像度・高画質の半導体表示装置が提供される。

(もっと読む)

保護回路、半導体装置、光電変換装置および電子機器

【課題】ESD対策をした保護回路および半導体装置を提供する。

【解決手段】集積回路と電気的に接続された信号線と、信号線と第1の電源線との間に設けられた第1のダイオード、及び第1のダイオードと並列に設けられた第2のダイオードと、第1の電源線と第2の電源線との間に設けられた第3のダイオードとを有し、第1のダイオードは、トランジスタをダイオード接続することによって形成されたダイオードであり、第2のダイオードはPIN接合又はPN接合を有するダイオードである保護回路。上記保護回路は、特に薄膜トランジスタを用いて作製される半導体装置に用いられることで効果を発揮する。

(もっと読む)

半導体装置の製造方法

【目的】層間絶縁膜内の電荷による電界への影響を緩和して、素子のリーク電流の減少と耐圧の向上を図ることができる半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜をSiH4とN2Oから形成される堆積酸化膜2aとTEOSとO2から形成されるTEOS酸化膜2bとの二層の複合膜とすることで、TEOS酸化膜2b中の電荷5による電界への影響を堆積酸化膜2aで緩和できて、素子のリーク電流が低減され、耐圧が向上する。その結果、良品率を向上させることができる。

(もっと読む)

半導体装置

【課題】回路動作の安定性を高め、消費電力の低減を可能とした半導体装置を提供する。

【解決手段】フローティングボディ型のPD−SOI−MOSFET21〜26を有する分周回路を備え、この分周回路の動作時は、MOSFET22、23,24、26の各ゲート(G)に固定電圧が印加されてMOSFET22、24がオンすると共に、MOSFET23、26がオフする。また、MOSFET21、25の各ゲート(G)に振幅電圧が印加されて、MOSFET21、25がオン、オフを繰り返す。このように動作する分周回路において、MOSFET23、26の閾値電圧の絶対値は、例えばチャネルドープにより、MOSFET21、25の閾値電圧の絶対値よりも大きく設定されている。

(もっと読む)

集積回路のためのオンチップ電圧変換装置およびシステム

【課題】 多数の電圧ドメインを有する集積回路デバイスおよびシステムのための改良された電圧変換システムを提供する。

【解決手段】 集積回路のためのオンチップ電圧変換装置は、第1のキャパシタと、この第1のキャパシタの第1の電極を第1の電圧ドメインの低側電圧レールに選択的に結合するように構成された第1のNFETデバイスと、第1のキャパシタの第1の電極を第1の電圧ドメインの高側電圧レールに選択的に結合するように構成された第1のPFETデバイスと、第1のキャパシタの第2の電極を第2の電圧ドメインの低側電圧レールに選択的に結合するように構成された第2のNFETデバイスであって、第2の電圧ドメインの低側電圧レールが第1の電圧ドメインの高側電圧レールに対応する、第2のNFETデバイスと、第1のキャパシタの第2の電極を第2の電圧ドメインの高側電圧レールに選択的に結合するように構成された第2のPFETデバイスと、を含む。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる単結晶半導体層を備えた半導体基板の製造方法を提供する。

【解決手段】単結晶半導体基板上に酸化膜を形成し、酸化膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板中に脆化領域を形成し、酸化膜を間に挟んで単結晶半導体基板と向かい合うように支持基板を貼り合わせ、単結晶半導体基板を加熱することにより、脆化領域において、単結晶半導体層が貼り合わされた支持基板と単結晶半導体基板の一部とに分離し、支持基板に貼り合わされた単結晶半導体層の表面に対して、基板バイアスを印加して第1のエッチングを行い、単結晶半導体層に対してレーザビームを照射して、単結晶半導体層の少なくとも表面の一部を溶融した後、凝固させ、単結晶半導体層の表面に対して、基板バイアスを印加することなく第2のエッチングを行う。

(もっと読む)

半導体およびその製造方法

【課題】SOI構造を有するCMOSトランジスタにおいて、CMOSトランジスタのチャネル領域に応力を印加する構造の製造方法の提供。

【解決手段】単結晶のシリコン基板11の表面に素子分離領域13Iにより画成されたnチャネルMOSトランジスタ10Aが形成された第1の素子領域13AとpチャネルMOSトランジスタ10Bが形成された第2の素子領域13Bとを含む単結晶シリコンの活性層13を形成し、シリコン基板と活性層との間に形成されたシリコン酸化膜を有し、シリコン酸化膜は第1の素子領域の下および第2の素子領域の下に連続して延在し、nチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最大の膜厚を有し、ゲート長方向に向かって膜厚を減少させ、pチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最小またはゼロの膜厚を有し、チャネル領域から、ゲート長方向に向かって膜厚を増大させることを特徴とする。

(もっと読む)

半導体回路

【課題】耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】複数のpMOSトランジスタ11を直列又は一のpMOSトランジスタ12を備えた並列回路に接続した第1の回路ブロック1と、複数のnMOSトランジスタ21を直列又は一のnMOSトランジスタ22を備えた並列回路に接続した第2の回路ブロック2とを備え、前記第1の回路ブロック1と前記第2の回路ブロック2との接続点Sを出力端子Voutに接続するとともに、全ての前記pMOSトランジスタ11,12のゲート及び全ての前記nMOSトランジスタ21,22のゲートを共通の入力端子Vinに接続する半導体回路。

(もっと読む)

101 - 120 / 452

[ Back to top ]