Fターム[5F048BG07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 絶縁体分離 (5,896) | 素子領域側面・底面を絶縁物で分離するもの (666) | 複数MOS(CMOS)ですべて (452)

Fターム[5F048BG07]に分類される特許

81 - 100 / 452

半導体装置

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲む第1のゲート電極と、第1のゲート電極の周囲を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲を取り囲む第1の筒状半導体層と、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第1の筒状半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第1の筒状半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有するインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積なSGTを用いたCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のトランジスタは、島状半導体層と、島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲むゲート電極と、島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、島状半導体層の下部に配置された第2の第1導電型高濃度半導体層とを有し、第2のトランジスタは、ゲート電極の周囲の一部を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲の一部に接する第2の半導体層と、第2の半導体層の上部に配置され、第1導電型高濃度半導体層と反対の極性を有する第1の第2導電型高濃度半導体層と、第2の半導体層の下部に配置され、第1導電型高濃度半導体層と反対の極性を有する第2の第2導電型高濃度半導体層とを有することにより、上記課題を解決する。

(もっと読む)

半導体装置

【課題】接続配線に起因する耐圧低下を抑制する。

【解決手段】半導体装置は、第1素子領域16に配置されたLIGBTと、第2素子領域18に配置されたFWDを備えている。第1素子領域16と第2素子領域18は、SOI基板20を平面視したときに、隣接部11においてy軸方向に沿って並んでいる。LIGBTは、SOI基板20を平面視したときに、隣接部11においてコレクタ電極42とエミッタ電極48がx軸方向に間隔を置いて配置されている。FWDは、SOI基板20を平面視したときに、隣接部11においてカソード電極142とアノード電極148がx軸方向に間隔を置いて配置されている。LIGBTのコレクタ電極42とFWDのカソード電極142が接しており、LIGBTのエミッタ電極48とFWDのアノード電極148が接している。

(もっと読む)

半導体装置

【課題】高耐圧の半導体装置であって、パルス的に変化する高基準電位のOFF直後においてもデッドタイムが発生しない、安価な半導体装置を提供する。

【解決手段】n個(n≧2)のMOSトランジスタ素子Tr1〜Tr12が、GND側を第1段、電源側を第n段として、順次直列接続されてなり、第1段を除いた各段のMOSトランジスタ素子Tr2〜Tr12におけるゲート端子が、直列接続された各段の抵抗素子R1〜R12の間に、それぞれ、順次接続されてなり、第1段を除いた少なくとも中央より低段のMOSトランジスタ素子Tr2〜Tr6におけるゲート端子が、直列接続された各段の容量素子C1〜C12の間に、容量素子側をアノードとしゲート端子側をカソードとしたダイオード素子A2〜A6を介して、それぞれ、順次接続されてなる半導体装置22とする。

(もっと読む)

トランジスタ回路

【課題】 高耐圧の薄膜トランジスタと高電流駆動能力を持った薄膜トランジスタを同一基板上に形成する。

【解決手段】 絶縁性基板上に形成され、半導体層、ソース領域、ドレイン領域で構成される薄膜トランジスタを備えるトランジスタ回路において、半導体層の下側に第1の絶縁層を介してボトムゲート層があり、半導体層を挟んでボトムゲート層と対向する側に第2の絶縁層を介してトップゲート層を具備した少なくとも一つの第1の薄膜トランジスタと、半導体層の下側に第1の絶縁層を介してボトムゲート層のみを具備する少なくとも一つの第2の薄膜トランジスタと、を同一基板上に形成したことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

トランジスタ基板及び発光装置

【課題】トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、スイッチトランジスタ5のチャネル長より、駆動トランジスタ6のチャネル長を長くするように、チャネル保護膜6dのチャネル長方向の長さを18[μm]以上に形成することによって、駆動トランジスタ6のオン電流を安定させる。駆動トランジスタ6のチャネル長を長くすることによって、駆動トランジスタ6がEL素子8に向けて安定した電流を流すことが可能になって、EL素子8を所望するレベルで発光させることができ、ELパネル1における画素Pごとに、薄膜トランジスタの製造時のアライメントずれに起因するEL素子8の発光レベルの差が無くなるので、ELパネル1の画質低下を抑えることができる。

(もっと読む)

半導体装置、半導体基板、及び半導体基板の処理方法

【課題】表面が(111)面以外であるシリコン層と、表面が(0001)面である窒化物半導体層とを基板に設け、かつシリコンと窒化物半導体の線膨張係数の違いに起因した応力を小さくする。

【解決手段】まずSOI(Silicon On Insulator)基板を準備する。SOI基板は、表面が(111)面であるシリコン基板100上に絶縁層120及びシリコン層200を積層した基板である。シリコン層200は、表面が(111)面以外の面方位である。次いで、絶縁層120及びシリコン層200に、底面にシリコン基板100が露出している開口部201を形成する。次いで、開口部201内にIII族の窒化物半導体層300を形成する。

(もっと読む)

半導体装置

【課題】画素TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現し、信頼性と生産性を向上させる技術を提供することを課題とする。

【解決手段】画素領域に形成する画素TFTをチャネルエッチ型の逆スタガ型TFTで基板上に形成し、ソース領域及びドレイン領域のパターニングと画素電極のパターニングを同じフォトマスクで行う。また、ソース配線を画素電極と同じ材料である導電膜で覆い、基板全体を外部の静電気等から保護する構造とする。このような構成とすることで、製造工程において製造装置と絶縁体基板との摩擦による静電気の発生を防止することができる。特に、製造工程で行われる液晶配向処理のラビング時に発生する静電気からTFT等を保護することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体集積回路

【課題】サブスレッショルドリーク電流が増大するという問題を回避しつつ、動作時における消費電力を極力低減し得る半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のFF103、組み合わせ回路104及びメインFF105と、メインFF105と並列に設けられる第1の遅延素子107及び第1のカナリアFF108と、メインFF105と並列に設けられる第2の遅延素子111及び第2のカナリアFF112と、メインFF105の出力と第1のカナリアFF108の出力とを比較する第1の比較回路109と、メインFF105の出力と第2のカナリアFF112の出力とを比較する第2の比較回路113と、第1の比較回路109の出力及び第2の比較回路113の出力に応じて、組み合わせ回路104のトランジスタの閾値電圧を制御する制御回路120とを備える。

(もっと読む)

半導体装置及びその製造方法

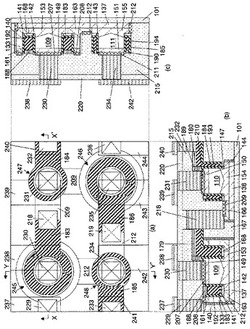

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

静電保護回路及び半導体回路

【課題】薄膜トランジスターで回路構成した場合であっても安定した動作をする集積回路を提供する。

【解決手段】高電位源と低電位源との間に設けられた静電保護回路はP型トランジスターとN型トランジスターとが直列接続しており、P型トランジスターのソースとゲートが高電位源に接続し、N型トランジスターのソースとゲートが低電位源に接続し、P型トランジスターのドレインとN型トランジスターのドレインとが接続している。

(もっと読む)

半導体装置及び電子機器

【課題】回路面積が小さい、またはトランジスタの劣化を防止するよう形成された、有機トランジスタと無機トランジスタとを備えた半導体装置を提供する。

【解決手段】本発明の一形態の半導体装置としてのCMOS回路は、(a)基板100と、(b)有機半導体層106aを含むp型有機トランジスタPTと、(c)p型有機トランジスタPTの上層に設けられた無機半導体層126aを含むn型無機トランジスタNTと、を備える。さらに、n型無機トランジスタNTのチャネル領域126は、p型有機トランジスタPTのチャネル領域106と、平面視において少なくとも部分的に重なっている。

(もっと読む)

SOI基板の作製方法

【課題】単結晶シリコン基板よりも大面積な基板に、均一な質を有する複数の単結晶半導体層を貼り付けたSOI基板の作製方法を提供することを課題とする。

【解決手段】熱処理において、ベース基板支持及び単結晶半導体基板保持のトレイとして、凹部の底が深く、ベース基板に貼り付けられた単結晶半導体基板と接触しないトレイを用いて、単結晶半導体基板の熱分布の均一化を図る。また、該トレイの各々の凹部の間にベース基板支持部を設けることによって、該トレイとベース基板との接触面積を低減する。以上より、単結晶半導体基板から単結晶半導体層を分離する熱処理の際、単結晶半導体基板及びベース基板の熱分布が均一になるようにする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に、酸化物半導体層より導電率の高いバッファ層を形成し、該バッファ層の上にソース電極層及びドレイン電極層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置

【課題】しきい値電圧の制御にチャネルドープ法を用いて行う場合、活性層に不純物を導入するため、必然的にこの不純物起因のバルク結晶欠陥や、半導体層と絶縁層の界面凖位を生じさせてしまう。この結果、TFT特性、特に電界効果型移動度を悪化させる原因となる。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

SOI基板の作製方法およびSOI基板

【課題】ガラス基板と単結晶半導体基板とを貼り合わせてSOI基板を作製する際のシリコン層の表面の荒れを抑制することを目的の一とする。または、上記荒れを抑えて歩留まりの高い半導体装置を提供することを目的の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせると共に、ボンド基板とベース基板の一部に貼り合わない領域を形成し、熱処理を施すことにより、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成する。

(もっと読む)

誘電体分離型半導体集積装置、及び半導体集積装置の製造方法

【課題】微細なMOS素子と共存する。

【解決手段】支持基板5と、埋込シリコン酸化膜6と、第1高濃度不純物層9及び低不純物濃度層とからなる活性層15、とで構成されるSOI基板を適用した誘電体分離型半導体集積装置10において、高耐圧半導体素子形成領域を囲んで形成される素子分離領域は、多重溝100と、多重溝の側壁に設けた第1酸化膜105と、第1酸化膜と隣接して多重溝側壁に沿って形成された第2高濃度不純物層110と、第2高濃度不純物層の略上部にLOCOS酸化膜50を介して配設された低抵抗層P2と、前記低抵抗層に積層された第2酸化膜70,75,80と、を備えて構成され、低抵抗層は、第2高濃度不純物層、あるいはドレイン電極と略同電位であり、第2酸化膜の表面でエミッタ電極が前記高耐圧半導体素子形成領域から隣接領域へ引き出されている。

(もっと読む)

81 - 100 / 452

[ Back to top ]