Fターム[5F049MA04]の内容

受光素子−フォトダイオード・Tr (21,418) | 素子の種類 (2,342) | フォトダイオード(PD) (2,089) | PIN接合型 (513)

Fターム[5F049MA04]に分類される特許

121 - 140 / 513

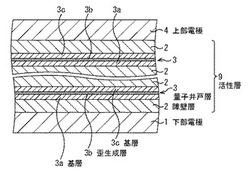

光検知器及びその製造方法

【課題】高い感度を得ることができる光検知器及びその製造方法を提供する。

【解決手段】下部電極1と、下部電極1上方に形成された活性層9と、活性層9上方に形成された上部電極4と、が設けられている。活性層9には、障壁層2と、障壁層2と格子整合する量子井戸層3と、が設けられている。障壁層2及び量子井戸層3は、タイプII型の超格子を構成している。量子井戸層3には、第1の化合物半導体層3a及び3cと、第1の化合物半導体層3a及び3cの結晶に格子歪を生じさせる第2の化合物半導体層3bと、が設けられている。

(もっと読む)

半導体装置およびその作製方法

【課題】特性の良い光電変換素子を有する半導体装置を提供することを目的の一とする。または、簡単な工程で、特性の良い光センサ光電変換装置を有する半導体装置を提供することを目的の一とする。

【解決手段】光透過性を有する基板と、光透過性を有する基板上の絶縁層と、絶縁層上の、光電変換を奏する半導体領域、第1の導電型を示す半導体領域、および、第2の導電型を示す半導体領域を有する単結晶半導体層と、第1の導電型を示す半導体領域と電気的に接続された第1の電極と、第2の導電型を示す半導体領域と電気的に接続された第2の電極とを有する光電変換素子とを備える半導体装置を提供する。

(もっと読む)

光センサ

【課題】光を最大に効率良く利用し、高いS/N比を有した超小型で、赤外線領域の赤外線を電圧信号に変換するのに適した光センサを提供すること。

【解決手段】光センサは、半導体基板1の表面に設けられた少なくとも第1の半導体層2と、この第1の半導体層2上に設けられた光吸収層となる第3の半導体層4と、この第3の半導体層4上に設けられた第2の半導体層3と、半導体基板1の裏面に設けられた保護層5とから構成されている。半導体基板の裏面から入射した光量に応じた信号を電圧又は電流で出力し、半導体基板の裏面が粗面であり、さらに半導体基板の裏面に保護層を設けることで、半導体基板の裏面の変色を防ぎ、また、光の利用効率を向上することが出来る。

(もっと読む)

光検出装置、液晶表示装置及び発光装置

【課題】バックライトからのフォトダイオードへの光の入射を防止し、検出物からの斜光が所望のフォトダイオードではなく、別のフォトダイオードに入射されるのを防止する。

【解決手段】透光性基板上の第1の遮光層と、第2の遮光層と、第1の遮光層上の第1のフォトダイオードと、第2の遮光層上の第2のフォトダイオードと、第1のフォトダイオードを覆う第1のカラーフィルターと、第2のフォトダイオードを覆う第2のカラーフィルターと、を有し、第1のフォトダイオードと第2のフォトダイオードとの間には、第1のカラーフィルター及び第2のカラーフィルターからなる第3の遮光層を有する。

(もっと読む)

反射防止イメージセンサ

【課題】本発明は反射防止膜を有するイメージセンサおよびその製造方法を提供する。

【解決手段】反射防止イメージセンサは、基板と、前記基板内に配置された第1カラーセンシングピクセルと、前記基板内に配置された第2カラーセンシングピクセルと、前記基板内に配置された第3カラーセンシングピクセルと、前記第1、第2および第3カラーセンシングピクセル上に直接配置された第1層と、前記第1、第2および第3カラーセンシングピクセル上に置かれ、前記第1層上に直接配置された第2層と、前記第1カラーセンシングピクセルまたは第2カラーセンシングピクセルの少なくとも一つの上に置かれ、前記第2層の一部上に直接配置された第3層とを含み、前記第1層は第1屈折率を有し、前記第2層は前記第1屈折率より大きい第2屈折率を有し、前記第3層は前記第2屈折率より大きい第3屈折率を有する。

(もっと読む)

半導体素子の製造方法

【課題】III−V族半導体から成る暗電流の低減された半導体素子の製造方法を提供すること。

【解決手段】III−V族半導体からなる基板3a上にSb元素を含むIII−V族半導体からなる第1の半導体層2aを形成する工程と、第1の半導体層2aを形成した後に、III−V族半導体からなる第2の半導体層10aを第1の半導体層2a上に形成する工程とを備え、第1の半導体層2aを形成する工程は、第1の半導体層2aに含まれており基板3aとの界面から所定の厚みを有する第1の層の形成を第1の温度のもとで行った後に、第1の半導体層2aのうち第1の層を除いた第2の層の形成を第1の温度よりも高い第2の温度のもとで行い、第2の半導体層10aを形成する工程は、第2の半導体層10aに含まれており第1の半導体層2aとの界面から所定の厚みを有する第3の層の形成を第2の温度のもとで行う。

(もっと読む)

III−V族化合物半導体受光素子、及びIII−V族化合物半導体受光素子を作製する方法

【課題】V族構成元素としてSbを含むIII−V化合物半導体層を有する受光層とn型InP窓層とを有しており暗電流を低減可能なIII−V族化合物半導体受光素子を提供する。

【解決手段】受光層21のGaAsSb層の成長の際に供給されたアンチモンのメモリ効果により、受光層23上に成長されるInP層23に、不純物としてアンチモンが含まれる。III−V族化合物半導体受光素子11では、InP層23は不純物としてアンチモンを含むと共に、InP層23にはn型ドーパントとしてシリコンが添加されている。InP層23中のアンチモン不純物は正孔を生成するように作用するけれども、この生成キャリアをInP層23中に添加されたシリコンが補償して、InP層23の第2の部分23dは十分なn導電性を示す。

(もっと読む)

半導体素子およびその製造方法

【課題】 多くのペア数を有する多重量子井戸構造を、良好な結晶品質を確保しながら能率よく成長することができる、半導体素子の製造方法および当該半導体素子を得る。

【解決手段】 本発明の半導体素子の製造方法は、III−V族化合物半導体の量子井戸を50ペア以上有する多重量子井戸構造3を形成する工程を備え、その多重量子井戸構造3の形成工程では、全有機金属気相成長法(全有機MOVPE法)により、多重量子井戸構造を形成することを特徴とする。

(もっと読む)

光検出回路及びその駆動方法、並びにこれを備えたタッチスクリーンパネル

【課題】光検出回路を実現するにあたり、電源線及び信号線の数を最小化して受光素子の受光領域を最大化することにより、光の変化程度をより正確に検出できるようにする光検出回路及びその駆動方法を提供する。

【解決手段】第1電源に接続された受光素子と、上記受光素子と第2電源との間に接続されたキャパシタと、ゲート電極が上記キャパシタの第1電極に接続され、第1電極が選択信号線に接続された第1トランジスタと、ゲート電極が上記選択信号線に接続され、第1電極が上記第1トランジスタの第2電極に接続され、第2電極が出力信号線に接続された第2トランジスタと、ゲート電極が初期化電源に接続され、上記第2電源と上記出力信号線との間に接続された第3トランジスタと、を備える。

(もっと読む)

化合物半導体膜の製造方法、化合物半導体膜及び半導体デバイス

【課題】化合物半導体結晶中への亜鉛の取り込み量を増やすことができる化合物半導体膜の製造方法、化合物半導体膜及び当該化合物半導体膜を用いた半導体デバイスを提供することを目的とする。

【解決手段】亜鉛をドープするp型化合物半導体膜のエピタキシャル成長時に、亜鉛含有原料(例えば、ジエチル亜鉛;DEZn)と共に所定範囲の供給量のSb含有原料(例えば、トリスジメチルアミノアンチモン;TDMASb)を供給することにより、化合物半導体膜(例えば、InGaAs膜)中への亜鉛の取り込み量を増やす。

(もっと読む)

メサ型フォトダイオード及びその製造方法

【課題】メサ型フォトダイオードの安定なデバイス特性及び長期信頼性を得る。

【解決手段】メサ(受光領域メサ19)の側面23と、メサの上面24における少なくとも当該メサの肩の部分(肩部25)とは、それらの上に成長された第1導電型、第2導電型、半絶縁型、ないしノンドープの半導体層(例えば、ノンドープInP層17)により連続的に被覆されている。半導体層においてメサの側面23を覆う部分の層厚D1が850nm以上である。

(もっと読む)

半導体受光素子

【課題】優れた信頼性を具備し、かつ簡易に製造できる半導体受光素子を提供すること。

【解決手段】本発明は、n型の半導体基板201上に、半導体メサ120と、少なくとも半導体メサ120の側壁を覆う半導体層107aが少なくとも形成されている。半導体メサ120は、光吸収層104と、p型のコンタクト層106を少なくとも有する。半導体基板101の主面は、<01−1>方向を軸として、(100)面に対して回転角θだけ回転した結晶面であり、その回転角θは0.1°≦|θ|≦10°である。

(もっと読む)

光電変換装置の製造方法

【課題】高い均一性を備える銀薄膜を熱処理により凝集させて凸凹を形成する場合、温度や表面状態により、一箇所に凝集し、銀薄膜が無くなってしまう領域と、銀が「だま」状に集中してしまう場所ができてしまう場合がある。この場合、本来の目的である乱反射領域にはならず、不良品となる課題がある。

【解決手段】多結晶ITO層20aを積層し、フォトリソグラフ工程によりレジストマスクを形成した後、多結晶ITO層20aを例えば塩酸系のエッチング液を用いてエッチングする。ここで、レジストマスクに覆われた部分は配線層として機能する。この場合粒界から選択的にエッチングが進行し、特定の面方位のグレインが残り、エッチングマスクとして機能する残渣20bが形成される。この残渣20bをマスクとして第2層間絶縁層19をドライエッチングすることでテクスチャー構造を得ることができる。

(もっと読む)

pinダイオードを備えた集積回路構造の製造方法

【課題】簡単に設計された、感度の高い、無線周波数の使用に適した、pinダイオード、を備えた集積回路構造を提供する。

【解決手段】集積回路構造において、保護される材料82が隣接している少なくとも1つの段を含んだ形状を形成し、段をも覆う保護層を形成し、上記保護層を形成した後、スペーサ素子層を形成し、スペーサ素子層に異方性エッチングを行い、段に少なくとも1つのスペーサ素子を形成し、スペーサ素子によって覆われていない領域において、保護層を薄膜化するか、または、完全に除去し、上記保護される材料82に沿って、保護層の少なくとも1つの残余領域150が残っており、保護層を薄膜化または除去した後、有効層を形成し、有効層をパターン形成すると同時に、スペーサ素子を除去して、保護される材料82を、残余領域150によって保護する。

(もっと読む)

光学素子とこれを用いた光子発生装置、光発生装置、光記録装置および光検出装置

【課題】高い励起効率と光子取り出し効率の両方を兼ね備え、バックグラウンド雑音が少ない単一光子発生装置を提供する。

【解決手段】量子ドット4が上部半導体層2と下部半導体層3の間に埋め込まれ、その上部の金属遮光膜5に、開口から金属突起11〜14が張り出した構造を持つ突起付開口6が形成されている。励起光源21から発せられたY方向の偏光を有する励起光は、金属突起13、14からなるアンテナYに共鳴して、量子ドット4を励起する。その後の量子ドットからの発光は、金属突起11、12からなるアンテナXに結合し、X偏光の光子として外部に取り出される。

(もっと読む)

側壁光検出器

集積フォトニック・デバイスに対する側壁光検出器及びそれらの製造の方法。実施形態は、マルチモード・ファイバーのスポット・サイズを適合するように十分に大きい領域を有する基板半導体機能の側壁に形成されたp-i-n積層膜を含む。実施形態は、第2側壁光検出器に導波路によって結合された第1側壁光検出器を含み、その第1側壁光検出器は、第1側壁に入射する光の第1波長を吸収し、第2波長を吸収するように調節されたi層を有する第2側壁光検出器に第2波長の光を通過させるように調節されたi層を有する。  (もっと読む)

(もっと読む)

光デバイス、半導体基板、光デバイスの製造方法、および半導体基板の製造方法

【課題】高品質な光デバイスをシリコン基板上にモノリシックに形成する。

【解決手段】シリコンを含むベース基板と、ベース基板上に設けられた複数のシード結晶と、複数のシード結晶に格子整合または擬格子整合する複数の3−5族化合物半導体とを備え、複数の3−5族化合物半導体のうちの少なくとも1つに、供給される駆動電流に応じて光を出力する発光半導体、または光の照射を受けて光電流を発生する受光半導体を含む光電半導体が形成されており、複数の3−5族化合物半導体のうち、光電半導体を有する3−5族化合物半導体以外の少なくとも1つの3−5族化合物半導体にヘテロ接合トランジスタが形成されている光デバイスを提供する。

(もっと読む)

光電変換装置および放射線撮像装置

【課題】光電変換素子における逆導電型の半導体層のエッジ間でのリーク電流を抑えるようにする。

【解決手段】絶縁層(66,68)にn型半導体層71の面積よりも小さい面積(上部開口面積)のコンタクトホール69を形成し、当該コンタクトホール69を介してp型半導体層64とi型半導体層70が接するようにする。すなわち、p型半導体層64のi型半導体層70と接するエッジ(コンタクトホール69の下部開口端)をn型半導体層71のエッジよりも内側に位置させる。これにより、p型半導体層64のi型半導体層70と接するエッジとn型半導体層71のエッジの間の距離を、従来技術のようにp型半導体層64とn型半導体層71がほぼ同一形状で形成され、p型半導体層64とi型半導体層70が直接接している場合に比べて長くする。

(もっと読む)

半導体基板およびその製造方法、並びに半導体装置

【課題】段差部において膜厚の急激な変動が抑制された半導体膜を含む半導体基板、およびその製造方法、並びに、その半導体基板を備える半導体装置を提供する。

【解決手段】本発明に係る半導体基板1は、下地基板10と、下地基板10上の一部に形成されている金属膜20と、金属膜20を覆うようにして下地基板10上に形成されている絶縁膜30と、絶縁膜30上に形成され、かつ結晶化された半導体膜40とを備えている。絶縁膜30は、金属膜20の端部において段差部を有し、当該段差部の下地基板10に対して垂直な断面形状が、外に膨らむ「R」形状を呈している。上記段差面は、その上端部から下端部に向かって、テーパー角度ψが略0°から徐々に大きくなって、略40°〜90°であるテーパー角度θになるように形成されている。

(もっと読む)

窒化物半導体層の剥離方法、半導体装置の製造方法、及び半導体装置

【課題】第1基板から窒化物半導体層を容易に剥離する。

【解決手段】SiC基板101の表面で単層又は複数層のグラフェン層111が成長する工程と、グラフェン層との界面で、共有結合性を有することなく、原子レベルのポテンシャルの規則性のみを用いた結合力を伴って窒化物半導体層114が形成される工程と、窒化物半導体層114とグラフェン層111aとの間、あるいはグラフェン層相互間111a,111b,111cのポテンシャルによる接合力以上の力で、窒化物半導体層がSiC基板から剥離される工程とを備える。また、剥離された窒化物半導体層が第2基板130の表面に接合される。

(もっと読む)

121 - 140 / 513

[ Back to top ]