Fターム[5F058BA10]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成の目的、効果 (3,596) | 密着性向上 (177)

Fターム[5F058BA10]に分類される特許

41 - 60 / 177

薄膜トランジスタの製造方法

【課題】基板との密着性が高いゲート絶縁層を設けることにより信頼性の高い電界効果トランジスタを提供することを目的とする。

【解決手段】絶縁基板上に少なくともゲート電極、ゲート絶縁層、酸化物を含む半導体層、ソース電極およびドレイン電極が設けられ、前記ゲート絶縁層は前記絶縁基板と接触する下部ゲート絶縁層と、該下部ゲート絶縁層の上に形成された一層以上の上部ゲート絶縁層を積層してなる薄膜トランジスタの製造方法であって、前記下部ゲート絶縁層がイオンビームスパッタ法により成膜されることを特徴とする薄膜トランジスタの製造方法としたものである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】電極とキャパシタ用絶縁膜(金属酸化膜)との間に発生する気泡状の剥がれの発生を防止することができる半導体装置およびその製造方法を提供する。

【解決手段】基体上にソースガスを供給S1して、ALD法により金属窒化膜を3nm以下の膜厚で堆積S2,S3,S4し、金属窒化膜を酸化S5,S6して金属酸化膜を形成する工程を複数回繰り返して、基体上に、金属酸化膜からなる積層膜を形成する。これにより電極とキャパシタ用絶縁膜(金属酸化膜)との間に発生する気泡状の剥がれを防止することができる。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 成膜温度を低下させ、成膜速度を増大させる。

【解決手段】 基板を収容した処理室内にシリコン含有ガスとボロン含有ガスとを供給して基板上にシリコン含有及びボロン含有膜を形成するシリコン含有及びボロン含有膜形成工程と、大気圧未満の圧力に設定した処理室内に酸素含有ガスと水素含有ガスとを供給して基板上に形成したシリコン含有及びボロン含有膜をボロン及びシリコン含有酸化膜に改質するシリコン含有及びボロン含有膜改質工程と、を有する。

(もっと読む)

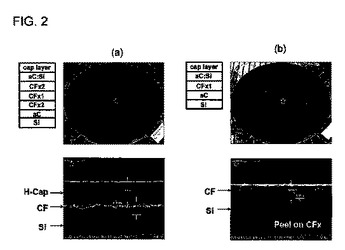

プラズマ処理方法

絶縁層としてフッ素化炭素層を持つ半導体装置を製造する方法であり、前記方法は:マイクロ波パワー励起プラズマを用いて第1のフッ素化炭素(CFx1)層を形成するステップ;及びRFパワー励起プラズマを用いて第2のフッ素化炭素(CFx2)層を形成するステップを含む。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】キャパシタの強誘電体又は高誘電体からなる容量絶縁膜が水素バリア膜から発生する水素によって劣化することを確実に防止できるようにする半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板11の上に形成された強誘電体又は高誘電体からなる容量絶縁膜18を有するキャパシタ20と、キャパシタ20の下側に形成された第1の水素バリア膜15とを有している。第1の水素バリア膜15は、フッ素を含む窒化シリコンからなる。

(もっと読む)

酸化マンガン膜の形成方法、半導体装置の製造方法および半導体装置

【課題】 Cuとの密着性を良好とすることが可能な酸化マンガン膜の形成方法を提供すること。

【解決手段】 酸化物102上にマンガンを含むガスを供給し、酸化物102上に酸化マンガン膜103を形成する酸化マンガン膜103の形成方法であって、酸化マンガン膜103を形成する際の成膜温度を、100℃以上400℃未満とする。

(もっと読む)

選択的窒素化の方法

ここに、半導体装置の形成方法が提供された。ある実施の形態において、半導体装置の形成方法は、酸化物表面とシリコン表面とを有する基板を用意し、酸化物表面およびシリコン表面の双方の露出面に窒素含有層を形成し、酸化物表面上から窒素含有層を選択的に除去することによって窒素含有層を酸化する工程を有する。別の実施の形態において、シリコン特徴部上に形成された窒素含有層の残余部分上に酸化物層が形成される。また、ある実施の形態において、酸化物表面が半導体装置の1つまたはそれ以上のフローティングゲートに隣接して配置されている浅いトレンチ分離領域(STI)の露出した表面である。ある実施の形態において、シリコン表面は、半導体装置のシリコンまたはポリシリコンのフローティングゲートの露出面である。  (もっと読む)

(もっと読む)

電界効果型トランジスタ

【課題】ゲート絶縁層とチャネル層との密着性が良好な電界効果型トランジスタを提供する。

【解決手段】基板と、前記基板上に、ゲート電極と、ゲート絶縁層と、チャネル層と、ソース電極と、ドレイン電極と、を有し、前記ゲート絶縁層は酸化ガリウムを含み、前記チャネル層は有機半導体層である、電界効果型トランジスタ。

(もっと読む)

有機電気装置のための封入方法

本開示は、障壁層を電子装置に封入するための使用に適した方法および材料を提供する。一実施形態では、たとえば、ケイ素含有結合材料およびセラミック材料の交互する層によって封入された、電気発光装置または他の電子装置を提供する。本封入方法は、たとえば、安定性および貯蔵寿命が増加した電子装置を提供する。本発明は、たとえばマイクロ電子装置の分野において有用である。別の態様では、基材上に配置された複数の構成要素層を含む電子装置と、障壁材料および架橋結合した材料の第1の対の層を含む封入部分とを含み、障壁材料がセラミック材料であり、架橋結合した材料がケイ素含有ポリマーである、封入された電子装置を提供する。 (もっと読む)

絶縁膜の成膜方法及びその成膜装置

【課題】 量産に適した、コンタミの少ない、組成制御された、ち密で、欠陥、粒界の極めて少ない、深さ方向に構造制御された、良好な絶縁特性を持つ絶縁膜の提供。

【解決手段】 O、N及びFから選ばれた少なくとも1種を含む気体状分子を該基板表面に供給し、吸着させた後排気する第1の工程の後に、Al、Si、Ta、又はTiを含む気体状分子を基板表面に供給し、吸着させた後排気する第2の工程を行い、その後にArを導入した後排気する第3の工程を行い、前記第1〜第3の工程を1つのサイクルとして、このサイクルを複数回行うことを特徴とする。

(もっと読む)

多孔質膜

【課題】基板との密着性に優れ、誘電率、硬度等の諸特性に優れ、誘電率の経時変化が小さく、半導体素子デバイスなどにおける層間絶縁膜として使用するのに適した多孔質膜、およびその多孔質膜を製造する組成物を提供する。

【解決手段】多孔質膜は、加熱、光照射、放射線照射またはそれらの組み合わせにより、その一部が脱離して揮発性成分を生じる官能基を有する化合物(X)を用いて形成され、空孔分布曲線における最大ピークを示す空孔直径が5nm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】相異なる膜質領域を有する層間絶縁膜において、膜界面における膜剥れや隣接配線間リークの発生を抑制する。

【解決手段】単層構造の層間絶縁膜である第3の絶縁膜107は複数の空孔120を有している。第3の絶縁膜107における単位体積当たりの空孔占有率は膜厚方向に変化している。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備える平板表示装置

【課題】酸素を含む化合物半導体を活性層とする薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、基板10上に形成されたゲート電極12と、ゲート絶縁膜13によりゲート電極12と絶縁され、ゲート電極12を覆うようにゲート絶縁膜13上に形成された、酸素を含む化合物半導体からなる活性層14と、活性層14の上部に形成された保護層15と、活性層14と接触するソース電極16a及びドレイン電極16bと、を備え、保護層15が、チタン酸化物(TiOx)またはチタン酸窒化物(TiOxNy)で形成される。

(もっと読む)

圧電素子

【課題】エアロゾルデポジション法により形成された薄膜を有しながら、膜剥離が発生しにくく、電気評価が良好であるため歩留りが改善されるとともに、優れた圧電特性を達成できる積層型圧電素子を提供する。

【解決手段】基板14の上に、第一層11、第二層12、及び第三層13がこの順序で積層された四層構造の圧電素子において、第一層11、第二層12、及び第三層13は、各々がエアロゾルデポジション法によって成膜されたセラミックス膜であり、第一層11の弾性率は第二層12の弾性率よりも大きく、第二層12の弾性率は第三層13の弾性率よりも大きい。第一層11/第二層12/第三層13の具体的態様としては、ZrO2/PZT/PZT、Al2O3/ZrO2/PZT、Al2O3/PZT/PZTがある。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】本発明は、比誘電率が10以上のhigh-k材料から構成されるMIMキャパシタの高誘電率膜がトランジスタや配線の設けられる箇所に形成されない半導体装置を容易に製造できる方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上に下地電極を形成する工程と、前記下地電極上にフォトレジストを塗布する工程と、前記下地電極の外周部より中央側において前記フォトレジストに開口部を形成する工程と、比誘電率が10以上のhigh-k材料から構成される高誘電率膜を成膜する工程と、前記下地電極の外周部より中央側に前記高誘電率膜が残るように、リフトオフを行なう工程と、前記リフトオフにより残された前記高誘電率膜上に上地電極を形成する工程と、を備えることを特徴とするものである。

(もっと読む)

薄膜多層配線基板およびその製造方法

【課題】 剥離の発生の少ない薄膜多層配線基板とその製造方法を提案する。

【解決手段】 少なくとも一つの前記配線層が、下層の配線層上に形成された第一のSiO2薄膜と、前記第一のSiO2薄膜上に形成されたSiON薄膜と、前記SiON薄膜上に形成された第二のSiO2薄膜と、前記第二のSiO2薄膜に埋め込まれて形成された配線導体と、前記配線導体と接続しかつ前記第一のSiO2薄膜、前記SiON薄膜および前記第二のSiO2薄膜を貫通して前記下層の配線層の配線導体と電気的に接続するビア導体と、前記第二のSiO2薄膜上に形成されたSiN薄膜と、で構成されている。

(もっと読む)

半導体装置の製造方法及び成膜システム

【課題】フッ素添加カーボン膜(CF膜)上にハードマスク用の薄膜であるSiCO膜あるいはSiCN膜を成膜するにあたり、その薄膜とフッ素添加カーボン膜との間で大きな密着性を得ること。

【解決手段】 SiCO膜をハードマスクとして使用する場合に、CF膜をシリコンの有機化合物例えばトリメチルシランガスを活性化したプラズマ雰囲気に例えば5〜10秒程度曝し、次いでこのプラズマに窒素プラズマを加えてフッ素添加カーボン膜の上にSiCN膜を成膜し、その後例えばトリメチルシランガスと酸素ガスとを活性化したプラズマによりSiCO膜を成膜する。SiCO膜の成膜時に、酸素の活性種がCF膜中の炭素と反応することが抑えられ、従ってCF膜の脱ガス量が低減する。またSiCN膜をハードマスクとして使用する場合も、同様に最初にトリメチルシランガスのプラズマ処理を行う。

(もっと読む)

誘電体膜の形成方法

【課題】薄い絶縁物の分子層で覆われたSi基板表面にCVD法により誘電体膜を形成する際のインキュベーション時間をなくし、得られる誘電体膜の均一性を向上させると同時に、誘電体膜の膜厚方向の組成を制御する。

【解決手段】Si基板上への誘電体膜の形成方法は、前記Si基板上に第一の金属の気相分子化合物を実質的に一様に吸着させ、前記Si基板上を前記第一の金属の気相分子化合物により覆う第一の工程と、前記Si基板を覆う前記第一の金属の気相分子化合物を酸化雰囲気中で分解し、前記Si基板上に前記第一の金属を含む第一の誘電体分子層を形成する第二の工程と、前記Si基板上に第二の金属の気相分子化合物を実質的に一様に吸着させ、前記Si基板上を前記第二の金属の気相分子化合物により覆う第三の工程と、前記Si基板を覆う前記第二の金属の気相分子化合物を酸化雰囲気中で分解し、前記第一の誘電体分子層上に前記第二の金属を含む第二の誘電体分子層を形成する第四の工程と、を含む

(もっと読む)

半導体装置の製造方法

【課題】バリア膜を良好に形成することができながら、Cu配線中のMnの残留量を低減することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む第2絶縁層6に、第2溝11およびビアホール12が形成された後、Mnからなる金属膜18が第2溝11およびビアホール12の側面および底面に被着される。次いで、金属膜18中のMnと第2絶縁層6中のSiおよびOとを結合させるための熱処理が行われる。この熱処理の結果、第2溝11およびビアホール12の内面上に、MnSiOからなるバリア膜が形成される。

(もっと読む)

半導体装置の製造方法

【課題】溝を埋め尽くすように形成されるCu層中のMnの残留量の増加を生じることなく、溝の側面上における合金膜の膜剥がれの発生を防止することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む絶縁材料からなる第2絶縁層6に、第2溝11が形成される。次に、スパッタ法により、第2溝11の内面に、CuMn合金からなる合金膜18が被着される。この合金膜18は、第2溝11の内面に接する部分のMn濃度が相対的に高く、その表層部分のMn濃度が相対的に低くなるように形成される。次いで、合金膜18上に、Cuからなる第2配線14が形成される。第2配線14の形成後、熱処理により、第2配線と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。

(もっと読む)

41 - 60 / 177

[ Back to top ]