Fターム[5F058BJ01]の内容

Fターム[5F058BJ01]に分類される特許

1 - 20 / 1,170

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた表示装置、スパッタリングターゲット材

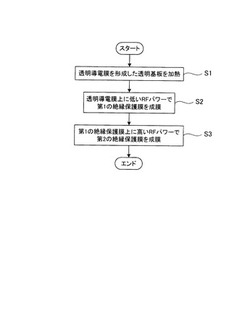

絶縁保護膜形成方法

【課題】透明導電膜の透過率を低下させることなく、絶縁保護膜を形成することができる絶縁保護膜形成方法を提供する。

【解決手段】透明基板に形成された透明導電膜上にプラズマ処理により絶縁保護膜を形成する絶縁保護膜形成方法において、基板の単位面積当たりのプラズマのRFパワーを1.84W/cm2以下とし、加熱時間を60秒以下として、プラズマにより透明基板を加熱し(S1)、RFパワーを1.84W/cm2以下として、透明導電膜上に第1の絶縁保護膜を形成し(S2)、RFパワーを1.84W/cm2より大きくして、第1の絶縁保護膜上に第2の絶縁保護膜を形成する(S3)。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

成膜装置及びその運用方法

【課題】処理容器内の処理空間に接する石英製の部材の表面に対するカーボン膜の密着性を向上させてパーティクルの発生を抑制することができる成膜装置の運用方法を提供する。

【解決手段】石英製の処理容器8内で保持手段22に保持された複数の被処理体Wの表面にカーボン膜を成膜する成膜工程を行うようにした成膜装置の運用方法において、処理容器内の処理空間に接する石英製の部材の表面にカーボン膜の密着性を向上させる密着膜70を形成する密着膜形成工程を行うようにする。これにより、処理容器内の処理空間に接する石英製の部材の表面に対するカーボン膜の密着性を向上させてパーティクルの発生を抑制する。

(もっと読む)

半導体装置の製造方法、基板処理方法、基板処理装置およびプログラム

【課題】低温領域において、フッ化水素に対する耐性の高い窒化膜を形成する。

【解決手段】基板に対して原料ガスを供給する工程と、基板に対してプラズマ励起させた水素含有ガスを供給する工程と、基板に対してプラズマ励起または熱励起させた窒化ガスを供給する工程と、基板に対してプラズマ励起させた窒素ガスおよびプラズマ励起させた希ガスのうち少なくともいずれかを供給する工程と、を含むサイクルを所定回数行うことで、基板上に窒化膜を形成する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】消費エネルギーを抑制しつつ成膜性能を向上する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、ウエハ2を処理室20へ搬入する搬入工程(S1)と、処理室20を排気する排気工程と、処理室20を所定の圧力まで降下する降圧工程(S2)と、複数の処理ガスを供給してウエハ2に膜を形成する成膜工程(S4)と、処理室20を所定の圧力まで上昇する昇圧工程(S7)と、ウエハ2を処理室20から搬出する搬出工程(S8)と、成膜工程(S4)における排気量が、降圧工程(S2)及び昇圧工程(S7)における排気量よりも大きくなるように調整する調整工程と、を有する。

(もっと読む)

熱処理方法および熱処理装置

【課題】フラッシュ加熱処理時における薄膜の過度の加熱を抑制することができる熱処理方法および熱処理装置を提供する。

【解決手段】表面に二酸化ケイ素の基材を形成し、さらにその上にアモルファスシリコンの薄膜を形成した半導体ウェハーWをチャンバー6内に搬入する。フラッシュランプFLへの電力供給回路には絶縁ゲートバイポーラトランジスタ(IGBT)が接続されており、そのIGBTによってフラッシュランプFLへの通電時間を0.01ミリ秒以上1ミリ秒以下とすることにより、フラッシュ光照射時間を0.01ミリ秒以上1ミリ秒以下としている。顕著に短いフラッシュ光照射時間にてフラッシュ加熱処理を行うため、アモルファスシリコンの薄膜が過度に加熱されることは抑制され、当該薄膜が剥離するなどの弊害が防止される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】結晶欠陥の発生を抑え、デバイスのリーク電流の発生、耐圧低下、しきい値電圧の継時変化、およびショートチャネル効果を抑制することが可能な半導体装置を提供すること。

【解決手段】単結晶AlNからなる基板を準備するステップと、前記単結晶AlNからなる基板の表面を酸素プラズマによって酸化し、単結晶AlNからなる基板上に酸化アルミニウムまたはアルミニウムオキシナイトライドからなる絶縁膜を形成するステップとを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

酸化膜の形成方法

【課題】シリコン表面のプラズマ酸化により、界面準位密度が低くリーク電流の少ない高品質な酸化膜をシリコン表面上に形成する。

【解決手段】

酸化膜の形成方法は、KrとO2の混合ガス中にプラズマを形成することにより原子状酸素O*を発生させ、前記原子状酸素O*によりシリコン表面をプラズマ酸化するプラズマ酸化工程を含み、前記プラズマ酸化工程は、800〜1200mTorrの圧力範囲において実行される。

(もっと読む)

半導体装置の製造方法、基板処理方法、基板処理装置およびプログラム

【課題】酸化膜と窒化膜との積層構造を有する絶縁膜の膜厚均一性を向上させ、生産性を向上させる。

【解決手段】処理容器内の基板に対して、原料ガスを供給する工程と、窒化ガスを供給する工程と、酸化ガスを供給する工程と、を含むサイクルを所定回数行うことにより、酸化膜を形成する工程と、処理容器内の基板に対して、原料ガスを供給する工程と、窒化ガスを供給する工程と、を含むサイクルを所定回数行うことにより、窒化膜を形成する工程と、を交互に所定回数行うことにより、基板上に酸化膜と窒化膜とが積層されてなる積層膜を形成する工程を有し、酸化膜を形成する工程および窒化膜を形成する工程を、基板の温度を同様な温度に保持しつつ、連続的に行う。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】耐圧をより向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体積層構造8と、基板1と化合物半導体積層構造8との間に形成された非晶質性絶縁膜2と、が設けられている。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】酸化物半導体を用いた低温プロセスで形成する信頼性の高い薄膜トランジスタ、その製造方法、および表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板100と、前記基板上の一部に設けられたゲート電極110と、前記ゲート電極を覆う第1の絶縁膜120と、前記第1の絶縁膜を介して前記ゲート電極上に設けられた酸化物半導体膜130と、前記酸化物半導体膜上の一部に設けられた第2の絶縁膜150と、前記酸化物半導体膜から露出する酸化物半導体膜の一部と接続されたソース電極140Sおよびドレイン電極140Dと、を備え、前記酸化物半導体膜はInと、Gaと、Znのうち少なくとも一つの元素を含む酸化物半導体を有し、前記第1の絶縁膜中に含有される水素濃度が5×1020atm/cm−3以上であり、かつ、前記第2の絶縁膜中に含有される水素濃度が1019atm/cm−3以下である。

(もっと読む)

半導体装置及びその製造方法、電源装置、高周波増幅器

【課題】放置時間が長くても、化合物半導体積層構造の表面のダングリングボンドがフッ素で終端された状態が維持されるようにし、閾値電圧の変動を抑制して、信頼性を向上させる。

【解決手段】半導体装置は、化合物半導体積層構造6と、化合物半導体積層構造6の表面を覆うフッ素含有バリア膜9と、化合物半導体積層構造6の上方にフッ素含有バリア膜9を挟んで設けられたゲート電極8とを備える。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】複数の種類のガスを用いる場合においても、所望の膜質を得られる基板処理装置及び半導体装置の製造方法を提供する。

【解決手段】基板処理装置10は、複数の基板900を円周方向に支持するサセプタ60と、サセプタを回転させる回転機構120と、サセプタの支持面62上の空間に設けられた複数の領域と、これらの複数の領域にガスを供給するガス供給部200と、を有し、ガス供給部200は、複数の領域における隣り合う領域で同じガスを供給するか、若しくは複数の領域における隣り合う領域で異なるガスを供給するかが選択可能な構成である。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

半導体素子被覆用ガラス

【課題】環境への負荷が小さくて化学耐久性に優れ、かつ、表面電荷密度が低く、特に低耐圧用の半導体素子を被覆するために好適なガラスを提供する。

【解決手段】ガラス組成として、質量%で、ZnO 52〜65%、B2O3 5〜20%、SiO2 15〜35%およびAl2O3 3〜6%を含有し、かつ、鉛成分を実質的に含有しないことを特徴とする半導体素子被覆用ガラス。さらに、組成として、Ta2O5 0〜5%、MnO2 0〜5%、Nb2O5 0〜5%、CeO2 0〜3%およびSb2O3を含有することが好ましい。

(もっと読む)

半導体装置の製造方法、基板処理方法および基板処理装置

【課題】形成した絶縁膜のリーク電流を抑制することができる半導体装置の製造方法、基板処理方法および基板処理装置を提供する。

【解決手段】基板を収容した処理室にそれ単独で固体となる第1の元素を含む第1の処理ガスをCVD反応が生じる温度条件下で供給することで、前記基板上に前記第1の元素を含む第1の層を形成する工程と、前記処理室にそれ単独では固体とならない第2の元素を含む第2の処理ガスを供給することで、前記第2の処理ガスと前記第1の層を反応させ前記第1の元素および前記第2の元素を含む第2の層を形成する工程と、を1回ずつ含むサイクルを1サイクルとして、このサイクルを1回以上行うことで、所定膜厚の前記第1の元素および前記第2の元素を含む薄膜を形成する。

(もっと読む)

1 - 20 / 1,170

[ Back to top ]