Fターム[5F064CC23]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | コンデンサ、キャパシタ (371)

Fターム[5F064CC23]に分類される特許

101 - 120 / 371

半導体装置、下層配線設計装置、下層配線設計方法およびコンピュータプログラム

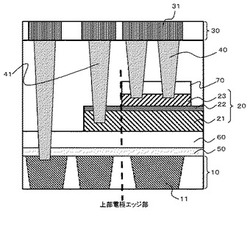

【課題】MIMキャパシタの構造破壊に起因するリーク電流の上昇を低減する構成を備えた半導体装置を提供することを課題とする。

【解決手段】複数の下層配線11を備える下層配線層10と、下層配線層10の上方に設けられる、下部電極21と容量誘電膜22と平面形状が下部電極21より小さい上部電極23とを下からこの順に積層したMIMキャパシタ20と、MIMキャパシタ20の上方に設けられ、ビア40、41を介して下部電極21および上部電極23のそれぞれに接続する複数の上層配線31を備える上層配線層30と、を備えた半導体装置であって、上部電極23の平面形状は矩形に構成され、上部電極23の平面のいずれか一以上の辺であるエッジ部の直下には下層配線11が配置されていない半導体装置を提供する。

(もっと読む)

半導体装置

【課題】半導体を実装するプリント基板の不要輻射経路の複雑化、不要輻射の影響を抑制するとともに、コスト増を抑制することが可能な半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1動作周波数又はサンプリング周波数により動作する第1論理回路ブロック10と、第1論理回路ブロック10に、第1電源配線12を介して接続された第1電源端子11及び第1接地配線14を介して接続された第1接地端子13と、第1動作周波数又はサンプリング周波数と異なる第2動作周波数又はサンプリング周波数により動作する第2論理回路ブロック20と、第2論理回路ブロック20に第2電源配線22を介して接続された第2電源端子21及び第2接地配線24を介して接続された第2接地端子23とを備える。

(もっと読む)

ばらつきを考慮した半導体集積回路の設計方法

【課題】少数の離散的な電荷によって生じるトランジスタ特性のばらつきを考慮した半導体集積回路の設計方法を提供する。

【解決手段】単一の電荷が付加されることにより生じるトランジスタ特性の変位xの確率密度関数P1(x)を決定する工程と、P1(x)と、付加される電荷の個数nの出現確率と、を元に回路設計上想定すべき設計余裕Mを決定する工程と、を備える。単一の電荷が特性に影響を与えるほど微細なトランジスタを有する半導体集積回路においても、正確にばらつきが計算できる。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】MIM容量の搭載数を変化させた評価を、効率良く行うことができる半導体装置及びそのレイアウト方法。

【解決手段】本発明に係る半導体装置は、下層電極107と、上層電極109と、両電極間に形成された容量絶縁膜108を有するMIM容量MC1と、下層電極107に接続され、下層電極107の主面の法線方向上向きに延設された第1のビアホールVHcと、上層電極109に接続され、上層電極109の主面の法線方向上向きに延設された第2のビアホールVHbと、下層電極107よりも下側に形成された複数の下層配線102と、を備え、上層電極109の主面の法線方向から見た場合、第1及び第2のビアホールVHc、VHbが下層配線102と重なって形成されているものである。

(もっと読む)

半導体製品ダイのテスト方法及び同テストのためのテストダイを含むアセンブリ

【課題】製品ダイ(2011,300)の製品回路(202,302,304)をテストするためのテストアセンブリ(2000)を提供すること。

【解決手段】一実施形態では、テストアセンブリは、テストダイ(2010,400)及び該テストダイをホストコントローラ(2002)へ電気的に結合する相互接続基板(2008)を含む。該テストダイは、テスト回路(202A,402,404)及び製品回路を統合化された設計(102)に同時に設計するステップを含むテストダイ及び製品ダイに関する設計方法論(100)に従って設計可能である。テスト回路は、該テスト回路により必要とされるシリコン領域の量にほぼ関係なく、対応する製品回路に関して高度の欠陥検出範囲を提供するよう設計可能である。次いで該設計方法論は、統合化された設計をテストダイ及び製品ダイへと分割する(104)。テストダイはテスト回路を含み、製品ダイは製品回路を含む。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】チップサイズが小さくなるように、半導体集積回路を設計できるレイアウト設計装置を提供する。

【解決手段】ネットリスト及び遅延情報に基づいて、タイミング解析を行うタイミング解析部103と、タイミング解析にタイミングエラーが生じる場合、タイミングエラーに関連している調整対象セルを抽出する調整対象抽出部104と、第1セル枠は調整対象セルの境界線であり、第2セル枠の外側に第1拡散領域を有する複数の補強フィルセルを格納する補強フィルセルライブラリ105と、第2セル枠は複数の補強フィルセルの各々の境界線であり、調整対象セルに隣接する通常フィルセルと同じ大きさの第1補強フィルセルを、複数の補強フィルセルから抽出し、第1セル枠と第2セル枠とが隣接配置するように通常フィルセルを第1補強フィルセルに置き換え、トランジスタと第1拡散領域とを接続するセル置換部106とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】 信号線の形成位置に関わらず、信号線とMIM構造のキャパシタ11との間で発生する寄生容量が抑制できるようにする。

【解決手段】 MIM構造のキャパシタ11と、絶縁膜12a,12bを介してMIM構造のキャパシタ11を挟む、少なくとも一対の遮蔽部13a,13bとを備える。

(もっと読む)

三次元半導体集積回路

【課題】複数チップからの二値データを一箇所に集めずに多値データを生成する。

【解決手段】本発明の例に係る三次元半導体集積回路は、積み重ねられる第一乃至第三チップ11,12,13を有する。第二チップ12内の第二回路15は、二値の第一データAが入力され、第一及び第二電位のうちの一つを出力する第一インバータと、第一インバータの出力端と共通導電体との間に接続される第一キャパシタとを備える。第三チップ13内の第三回路16は、二値の第二データBが入力され、第三及び第四電位のうちの一つを出力する第二インバータと、第二インバータの出力端と共通導電体との間に接続される第二キャパシタとを備える。

(もっと読む)

半導体装置及び半導体装置の補償容量の配置方法

【課題】回路セル内の領域を有効活用して十分な補償容量を確保し、電源電圧の変動を確実に抑制し得る半導体装置等を提供する。

【解決手段】本発明の半導体装置は、第1の方向に並んで配置された複数の素子を含む回路セル2と、この回路セル2の第1の方向に隣接して配置され回路セル2の電源に接続可能な補償容量C1、C2を有する基本端セル1(1a)とを備えて構成される。補償容量C1、C2を構成する拡散層10、11は、回路セル2の所定領域(素子間接続領域R1)を第1の方向に沿って延伸形成されている。また、拡散層10、11の上部にはゲート配線16、17が延伸形成されている。本発明の構成により、回路セル2の素子間接続領域R1を有効に活用しつつ、補償容量のC1、C2の容量値を増加させて電源変動の変動を確実に抑えることが可能となる。

(もっと読む)

半導体集積回路および半導体集積回路のレイアウト設計方法

【課題】回路面積の狭小化の要請と電源電圧ドロップによる動作不良の防止の要請とをともに満足する半導体集積回路を提供する。

【解決手段】半導体集積回路10の内部回路配置領域22を、電源電圧ドロップ対策を施する領域Pと電源電圧ドロップ対策を施さない領域Lとに分ける。そして、内部回路をなすセルのうち消費電流の大きいセルを領域Pに行として配置し、消費電流の大きくないセルを領域Lに行として配置する。さらに、高電位側電源線31,33および低電位側電源線32の線幅を太くする第1の電源電圧ドロップ対策と、セル間にデカップリング容量8−m(m=1,2…)を形成する第2の電源電圧ドロップ対策とを施す。

(もっと読む)

半導体装置

【課題】容量素子を構成する第1電極及び第2電極を形成するためのリソグラフィ工程で重ね合わせズレが生じた場合にも容量ばらつきを抑制できる半導体装置を提供する。

【解決手段】複数の配線層L1〜L5のそれぞれは、絶縁膜103〜106と、当該絶縁膜中に相互に離隔し且つ向かい合うように埋め込まれた第1電極101及び第2電極102とを有する。一の配線層の第1電極101と、その上方又は下方に設けられた他の配線層の第2電極102とは相互に向かい合うように配置されている。一の配線層の第1電極101の幅と、他の配線層の第2電極102の幅とは異なっている。

(もっと読む)

容量素子、容量素子の設計方法および容量素子を含む集積回路装置

【課題】容量値としての変動(ばらつき)が細密構造に比べて小さいデバイス構造を設計する。

【解決手段】多層配線の各配線に関するパラメータを統計的処理で変化させた複数のデバイス構造に対する総容量値、線間容量値および層間容量値を算出する。次いで、複数のデバイス構造の中から、デバイス構造間における総容量値の差分が例えば0.1以下でかつ総容量値に対する線間容量値の比と総容量値に対する層間容量値の比の差分が例えば0.01以内のデバイス構造を特定する。そして、この特定したデバイス構造についてのパラメータを、容量素子を形成する多層配線の各配線のパラメータとする。

(もっと読む)

半導体装置

【課題】基板の面内方向のばらつきに関わらず、素子の特性値の設計値からのずれを低減する。

【解決手段】半導体装置100は、基板に形成され、それぞれ、長軸方向と短軸方向とを有する所定パターンの膜を含み、基板の面内方向の同一層に分散配置された複数の分割素子(200aまたは200b)を含む。複数の分割素子は、第1の方向において隣接する分割素子の膜の長軸方向が異なるか、または、第1の方向において隣接する分割素子が、第1の方向と直交する第2の方向に、当該第2の方向における分割素子の長さよりも小さい量だけずらして配置される。

(もっと読む)

電子デバイスをソース技術からターゲット技術に移行する方法及びコンピュータ・プログラム(電流モード動作電子デバイスをターゲット技術に移行する方法)

【課題】アナログ/ミックスド・シグナル電子回路をソース技術からターゲット技術に移行する有用な方法を提供する。

【解決手段】まず、ソース技術電子回路内の電流モード動作デバイス及びそれらの電圧調整ノードが識別される。電流モード動作デバイスはそれ自体の電圧調整ノードに印加される電圧に対する感度が低いため、回路内の他のデバイスのバイアス条件に干渉することなく、電圧調整ノードの電圧を変更して電流モード・デバイスの性能を高めることが可能となる。これにより、回路設計者は、電流モードで動作する電子デバイスをソース技術からターゲット技術に移行する際に使用可能な2つの自由度(典型的には幅及び長さ)を余すところなく利用することが可能となる。

(もっと読む)

半導体装置

【課題】外部からの電気的な干渉が十分に低減されるとともに、所望の特性を発揮する容量素子が形成される半導体装置、を提供する。

【解決手段】半導体装置は、主表面1aを含む半導体基板1と、主表面1a上に規定された容量形成領域22に形成され、所定の方向に延在する複数の配線11と、容量形成領域22の周縁に配置された配線11pに隣り合い、所定の方向に延在し、電位固定された複数の配線12と、主表面1a上に形成され、複数の配線11の各々の間と、隣り合う配線11および配線12の間とを充填する絶縁体層5とを備える。複数の配線11および12は、主表面1aに平行な平面21内においてほぼ等しい間隔を隔てて配置され、かつ所定の方向に対してほぼ直角方向に並んで配置されている。

(もっと読む)

MOS型可変容量素子

【課題】回路構成を複雑化することなく、簡易な等価回路で高周波領域まで実際の電気的特性に合致する任意形状のMOS型可変容量素子をモデリングする。

【解決手段】MOS型可変容量素子は、第1導電型の半導体基板と、前記半導体基板内に形成された第2導電型のウェル領域と、前記ウェル領域内に形成された第2導電型の第1の拡散領域と、前記ウェル領域内に形成された第2導電型の第2の拡散領域と、電圧供給端子と、基板引き出し端子と、ウェル引き出し端子と、単位MOS可変容量部と、を備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、ボンディングパッドの間隔を任意に調整して配置することができないという問題があった。

【解決手段】本発明にかかる半導体装置は、機能ブロックが配置された内部回路と、ボンディングパッドを複数有するI/Oバッファセル205が内部回路の外周部に沿って配置された周辺回路と、を備える。また周辺回路は、隣接する2つのI/Oバッファセルに所定の間隔を持たせるように内部回路の外周部に沿って配置されたブランクセル206を備える。このような回路構成により、ボンディングパッドの間隔を任意に調整して配置することが可能な半導体装置を提供することができる。

(もっと読む)

半導体集積回路装置

【課題】デジタル回路領域とアナログ回路領域との離間距離を小さくでき、チップ面積の増大を抑制できる半導体集積回路装置を提供することを目的とする。

【解決手段】デジタル回路を形成するデジタル回路領域13と、アナログ回路を形成するアナログ回路領域12とに分離し、アナログ回路領域を、アナログ回路の能動素子を形成する能動素子領域12aと、アナログ回路の抵抗又はコンデンサを形成する抵抗容量素子領域12b,12cとに分離し、抵抗容量素子領域12b,12cをデジタル回路領域13と隣り合う領域に配置し、能動素子領域12aをデジタル回路領域13から離れた領域に配置する。

(もっと読む)

半導体装置

【課題】PIDの影響を遮断することのできるレイアウト手法を用いてアンテナダイオードを配置することにより、PIDに起因する電界効果トランジスタの特性劣化を防止して、信頼度の高い半導体装置を実現する。

【解決手段】第1アンテナダイオードAD1とnMISのゲート電極16とを第1層目の配線M1を介して電気的に接続し、第2アンテナダイオードAD2と他の半導体素子とを第1層目の配線M1から第4層目の配線(アナログブロック内の最上層配線から1層下の配線)M4を介して電気的に接続する。さらに第1アンテナダイオードAD1と電気的に繋がる第4層目の配線M4と第2アンテナダイオードAD2と電気的に繋がる第4層目の配線M4とをアナログブロック内の最上層配線である第5層目の配線25によって結線する。

(もっと読む)

半導体装置

【課題】信頼性が高く、特性の改善された半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置1は、ワンチップに規則性を有するレイアウト領域と、規則性のないレイアウト領域を備える半導体装置であって、下層導電層11と、下層導電層11上に形成された層間絶縁膜と、その上に形成された上層配線層M1と、下層導電層11と上層配線層M1とを、実質的に最短距離で電気的に接続するように配設した接続プラグ10とを備える。そして、規則性を有するレイアウト領域における少なくとも一部の領域において、下層導電層11と上層配線層M1との電気的接続が、下層導電層11の直上から延在する直上位置、当該直上位置から離間したシフト位置に配設した少なくとも2つの接続プラグ10と、これらを電気的に接続するための中間接続層20により行われている。

(もっと読む)

101 - 120 / 371

[ Back to top ]