Fターム[5F064CC23]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | コンデンサ、キャパシタ (371)

Fターム[5F064CC23]に分類される特許

121 - 140 / 371

グリッドプレートを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(200)は、集積回路の第1のパターニングされた金属層に形成された分配グリッド(226)と、分配グリッドに接続され、分配グリッドから離れる方に第1の方向に沿って延在する第1の縦方向導電性フィラメント(202)とを含む。第2の縦方向導電性フィラメント(203)は、分配グリッドに接続され、反対方向に延在する。第1のグリッドプレート(225)および第2のグリッドプレート(224)は、第1のパターニングされた金属層の上および下に形成される。グリッドプレートは、第1のおよび第2の縦方向導電性フィラメントを包囲する。分配グリッド、第1の縦方向導電性フィラメント、および第2の縦方向導電性フィラメントは、キャパシタの第1のノードに接続され、かつ第1のノードの一部分を形成し、第1のグリッドプレートおよび第2のグリッドプレートは、キャパシタの第2のノードに接続され、かつ第2のノードの一部分を形成する。  (もっと読む)

(もっと読む)

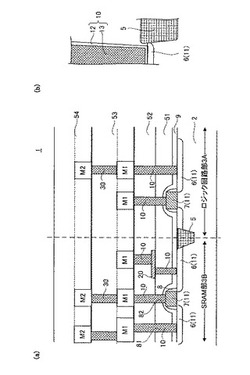

半導体装置

【課題】信頼性が高く、特性の改善された半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置1は、ワンチップに規則性を有するレイアウト領域と、規則性のないレイアウト領域を備える半導体装置であって、下層導電層11と、下層導電層11上に形成された層間絶縁膜と、その上に形成された上層配線層M1と、下層導電層11と上層配線層M1とを、実質的に最短距離で電気的に接続するように配設した接続プラグ10とを備える。そして、規則性を有するレイアウト領域における少なくとも一部の領域において、下層導電層11と上層配線層M1との電気的接続が、下層導電層11の直上から延在する直上位置、当該直上位置から離間したシフト位置に配設した少なくとも2つの接続プラグ10と、これらを電気的に接続するための中間接続層20により行われている。

(もっと読む)

互い違いになっている積層されたセグメントを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(100)は、ICの第1の金属層に形成され、キャパシタの第1のノードに電気的に接続され、かつ第1のノードの一部分を形成し、第1の軸(y)に沿って延在する第1のノードプレートリンク(102)と、ICの第2の金属層に形成され、当該軸に沿って延在し、かつビア(112)によって第1のノードプレートに接続された第2のノードプレートリンク(108)とを有する。第1の金属層に形成された第3のノードプレートリンク(106)は、キャパシタの第2のノードに電気的に接続され、かつ第2のノードの一部分を形成し、第1のノードプレートリンクに対して横断し第1のノードプレートリンクの一端に近接するノードプレートアレイの第2の軸(x)に沿って延在し、第2のノードプレートリンクの一部分の上にある。  (もっと読む)

(もっと読む)

半導体集積回路の設計装置、設計方法およびプログラム

【課題】半導体集積回路の電源ノイズを所定の許容範囲内に抑制するに必要なデカップリング容量を効率的に配置する。

【解決手段】設計装置は、初期見積部と概略電源ノイズ解析部とレイアウト設計部と詳細見積部と詳細電源ノイズ解析部とレイアウト調整部とを備える。初期見積部は、全体の消費電流およびオンチップ容量の概略値を見積る。概略電源ノイズ解析部は、見積られた概略値に基づいて、集中定数回路モデルによりモデル化して電源ノイズ解析を行い、電流容量比を算出する。レイアウト設計部は、電流容量比に基づいて、配置領域が分割された所定の領域毎にセルの配置を行う。詳細見積部は、所定の領域毎に集中定数回路モデルによりモデル化して所定の領域毎の消費電流およびオンチップ容量の詳細値を見積る。詳細電源ノイズ解析部は、詳細値に基づいて、詳細な電源ノイズ解析を行う。レイアウト調整部は、詳細電源ノイズ解析の結果に基づいて、セルの配置の調整を行う。

(もっと読む)

キャパシタ配置方法

【課題】レイアウトの効率化と周波数帯域に応じたノイズ抑制との双方を満足させる。

【解決手段】キャパシタのゲート幅と相関する周波数特性別にサイズの異なるセルを識別するための第1の分類と、周波数特性の異なるセルをサイズ別に識別するための第2の分類とに分類可能な複数のセルを記憶する。指定された周波数特性および配置エリアの組み合わせごとに、周波数特性に対応したセル群を第1の分類に基づき選択し、選択したセル群からより大きいサイズのセルを優先的に読み出し、配置エリアを充填するよう前記読み出したセルを配置する。全ての配置エリアに対しキャパシタ密度に関するルール違反の有無を検査する。違反を検知した場合、配置したセルのうち、より広いゲート幅のセルを前記第2の分類に基づく同一サイズのより狭いゲート幅のセルに置き換え、ルール違反に関する検査を再試行する。

(もっと読む)

半導体集積回路

【課題】配線効率を悪くすることなく効率よくノイズを除去可能な半導体集積回路を提供する。

【解決手段】スタンダードセル10に論理回路領域10aと容量領域10bとを具備させ、同一の配線層に属する1本の電源配線22及び2本の接地配線20,21(または2本の電源配線及び1本の接地配線)をスタンダードセル10に接続し、容量領域10bにおいて、MOS容量17を同一の配線層の電源配線22と接地配線21との間に接続する。

(もっと読む)

半導体装置

【課題】サイズおよびコストを抑えることができる半導体装置を提供する。

【解決手段】pMIS領域は、方向Xに沿って複数のスタンダードセルCffの各々を通る境界BRと、第1の外縁OTpとの間に形成されている。nMIS領域は、境界BRと第2の外縁OTnとの間に形成されている。電源配線VDおよび接地配線VSのそれぞれは、第1および第2の外縁OTp、OTnに沿って延びている。複数のpMIS配線M1pおよび複数のnMIS配線M1nのそれぞれは、方向Xに沿って延びかつ方向Yに沿ってピッチPminで配置された複数の第1の仮想ラインVLpおよび複数の第2の仮想ラインVLnの上に配置されている。複数の第1の仮想ラインVLpのうち境界BRに最も近いものと、複数の第2の仮想ラインVLnのうち境界BRに最も近いものとの間隔は、ピッチPminよりも大きい。

(もっと読む)

半導体デバイス設計支援装置及び基板ネットリスト作成方法

【課題】短時間で精度の高い基板ノイズ解析を行えるような基板ネットリストを作成する半導体デバイス設計支援装置の提供。

【解決手段】半導体デバイス設計支援装置は、半導体デバイスのレイアウトを複数のセグメントに分割し、該分割したセグメントに含まれるインスタンスの電流波形を用いて、該セグメントのマクロモデルを作成する手段と、前記セグメントにおける基板とのインタフェースとなるパターン(基板インタフェース)を、所定の基板インタフェース図形に置き換える手段と、複数のセグメントの基板インタフェース図形に基づいて、基板ネットリストを作成する手段と、を備える。

(もっと読む)

回路図設計装置、回路図設計プログラム及び回路図設計方法

【課題】 MOSトランジスタなどの回路素子を共有部分を介して連続接続してなるマルチ素子回路を含む半導体集積回路に係る回路図を設計するのに好適な回路図設計装置、回路図設計プログラム及び回路図設計方法を提供する。

【解決手段】 回路図設計装置100を、レイアウトされた回路図や選択画面から回路記号を選択する回路記号選択部12と、表示情報に基づき回路図の表示制御を行う回路図表示制御部16と、パラメータ設定可能な回路記号に対してマルチ素子回路を生成するためのパラメータを設定するパラメータ設定部18と、予め設定されたルールと回路記号に対して設定されたパラメータとに基づきマルチ素子回路の接続関係情報を生成する接続関係情報生成部20と、予め設定された表示方法のルールに基づきマルチ素子回路の回路記号の表示情報を生成する回路表示情報生成部22とを含んだ構成とした。

(もっと読む)

回路図設計装置、回路図設計プログラム及び回路図設計方法

【課題】 MOSトランジスタなどの回路素子を共有部分を介して連続接続してなるマルチ素子回路を含む半導体集積回路に係る回路図を設計するのに好適な回路図設計装置、回路図設計プログラム及び回路図設計方法を提供する。

【解決手段】 回路図設計装置100を、シンボル回路図や選択画面から回路シンボルを選択する回路記号選択部12と、回路図の表示制御を行う回路図表示制御部18と、パラメータ設定可能な回路シンボルに対してマルチ素子回路を生成するためのパラメータを設定するパラメータ設定部20と、設定されたパラメータが正しいか誤りかを判定するパラメータ判定部22と、パラメータの設定内容に誤りがあるときに正しい設定内容に修正するパラメータ修正部24と、予め設定されたルールと回路シンボルに対して設定されたパラメータとに基づきマルチ素子回路の接続関係情報を生成する接続関係情報生成部26と、を含んだ構成とした。

(もっと読む)

半導体集積回路及びその設計方法

【課題】デカップリングセルの配置場所を膨大な処理時間をかけて算出する必要が無く、電圧降下やノイズを効果的に防止できる位置にデカップリングセルを配置できる。

【解決手段】半導体集積回路100は、第1電位及び第2電位のセル用の電源配線101,102と、第1電位及び第2電位のセル用電源配線に垂直な方向に配置された第1電源配線103及び第2電源配線104と、スタンダードセル105と、デカップリングセル106とから構成される。第1電源配線103には第1電位、すなわち電源電位が供給され、第2電源配線104には第2電位、すなわちグランド電位が供給される。デカップリングセル106は、第2電源配線104の下に配置され、第1電位と第2電位が供給されている。スタンダードセル105の配置領域は、デカップリングセル106の配置部分以外の領域である。

(もっと読む)

LSIの設計方法

【課題】LSIにおいて、信頼性やノイズ問題の生じない最少の電源パッド数と配置を決定する方法を提供する。

【解決手段】1) 電源線のエレクトロマイグレーション(EM)、2) 信号線間クロストーク、3) I/Oバッファの同時スイッチング・ノイズ(SSN)、4) 不要電磁放射(EMI)と共振、という順番で解析し、それぞれに予め設定された判定基準が満たされたかどうかの判定を行う。これにより、解析毎に必要な電源パッド数と配置が求められる。前記解析はLSIが持っている各機能の高品質化と処理の高速化を目的に、LSI内の各種の機能グループ(DDR2/HDMI/USB I/F、PLL回路、テスト端子等)毎に行うことが好ましい。そして、機能グループ毎に判定基準を満たす電源パッド数と配置を決定する。

(もっと読む)

半導体装置

【課題】基板上に形成された第1導電型のウェルと第2導電型のウェルとの間でデカップリング容量を形成する際に、高い周波数まで追随できるようにする。

【解決手段】半導体装置100は、P型基板102上に形成された埋込Pウェル104と、その上に形成され、互いに隣接して交互に設けられた複数のPウェル106および複数のNウェル108と、を含む。各Nウェル108が埋込Pウェル104と接する領域の幅は、2μm以下である。Pウェル106およびNウェル108には、それぞれ接地電圧および電源電圧が印加される。Nウェル108と埋込Pウェル104との間でデカップリング容量が形成される。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、半導体集積回路の設計支援装置、及び半導体集積回路

【課題】本発明による半導体集積回路の設計方法、設計プログラムによれば、信頼性の高い累積故障確率の計算を行なうことができる。

【解決手段】本発明による半導体集積回路の設計方法は、半導体集積回路のレイアウト情報に基づいて、半導体集積回路全体のゲート面積を算出するステップと、経時絶縁破壊に対する累積故障確率を算出するステップと、累積故障確率を用いて半導体集積回路全体の累積故障確率を算出するステップとを具備する。

(もっと読む)

半導体集積回路

【課題】レイアウトパターンに依存した基本論理セル2の特性ばらつきを抑制する。

【解決手段】論理回路の部品として機能する基本論理セル(2)と、論理回路の部品としての機能を含まないダミーセル(1、21)とを具備する半導体集積回路を構成する。基本論理セル(2)は、基板に形成される拡散層(13、14)を含むものとする。そして、拡散層(13、14)は、基本論理セル(2)が、他のセル(1、2、21)に隣接して配置されるときに、それらの境界からの距離(L3)が、第1長さとなる位置に設けられていることが好ましい。また、ダミーセル(1、21)は、基板に形成されるダミー拡散層(3、4)を備えるものとする。そして、ダミー拡散層(3、4)は、ダミーセル(1、21)が、他のセル(1、2、21)に隣接して配置されるときに、それらの境界からの距離(L1)が、第1長さになる位置に設けられることが好ましい。

(もっと読む)

多層配線装置

【課題】本発明は、微細ピッチ多層配線構造を用いた並走配線間容量によるデカップリング容量において、高周波,高速特性に優れた大きなデカップリング容量を形成できるようにすることを最も主要な特徴とする。

【解決手段】たとえば、同一方向にピッチ配列された複数の配線M1a〜M1h,M2a〜M2f,M3a〜M3hの、そのピッチ配列の方向が互いに交差するように配線層M1,M2,M3を積層させる。そして、各配線層M1,M2,M3の、隣り合う配線におのおの異なる電位VDD,VSSが供給されるように、配線層M1,M2,M3の相互を接続してなる構成となっている。

(もっと読む)

磁気素子及び集積回路並びに磁気ランダムアクセスメモリ

【課題】磁気素子本体に電流を流すことなく、磁性体電極の磁化反転が可能な磁気素子及び集積回路並びに磁気ランダムアクセスメモリを提供する。

【解決手段】磁気素子1は、基板6上に第1の強磁性体電極3及び第2の強磁性体電極4を隔置し磁気素子本体2と、第1の強磁性体電極3に接触して高スピンホール効果を有する電極5を配設し、高スピンホール効果を有する電極5に電流を流して第1の強磁性体電極3へスピン注入して磁化反転する。磁気素子本体2へ電流を流すのではなく、高スピンホール効果を有する電極5に電流を流すことでスピンホール効果によるスピン分極を発生させ、第1の強磁性体電極3への移行により磁化反転できる。高インピーダンスの微小磁気メモリ素子及び磁気論理素子やスピン電界効果トランジスタを多段に接続した再構成可能微小磁気論理素子の磁化反転が可能となる。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】回路動作の信頼性向上および設計期間の短縮化を図ること。

【解決手段】設計対象回路の配線領域内の各ネットグループ固有の始点座標から終点座標に辿り着くまでの各ネットグループ固有の配線幅の配線経路を探索する。そして、探索された配線経路間で相互に交差関係を有するネットグループの組み合わせを検出し、検出された組み合わせのネットグループがそれぞれ異なる配線層に割り当てられるように、設計対象回路に与えられた複数の配線層の中から各ネットグループに割り当てる配線層を決定し、決定された決定結果を出力する。

(もっと読む)

ノイズ解析装置

【課題】本発明の課題は、内部回路の待機時消費電力を抑制するための電源制御回路を用いて半導体集積回路内の電源接続・切断を行った際に半導体集積回路内に発生する電源ノイズを解析することを目的とする。

【解決手段】上記課題は、半導体集積回路のレイアウトの前段階で、電源制御回路を用いた該半導体集積回路の内部回路の電源の接続及び切断時に発生する電源ノイズを算出する電源ノイズ算出手段と、前記算出された電源ノイズが第一基準値以下であるか否かを判定する基準値判定手段とを有するノイズ解析装置により達成される。

(もっと読む)

基本セルおよび半導体装置

【課題】チップサイズの増大を防ぎ、かつ、電源ノイズに対する耐性が向上した基本セルを提供する。

【解決手段】基板の表面から所定の深さまでの領域に第1の導電性不純物が拡散された第1のウェル拡散層と、第1のウェル拡散層の上に設けられた絶縁膜と、絶縁膜上に設けられた第1のダミーパターンとからなる容量素子を有する。

(もっと読む)

121 - 140 / 371

[ Back to top ]