Fターム[5F064CC23]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | コンデンサ、キャパシタ (371)

Fターム[5F064CC23]に分類される特許

61 - 80 / 371

製造を容易にする設計

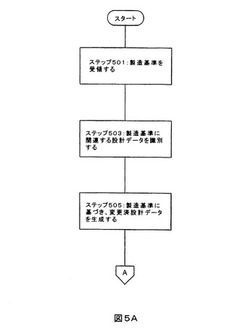

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

解析装置及び半導体装置

【課題】 本発明の課題は、複数段の電源スイッチを段階的にオンすることによって内部回路に電源供給する半導体装置において、電源供給開始から起動可能となるまでの復帰時間を短縮することを目的とする。

【解決手段】 上記課題は、複数段の電源スイッチを段階的にオンすることによって内部回路に電源供給する電源供給回路を解析する解析装置であって、前段までの電源スイッチをオン状態とし、オンすることによって発生する許容ノイズ量を超えない最大電源ノイズ量となる電源スイッチサイズを次段の電源スイッチとして決定する電源スイッチサイズ決定手段と、前記次段の電源スイッチサイズによる電源ノイズが前記オンされてから収束判定量以下となるまでの時間をオン時間間隔として決定するオン時間間隔決定手段とにより達成される。

(もっと読む)

半導体集積回路及び半導体集積回路の電源スイッチ制御方法

【課題】電源スイッチを非導通状態から導通状態に遷移させる時間を最適化できる半導体集積回路及びその電源スイッチ制御方法を提供する。

【解決手段】共通電源配線と、第1の回路と、それぞれ電源スイッチ制御信号に基づいて導通、非導通が制御され共通電源配線と第1の回路との間を並列に接続する複数の電源スイッチと、電源スイッチ制御信号と複数の電源スイッチとの間に接続され電源スイッチ制御信号が非導通状態から導通状態に遷移するときに電源スイッチ制御信号の遷移をそれぞれ異なった遅延時間だけ遅延させて複数の電源スイッチに伝え複数の電源スイッチをそれぞれ時間をずらして非導通状態から導通状態に遷移させる遅延回路と、各遅延回路の遅延時間の増減を制御する遅延時間制御部と、を備える。

(もっと読む)

品質優先回路抽出装置、品質優先回路抽出方法、品質優先回路抽出プログラム、マスク作成システム、及びレイアウト制約作成システム

【課題】レイアウト上での素子配置の規則性情報と組み合わせて、差動対回路やカレントミラー回路のようなマスク検査品質を優先する部分回路の抽出を図ること。

【解決手段】品質優先回路ネットリスト抽出装置3で抽出した品質優先回路のネットリスト情報(差動対回路、カレントミラー回路)と品質優先回路レイアウト抽出装置5で抽出した品質優先回路のレイアウト情報(行/列/アレイ構造)から、レイアウトデータに含まれる素子図形に対してマスク検査精度の優先順位を決定する。

(もっと読む)

半導体集積回路および電子回路

【課題】簡易な工程で保護ダイオードが有する寄生容量を内部回路から分離し、半導体集積回路の高速化を実現することが可能な半導体集積回路および電子回路を提供することを目的とする。

【解決手段】信号端子120と内部回路132とを接続する信号ライン134と、信号ライン134から分岐して接続されるヒューズ素子F1と、ヒューズ素子F1を介して信号ライン134と接続し、正電源VDDまたは負電源VSSが直接接続される通電端子136と、ヒューズ素子F1の通電端子136側に接続され、信号ライン134と正電源VDDまたは負電源VSSとの間をそれぞれ逆方向に接続する保護ダイオードD1、D2と、を備えることを特徴とする。

(もっと読む)

昇圧回路及び半導体装置

【課題】半導体チップのチップ面積を小さくできる昇圧回路を提供する。

【解決手段】昇圧回路100は、N個(Nは2以上の自然数)の容量素子(容量素子C0〜C3)を備える。N個の容量素子のうち第K番目(1<K<N、Kは自然数)の容量素子(容量素子C2)は第(K−1)番目の容量素子(容量素子C1)によって昇圧された第(K−1)番目の昇圧電圧を受けて、第(K−1)番目の昇圧電圧を更に昇圧した第K番目の昇圧電圧を発生して第(K+1)番目の容量素子(容量素子C3)に供給し、第N番目の容量素子の一端(出力端子OUT)から第N番目の昇圧電圧を発生する。N個の容量素子の内、少なくとも1つの容量素子(容量素子C0及びC1)は他の容量素子(容量素子C2及びC3)が形成された第1のチップ(半導体チップCHIP2)とは異なる第2のチップ(半導体チップCHIP1)に形成され、第1及び第2のチップは互いに積層されている。

(もっと読む)

ヒューズ制御回路、ヒューズ制御システム、照度センサ、近接センサ、携帯電話、デジタルスチルカメラ、および電源回路

【課題】従来のヒューズ制御回路よりも回路規模が低減されたヒューズ制御回路、照度センサ、近接センサ、携帯電話、デジタルスチルカメラ、および電源回路を提供する。

【解決手段】ヒューズ制御回路1は、ヒューズ溶断回路2がヒューズ素子F1に電流を流すとき、ノードBとヒューズ溶断検知回路3とを切断するとともに、ヒューズ溶断回路2がヒューズ素子F1に電流を流さないとき、ノードBとヒューズ溶断検知回路3とを接続する分離用素子4を備える。

(もっと読む)

半導体集積回路

【課題】少なくともロジック回路ブロックを含む半導体集積回路において、半導体集積回路の電源用パッドとロジック回路ブロックの電源ラインとを接続する電源配線、及び/又は、半導体集積回路のグランド用パッドとロジック回路ブロックのグランドラインとを接続するグランド配線の抵抗値を下げる。

【解決手段】この半導体集積回路は、半導体基板と、半導体基板上にそれぞれの層間絶縁膜を介して形成され、半導体基板に形成された複数のトランジスタに接続されて複数のトランジスタと共に少なくともロジック回路ブロックを構成する複数の配線層と、複数の配線層が形成された半導体基板上に層間絶縁膜を介して形成され、複数の配線層における最大膜厚の5倍〜20倍の膜厚を有する最上層の配線層とを具備する。

(もっと読む)

半導体装置

【課題】ノイズが高周波である場合においても、多層配線層を介してデジタル回路とアナログ回路の間でノイズが伝播することを抑制する。

【解決手段】回路分離領域40は第1回路領域20と第2回路領域30の間に位置している。回路分離領域40には複数の第1導体及び複数の第1ビアが設けられている。複数の第1導体は、電源ライン110より下層に設けられ、電源ライン110に対向しており、かつ繰り返し配置されている。複数の第1ビアは多層配線層の中に、複数の第1導体それぞれごとに設けられており、各第1導体を電源ライン110に接続している。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法

【課題】I/Oバッファ変更があった場合であっても、リワーク性を有する半導体集積回路を提供する。

【解決手段】半導体集積回路(7)のチップの外周部に沿って形成されたI/O配置領域(2)と、その外周部の内側に形成されたプリミティブブロック配置領域(3)とを具備する半導体集積回路(2)を構成する。その半導体集積回路(7)は、そのプリミティブブロック配置領域(3)は、容量セルの配置を許容する許容領域(3)と、そのI/O配置領域(2)に沿って形成され、その容量セルの配置が禁止された禁止領域(11)とを含む。

(もっと読む)

半導体装置

【課題】一つの半導体装置をボンディングオプションにより機能の異なる製品に切り替える場合に、その半導体装置で使用される内部電源の安定化容量を、それぞれの製品において最適化することができる半導体装置を提供する。

【解決手段】半導体装置10は、異なる電源電位の電圧が供給される2つのインナーリード12A、12Bに選択的にワイヤーボンディングされるボンディングオプション用パッド14と、ボンディングオプション用パッド14に接続されるインバータ16と、短絡されたソース及びドレインがインバータ16に接続され、ゲートが内部電源IVから電源電圧が出力される電源出力ライン18に接続された、内部電源IVの出力レベルを安定化させるためのNMOSトランジスタ20と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】設計基準を遵守しつつ容量値を向上しうる容量素子を有する半導体装置及びその製造方法を提供する。

【解決手段】複数の電極パターンをそれぞれ有し、積み重ねるように配置された複数の配線層と、複数の配線層の間にそれぞれ設けられ、隣接する配線層の複数の電極パターンのそれぞれを電気的に接続する複数のビア部と、複数の配線層及び複数のビア部の間隙に形成された絶縁膜とを有する容量素子を有し、ビア部は、電極パターンの中心に対して、電極パターンの延在方向と交差する方向にずらして配置されており、電極パターンは、ビア部が接続された部分において線幅が太くなっており、隣接する電極パターンとの間の間隔が狭まっている。

(もっと読む)

半導体装置

【課題】効率的にかつ確実にブロー状態に設定しかつ通常動作モード時に、確実に、プログラム情報を保持する所望の耐圧特性を有するキャパシタ型アンチヒューズを実現する。

【解決手段】プログラムモード時と通常動作モード時とで、キャパシタ型アンチヒューズに対する電圧印加極性を変更する。

(もっと読む)

プリミティブセル及び半導体装置

【課題】従来のプリミティブセルでは、電源配線及び接地配線により構成される電流経路のループが大きく、当該電流経路のループに起因して発生するEMIノイズを十分に低減することができない問題があった。

【解決手段】本発明にかかるプリミティブセルは、内部回路10と、内部回路10に電源電圧を印加する電源配線12と、内部回路に接地電圧を印加する接地配線11と、を有し、電源配線12と接地配線11とがセルの外周辺のうちの一辺に偏在して配置される。

(もっと読む)

半導体装置

【課題】 セルサイズが小さく、かつ配線接続の自由度が向上できるスタンダードセルを用いた半導体装置を提供する。

【解決手段】 半導体装置はメモリ回路と周辺回路を備え、周辺回路を分割した回路ブロックのそれぞれを、同じ高さを有した矩形で、それぞれが基本論理回路として機能するように構成された複数のスタンダードセルを、同じ高さになるように配置したセルブロックとして構成し、スタンダードセルへの入力信号配線が、メモリセルトランジスタと容量下部電極を接続する容量コンタクトパッド配線を用いて配線される。

(もっと読む)

集積回路装置及び電子機器

【課題】アナログ処理の特性の向上を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、信号が入力されるパッドPANTと、パッドPANTを介して入力される信号についてのアナログ処理を行うアナログ回路と、アナログ回路の信号入力ノードとパッドPANTとの間に設けられるキャパシターCAを含む。パッドPANTとキャパシターCAの一端とが、最上層金属層ALEで形成されるパッド配線LNPにより接続される。

(もっと読む)

半導体装置

【課題】電源配線やグランド配線に流れる電流の周波数が上がってもインピーダンスが上がるのを抑えられる半導体装置を提供すること。

【解決手段】トランジスタ20、21の近傍に配線された電源配線11a及びグランド配線11cを備え、電源配線11a及びグランド配線11cは、それぞれ、分割した構造となっており、所定間隔をおいて一方向に配線された複数本の分割配線11a、11cよりなる。

(もっと読む)

半導体集積回路のセル自動配置方法、装置、及びプログラム

【課題】製造工程の異なるセルを混在して配置する場合に、面積を大きくせずに配置する半導体集積回路のセル自動配置方法、自動配置装置、及びそれらのプログラムを提供する。

【解決手段】複数種類のセルの内、一種類のセルに同一種類のセルが隣接配置可能であり、異なる種類のセルの隣接配置が不可能な大きさの第1の外形を設定し、上記その他の種類のセルには、第1の外形が設定されるセルを含めセルの種類に係わらずセルを隣接配置することが可能なより大きい外形を設定するセル外形設定工程と、セル外形設定工程で設定した外形を有するセルを用いて複数種類のセルを自動配置するセル自動配置工程と、を備える。

(もっと読む)

T−コイル回路網設計を生成する方法およびT−コイル回路網

T−コイル回路網を備える回路設計を生成する方法の1つの実施形態は、インダクタのインダクタンスおよびT−コイル回路網の寄生ブリッジ容量を決定するステップ(305−340)を含み得る。寄生ブリッジ容量は、T−コイル回路網の出力に結合された負荷の寄生容量に依存する負荷容量基準と比較され得る(345,355)。T−コイル回路網の出力に結合された回路設計の静電放電(ESD)保護の量、または、T−コイル回路網のインダクタのパラメータが、寄生ブリッジ容量と負荷容量基準との比較に従って、選択的に調整され得る(350,360)。インダクタのインダクタンスと、静電放電保護の量と、インダクタの巻線の幅とを特定可能な回路設計が出力され得る(365)。  (もっと読む)

(もっと読む)

スパイラルコイルの配線構造および集積回路装置

【課題】 第1インダクターおよび第2インダクターを有する3ポートのスパイラルコイルにおける特性の対称性を確保し、かつ、3つのポートを、スパイラルコイルの中心を通る直線を基準として同じ側に配置すること。

【解決手段】 第1ポートと第3ポートとの間に設けられる第1インダクターと、第2ポートと前記第3ポートとの間に設けられる第2インダクターとを含むスパイラルコイルの配線構造であって、スパイラルコイルの中心を通る直線を基準として、前記第1ポートおよび第2ポートは同じ側に配置され、第1ポートから引き出される第1配線と、第2ポートから引き出される第2配線とが、スパイラルコイルの中心を通る直線を基準として、第1ポートおよび第2ポートの側において交差することによって第1交差部が設けられる。

(もっと読む)

61 - 80 / 371

[ Back to top ]