Fターム[5F064CC23]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | コンデンサ、キャパシタ (371)

Fターム[5F064CC23]に分類される特許

21 - 40 / 371

半導体装置及び半導体装置の製造方法

【課題】情報が読み取られることを防止する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置10は、コンタクト15aを有する第2絶縁層15と、コンタクト17aを有する第3絶縁層17と、第2絶縁層15と第3絶縁層17との間に配置された第2配線層16と、を備え、コンタクト15aとコンタクト17aとの間の第2配線層16の部分には配線が配置されておらず、コンタクト15aとコンタクト17aとの間の距離は、コンタクト15a又はコンタクト17aと、第2絶縁層15及び第3絶縁層17及び第2配線層16内の他のコンタクト又は配線との間の距離よりも短い。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

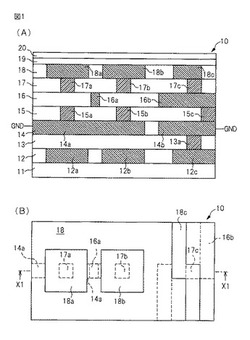

半導体集積回路装置

【課題】半導体集積回路装置において、レイアウトの面積効率の低下を抑制可能となる、マルチハイトセルのレイアウト構造を提供する。

【解決手段】標準論理セル10は、電源配線または接地配線となるメタル配線12を共有するようにY方向に隣接して配置された第1および第2回路領域A1,A2を備えている。X方向において、第1回路領域A1の両端部の位置x1a,x1bと第2回路領域A2の両端部の位置x2a,x2bとは、少なくともいずれか一方が異なっている。すなわち、標準論理セル10の外形形状CFは、第1および第2回路領域A1,A2の外形形状が矩形であるにもかかわらず、非矩形となっている。

(もっと読む)

電源ノイズ解析方法

【課題】簡易モデルを使用しても、電源ノイズを高精度かつ高速で解析することのできる電源ノイズ解析方法を提供する。

【解決手段】実施形態の電源ノイズ解析方法は、スイッチング部モデル11と非スイッチング部モデル12とを備える簡易モデル1を用い、半導体集積回路のトグル率の時間軸上の変化を表すトグル率時系列データを生成するステップと、トグル率時系列データにもとづいて簡易モデル1の容量CL、Cnswの容量値の時間軸上の変化を表す容量値時系列データを生成するステップと、簡易モデル1および容量値時系列データを用いて電源ノイズの解析を行うステップとを有する。電源ノイズの解析を行うステップは、スイッチング部モデル11のスイッチSWのスイッチング区間ごとに容量値時系列データから該当区間の容量値を取得し、前区間の過渡解析の結果を引き継ぎながら次区間の過渡解析を実行する。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップサイズを縮小する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、半導体集積回路のレイアウト設計を階層別に行う階層レイアウト設計における上位階層において、上位階層の下の階層で配置配線が行われる所定の機能を備えた階層ブロックが配置される領域であって、空きユニットセル配置領域3と階層ブロック用のユニットセル配置領域4とを含む階層ブロック配置領域2を、チップ領域1に設定し、チップ領域1における階層ブロック配置領域2を包囲する周辺領域5のユニットセル配置領域、および、階層ブロック配置領域2内の空きユニットセル配置領域3を用いて、配置配線を行う。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置の製造方法

【課題】ロジック回路を含む半導体装置に関し、処理時間を短縮し製造コストを低減する。

【解決手段】ロジック回路の形成領域(114)は、所定の精度で光近接補正処理された第1領域(114b,170)と、所定の精度より低い精度で光近接補正処理された第2領域(114a,180)とを備える。特に第1領域(114b,170)は、トランジスタとして動作するゲート配線(172)を有し、第2領域(114a,180)は、トランジスタとして動作しないダミーレイアウト(182)を有する。

(もっと読む)

スイッチング電源回路方式判定処理方法,CAD装置およびCADプログラム

【課題】 CAD装置で,スイッチング電源回路の方式を自動的に判別することを目的とする。

【解決手段】 CAD装置1は,判別対象とするスイッチング電源回路が配置されている基板に実装される部品およびネットの情報を示す実装CAD情報2,ならびに前記基板に配置される各部品の部品種別,部品内部の透過接続情報およびピン属性を示す部品情報3をもとに,スイッチング電源回路から開始かつ終了する経路を抽出し,該経路に接続する部品および接続関係を示すスイッチング電源回路経路情報14を生成する経路情報抽出部13と,スイッチング電源回路の経路に接続する部品および接続関係にもとづいてスイッチング電源回路の方式を定める条件をもとに,スイッチング電源回路経路情報14から,判定対象のスイッチング電源回路の方式を判定する回路方式判定部15とを備える。

(もっと読む)

プログラマブルLSI

【課題】低消費電力で、且つ、動的コンフィギュレーションにも対応できる高速なコンフィギュレーションを可能とし、起動するための時間が短いプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントと、複数のロジックエレメントに入力するためのコンフィギュレーションデータを記憶するメモリエレメントと、を有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有し、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更し、メモリエレメントは、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードと、を有する記憶素子を用いて構成する。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体集積回路の設計方法

【課題】設計フローの負荷を増大させることなく、それぞれの回路モジュールに必要十分な容量セルを、それぞれの回路モジュールに近接配置することができる半導体集積回路の設計方法を提供する。

【解決手段】本発明は、それぞれが複数の論理セルを含む複数の回路モジュールからなる半導体集積回路の設計方法であって、複数の回路モジュールのそれぞれの、複数の論理セルおよび複数の論理セルの端子間の接続の情報を記述するネットリストに、複数の論理セルに電源を供給する電源配線間に接続されるセルであり、複数の論理セルのいずれとも独立で、かつ、複数の論理セルの端子と接続される端子を持たない容量セルの記述を追加し、複数の論理セルおよび複数の容量セルのレイアウトデータが格納されたセルライブラリを備えた設計支援システムを利用して、回路モジュールのそれぞれに対応する、複数の論理セルおよび容量セルを配置する配置領域を設定し、複数の論理セルおよび容量セルを対応する配置領域内に配置する工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】銅を主成分とする配線層を有し、かつヒューズの切断によって特性の悪化を招くことのない半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、銅を主成分とするメタル配線34と、メタル配線34よりも上層に形成された最上層配線5と、メタル配線34と最上層配線5との間を接続するためのプラグ9が形成されるプラグ形成層10に少なくとも一部が形成され、銅以外の金属材料を主成分とする導電性材料で形成されたヒューズ膜4とを含む。

(もっと読む)

半導体集積回路、半導体チップ、及び半導体集積回路の設計手法

【課題】容易な設計により、小規模な構成でクロックスキューを抑制させる半導体集積回路を提供する。

【解決手段】ラッチ回路31〜316のデータ入力端子とデータビットの供給元PDとの間に、クロック信号CLLの供給元PCD及びラッチ回路のクロック入力端子間のクロック信号経路中に含まれている論理素子の個数と同一数だけ当該論理素子を直列に接続してなる第1遅延部51,52と、クロック信号経路中の配線の配線長に対応した配線遅延時間と同一長の遅延時間を有する第2遅延部53と、を備える。

(もっと読む)

レイアウト設計装置

【課題】アナログレイアウト設計の自動化による設計工期の短縮を図ることが可能なレイアウト設計装置を提供すること。

【解決手段】レイアウト設計装置21は、回路データ24の中から特性を一致させる必要があるトランジスタ、抵抗、容量素子群を抽出し、トランジスタ、抵抗、容量素子群の接続関係に基づいてトランジスタ、抵抗、容量素子群に含まれる複数のトランジスタ、抵抗、容量素子によって構成される所定の機能を有する回路、たとえば差動回路、差動負荷回路およびミラー回路を特定する。そして、特定された回路の種別に応じてレイアウト制約30を生成し、レイアウト制約30に基づいて配置配線を行なう。したがって、アナログ回路のレイアウト制約30を自動的に付加することができ、アナログレイアウト設計の自動化による設計工期の短縮を図ることが可能となる。

(もっと読む)

21 - 40 / 371

[ Back to top ]