Fターム[5F064EE01]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249)

Fターム[5F064EE01]の下位に属するFターム

配線の自動配置 (657)

配線の最適化 (421)

グラフ理論の応用 (5)

単位セル、ブロック内(上)の配線 (232)

配線長 (567)

配線幅 (593)

メッシュ状、格子状配線 (332)

配線スペース (344)

配線数、配線密度 (338)

配線の方向、角度 (398)

配線の位置、座標 (294)

配線の配列、ピッチ (319)

配線の末端 (40)

多層配線 (2,699)

Fターム[5F064EE01]に分類される特許

1 - 10 / 10

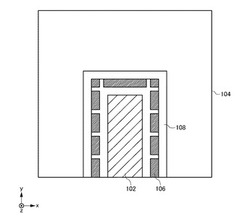

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

半導体回路装置

【課題】配線が微細化された半導体回路装置でも、銅(Cu)からなる配線間ブリッジ等による配線ショートの発生を予防することを目的とする。

【解決手段】隣接する配線との最小スペース幅13によって、設けられる配線幅12の最大値を規定することにより、配線が微細化された半導体回路装置でも、銅(Cu)からなる配線間ブリッジ等による配線ショートの発生を予防することができる。

(もっと読む)

集積回路内の構造的特徴部の形成方法

【課題】集積回路をより容易に製造できるように設計する。

【解決手段】集積回路が、複数の別々にプリントされるパターン層から1つのリソグラフ層を形成する工程段階を含むリソグラフ工程で形成される。集積回路内には、少なくとも2つのマッチされたデバイスを含む回路が形成されており、これらのマッチされたデバイスの性能特性の整合がずれると、その回路の性能が低下する。マッチすべきデバイスの機能的コンタクト(構造的特徴部)を強制的に同じパターン層に割り当てるようにするためのダミーコンタクト32(構造的特徴部)が回路デザイン中に設けられている。これにより、コンタクトの位置および/またはサイズのデバイス間でのバラツキが低減される。

(もっと読む)

マスクプログラム可能なロジックデバイスをプログラムする方法およびその方法によってプログラムされたデバイス

【課題】プログラム可能なロジックデバイスをプログラムする方法を提供すること。

【解決手段】マスクプログラム可能なロジックデバイス(MPLD)に対するユーザーのロジック設計は、互換性を有するユーザープログラム可能なロジックデバイス(UPLD)上で設計されMPLDに移行され得る、または直接MPLD上で設計され得る。設計がUPLD上でなされる場合には、目標のMPLDの制約(例えば、デバイスの間の差異)が考慮され、その結果、移行は成功する。設計が直接MPLD上でなされる場合には、その設計を試験のためにUPLDに移行することをユーザーが意図するときに、互換性を有するUPLDの制約が考慮される。これは、ロジック設計のUPLDとMPLDとの間で行き返りの移行が意図される場合にのみ、特徴の一致が使用され得ることを意味する。移行を助長するためにデバイスのペアの間の固定されたマッピングが生成され得る。

(もっと読む)

半導体集積装置およびフューズ回路

【課題】フューズが占める面積を減少できる半導体集積装置のフューズ回路を提供する。

【解決手段】複数のフューズを含む第1アップフューズブロックと前記第1アップフューズブロック内のフューズ数より少ないフューズからなる第1ダウンフューズブロックとを有する第1フューズブロック;および前記第1ダウンフューズブロック内のフューズ数と同一数のフューズからなる第2アップフューズブロックと前記第1アップフューズブロック内のフューズ数と同一数のフューズからなる第2ダウンフューズブロックとを有する第2フューズブロックを備える。

(もっと読む)

半導体装置の作製方法

【課題】また、従来のCADツールによる半導体装置の設計図を用いる場合、インクジェット装置で形成できるパターンが限られるため、半導体装置の回路の中には、そのまま転用することができない回路も生じる恐れがある。

【解決手段】インクジェット装置で吐出して描くことの可能な基本パターンを複数用意し、それらを組み合わせて所望の集積回路のレイアウトを行う。得られたレイアウトを基にして露光マスクを形成する。露光マスクを用いて露光を行った後、現像して液滴の径よりも幅の細い露光領域にレジスト膜を残存させる。そして、被処理表面の露呈部分に対して撥液処理を行った後、レジスト膜上に材料液滴を滴下する。液滴吐出法により選択的に吐出を行い、ドット径よりも幅の細い配線を形成する。

(もっと読む)

ベース半導体チップ、半導体集積回路装置及びその製造方法

【課題】半導体基板における各機能ブロックの配置を容易に確認することが可能で且つ機能ブロックを選択的に組み合わせ且つ分割することが可能で、各機能ブロック同士の接続の自在な組み替えが可能な半導体集積回路装置を実現できるようにする。

【解決手段】半導体集積回路装置は、半導体基板における所定の領域に互いに独立して形成され且つ信号を入出力するパッド22をそれぞれ有する複数の機能ブロック21を含むベース半導体チップ20と、パッド22と接続され且つ切断可能に形成された複数の配線31とを備えている。各機能ブロック21間における信号の入出力は、各配線31を介して行う。

(もっと読む)

半導体装置

【課題】配線領域の面積が小さく、かつ信号間の特性のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体記憶装置では、最も長い信号線5のグループをツイスト配線方式で構成し、中間の長さの信号線5のグループをシールド配線方式で構成し、最も短い信号線5のグループを単独配線方式で構成する。したがって、全体として、信号波形の劣化の防止とレイアウト効率の向上を両立させることができる。

(もっと読む)

半導体集積回路

半導体ウエハ上に複数存在する半導体集積回路において、機能回路(3)と、複数のパッド(4)と、パッド(4)と電気的に接続しプローブカード(7)のバンプと接触する配線(8)とを備え、少なくとも2つの配線(8a),(8b)が、互いに接触することなく、1つのバンプ(6)とバンプ領域以外の領域で同時に接触することで、ウエハレベルバーンインを実施する。これにより、チップ面積を縮小化しても、ウエハレベルバーンインが実施できる。  (もっと読む)

(もっと読む)

半導体集積回路およびその設計方法

【課題】 半導体プロセスのうち金属配線形成時のプラズマ工程において発生するアンテナダメージを防止する事が可能な半導体集積回路を提供する。

【解決手段】 第2導電型ウェル11上に第1導電型拡散層21を設け、MOS型トランジスタのゲート電極13と第1導電型拡散層21をコンタクトホール31、32とCuからなる金属配線41を介して接続する。さらに、第1導電型ウェル12上に第2導電型拡散層22を設け、MOS型トランジスタのゲート電極13と第2導電型拡散層22をコンタクトホール33、34とCuからなる金属配線42を介して接続し、ゲート電極13と第2導電型ウェル11との間のダイオード1を、ゲート電極13と第1導電型ウェル12との間にダイオード2をそれぞれ設置する。これにより、MOS型トランジスタのゲート電極に発生するアンテナダメージを防止する。

(もっと読む)

1 - 10 / 10

[ Back to top ]