Fターム[5F064EE14]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線スペース (344)

Fターム[5F064EE14]に分類される特許

1 - 20 / 344

設計支援装置

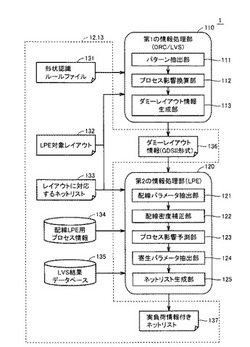

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

半導体装置

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

レイアウト設計方法、レイアウト設計プログラム及びレイアウト設計装置

【課題】被クリップセルとクリップセル間の配線引き回しを抑え、配線引き回しに起因した不具合を回避する。

【解決手段】レイアウト設計において、ネットリストを用い、被クリップセルと、その被クリップセルに接続されるクリップセルとを抽出し(ステップS1)、抽出された被クリップセルとクリップセルとを関連付けた関連付け情報を生成する(ステップS2)。そして、生成された関連付け情報に基づき、被クリップセルとクリップセルとを隣接させる等して一体で配置し(ステップS3)、配置された被クリップセルとクリップセルとを配線で接続する(ステップS4)。

(もっと読む)

レイアウト修正・ライブラリセル置換モジュール及び半導体装置設計用EDAツール

【課題】効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供する。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

(もっと読む)

半導体集積回路の設計方法および設計装置

【課題】無駄領域を削減するとともに配線混雑の発生も抑制できる回路設計方法を提供する。

【解決手段】データフローを参照し、同じタイミングで動作するレジスタ群を終点として、それらの終点レジスタから同じタイミングで動作する前段方向の始点レジスタ群までを一つの集まりとしてクラスタ化する。クラスタ化したクラスタをさらに複数のクラスタに分割する場合(ST207)、分割後のクラスタ同士が共有する始点レジスタを複製して(ST235)、分割されたクラスタ同士で始点レジスタを共有しないようにする。

(もっと読む)

レイアウト設計方法、レイアウト設計システムおよびプログラム

【課題】チップ上のマクロ間の間隔を適正化する。

【解決手段】チップ上の隣接する2つのマクロに挟まれた領域のうち、配線リソース占有率が、所定の目標占有率未満の領域を挟むマクロの少なくとも一方を移動し、配線リソース占有率を上げる第1のステップと、前記第1のステップの実行後、前記チップ上の隣接する2つのマクロに挟まれた領域のうち、配線リソース占有率が所定の目標占有率を超えている領域を挟むマクロの少なくとも一方を移動し、配線リソース占有率を下げる第2のステップと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体集積回路の配線方法、半導体回路配線装置および半導体集積回路

【課題】パターン配置の手順を複雑化することなく、電源配線パターンの配線抵抗による電圧降下を抑制可能で、信号配線パターンの信号伝搬遅延を低減可能とする。

【解決手段】半導体集積回路の配線方法は、主に信号配線パターンが形成される第1の層とは別個の第2の層に、空き領域をそれぞれの間に挟んで複数列の電源配線パターンを規則的に配置し、前記空き領域の幅を前記複数列の電源配線パターン中の最小幅の電源配線パターンの幅よりも狭くする。次に、前記第2の層における2列分以上の前記空き領域のそれぞれに、隣接する両側の前記電源配線パターンに接触しないように、前記第1の層と電気的に導通した前記信号配線パターンを配置する。次に、前記空き領域に残存するパターン配置可能領域の少なくとも一部に、前記電源配線パターンを再配置する。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

半導体装置

【課題】2つの入力端子の配置形態を工夫することにより配線層の増設スペースを確保しスタンダードセルの原価低減を図る。

【解決手段】入力端子34bはゲート配線2bに接続され、入力端子34cはゲート配線2cに接続される。また、入力端子34b、34cは、Y方向に互いに近接して配置され、入力端子34bの第2コンタクト配線4bは、第1コンタクト配線3bと隣接し、且つ該第1コンタクト配線3bに対しX方向に延在する。入力端子34cの第2コンタクト配線4cは、第1コンタクト配線3cと隣接し、且つ該第1コンタクト配線3c対して第2コンタクト配線4bとは逆のX方向に延在する。即ち、入力端子34bの第1コンタクト配線3bと入力端子34cの第2コンタクト配線4cとはY方向に互いに対向して配置され、入力端子34bの第2コンタクト配線4bと入力端子34cの第1コンタクト配線3cはY方向に互いに対向して配置される。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】配線の遅延特性のばらつきを抑制すること。

【解決手段】回路設計支援装置1は、設定部1aと生成部1bとを有している。設定部1aは、半導体集積回路モデル2の層2a、2bそれぞれに、積層方向および面方向に隣接するユニット3の配線方向が互いに異なる方向に配線が生成される複数の矩形のユニット3を設定する。生成部1bは、ユニット3の境界で異なる層のユニット3に跨る配線を生成する。

(もっと読む)

半導体装置、液晶ディスプレイパネル及び携帯情報端末

【課題】外部駆動端子の狭ピッチ化に充分答えることができる半導体装置を提供する。

【解決手段】長方形の半導体基板の一方の長辺に沿ってそれぞれ配置された、複数の外部駆動端子(3A,3B,3C)、対応する前記外部駆動端子に接続されたESD保護回路(4A,4B,4C)、及び対応する外部駆動端子に接続された出力回路(5)を備え、複数個の外部駆動端子は、Y方向に沿って複数列であるn列で配置され、各列の間で外部駆動端子の位置が相互にずらされた千鳥状配置を有し、前記出力回路は、Y方向に交差するX方向にn個の外部駆動端子毎に対応して一列に配置されるn個の出力ユニット(5A,5B,5C)を有する。n列の千鳥状配置によって外部駆動端子を狭ピッチにできる。n個の外部駆動端子毎に対応される出力回路にはX方向に一列で配置されたn個の出力ユニットを配置することにより、n個分の出力ユニットの幅を1個分の幅に集約できる。

(もっと読む)

半導体装置

【課題】異なる電位に対応する複数の外部電源配線間に間隔部分を有する半導体装置に対して,所定電源ピン数のテスタにより短絡試験を行う場合において,より多くの半導体装置の短絡試験を同時に行うことができる半導体装置を提供する。

【解決手段】半導体装置は,コア回路と,該コア回路の周囲に配置され且つコア回路と外部装置間の信号を入出力する複数の入出力回路と,複数の入出力回路のうちの第一の入出力回路グループに第一の電位の電源を供給する第一の電源配線と,複数の入出力回路のうちの第二の入出力回路グループに第二の電位の電源を供給し且つ第一の電源配線と間隔をあけて直列に延びる第二の電源配線と,第三の電位の電源を供給する第三の電源配線とを備え,第三の電源配線から延びる配線パターンが,第一の電源配線と第二の電源配線間の間隔部分に設けられる。

(もっと読む)

1 - 20 / 344

[ Back to top ]