Fターム[5F064EE42]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766) | 配線抵抗 (638)

Fターム[5F064EE42]に分類される特許

61 - 80 / 638

半導体集積回路装置

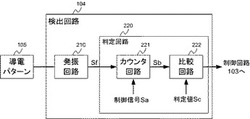

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出する精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に形成された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンに接続され、導電パターンの回路定数により決定される発振周波数で発振する発振回路と、発振回路の発振周波数が事前に設定された範囲に含まれるか否かを判定し、発振周波数が事前に設定された範囲に含まれない場合に、導電パターンに改変が加えられたことを検出する検出回路とを有することを特徴とする半導体集積回路装置が提供される。

(もっと読む)

電圧降下解析装置、および、電圧降下解析方法

【課題】電圧降下解析の実行時間を短縮することが可能な電圧降下解析装置を提供する。

【解決手段】電圧降下解析装置の電流解析部は、素子に流れる電流を解析し、素子に流れる電流の電流情報を出力する。電圧降下解析部は、素子の接続、素子の配置、および素子に接続された電源配線の情報を含む回路配置情報と、電流情報と、に基づいて、素子の電圧降下を解析し、素子の電圧降下の電圧降下情報を出力する。コーナ選択部は、複数のコーナ情報を含むコーナ情報リストから素子のコーナ情報を選択する。電圧降下補正部は、電圧降下情報と、選択されたコーナ情報と、コーナ情報と電圧降下情報の補正量との関係を規定する電圧降下補正情報と、に基づいて、電圧降下情報を補正した補正後電圧降下情報を出力する。

(もっと読む)

半導体集積回路の設計方法

【課題】 半導体集積回路の電源EM及びスタティックIRドロップの解析と電源補強設計を改善する。

【解決手段】 一つの実施形態の半導体集積回路の設計方法では、電源配線のEM解析を行い、EM解析でEMエラーが発生した場合、EMエラーとなるレイヤ及び座標をチェックしてリストを格納し、半導体集積回路の抵抗網を抽出し、EMエラーとなるレイヤ及び座標を含む抵抗セグメントを全て削除してIRドロップ値が許容値を満足するかの第1の判定を行い、記第1の判定でIRドロップ値が許容値を満足する場合、EMによって半導体集積回路が動作不良とならない抵抗セグメントをレイアウトデータから削除する。

(もっと読む)

タイミング解析方法、プログラム、及びシステム

【課題】IRドロップの影響を考慮して半導体集積回路のタイミング解析を行うこと。

【解決手段】タイミング解析方法は、(A)遅延変動率と電圧変動との関係を示す遅延電圧関数を算出するステップと、(B)IRドロップによる電圧変動と距離との関係を示す電圧距離関数を算出するステップと、(C)遅延電圧関数と電圧距離関数を組み合わせることによって、IRドロップによる遅延変動率と距離との関係を示す遅延距離関数を算出するステップと、(D)距離に依存するOCV係数を、遅延距離関数を用いることによって補正するステップと、(E)補正後のOCV係数を用いて、対象回路のタイミング解析を実行するステップと、を含む。

(もっと読む)

半導体装置

【課題】高い比精度が要求される複数のトランジスタの特性ばらつきを低減する。

【解決手段】本発明の半導体装置は、半導体基板上に配置されたトランジスタTr1と、半導体基板上で見たキャリアのドリフト方向がトランジスタTr1のキャリアのドリフト方向と同じ方向となる向きに配置されたトランジスタTr2と、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51b同士を接続する拡散層51cと、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51bまたはその拡散層同士を接続する拡散層51cの表面に接続され、拡散層51a,51bに給電するためのコンタクトプラグ61と、を備える。

(もっと読む)

半導体チップおよびその設計方法

【課題】設計期間が短く、面積効率が高く、電源配線における電圧降下が小さな半導体チップと、その設計方法を提供する。

【解決手段】この半導体チップは、複数の電源ドメインD1〜D4に分割された内部回路2を備える。互いに異なる電流駆動能力を有する複数種類のレギュレータR1,R2を予め準備しておき、各電源領域毎に、当該電源領域の最大負荷電流を供給するために必要なレギュレータの種類と数を選択し、選択した1または2以上のレギュレータによって当該電源領域用の電源回路を構成する。したがって、設計期間が短くて済む。

(もっと読む)

情報処理装置、プログラム、および設計支援方法

【課題】設計対象の集積回路内での回路特性のばらつきに伴う遅延時間の変動を反映したタイミング解析技術を提供する。

【解決手段】情報処理装置は、複数の回路素子を含む対象経路の信号伝搬時間を変化させる物理特性値を所定の変動範囲で複数個発生させる物理特性値発生部と、発生させた物理特性値にしたがって、回路素子を通る信号の遅延時間を算出する素子遅延算出部と、信号の遅延時間を基に対象経路の信号伝搬時間を算出する伝搬時間算出部と、を備える。

(もっと読む)

半導体装置、および、配線設計方法

【課題】チップサイズを縮小し、再配線層の配線を容易にすることが可能な半導体装置を提供する。

【解決手段】略矩形のLSI基板1の上面に、パッド電極4a1、4a2、4c1を被覆する絶縁膜3a、3bが設けられ、前記絶縁膜3b上に、前記パッド電極4a1、4a2、4c1の何れかに接続された第1のコンタクト配線7a1、7a2、7c、および前記第1のコンタクト配線7a1、7a2に接続された再配線8b1、8b2が設けられ、第1の再配線エリア3上に設けられたボール電極2b、2cと、第1のパッド電極4c1が上面の端部に設けられたLSIコア1a3と、前記第1のパッド電極4c1に接続された第2のコンタクト配線9b1に接続された配線層6b1と前記パッド電極4a1、4a2のうちの第2のパッド電極4a1とに接続された第3のコンタクト電極9b2が形成され、前記LSIコア1a3に隣接した第2の再配線エリア1a2、とを有する。

(もっと読む)

半導体装置のシミュレーション方法及び装置

【課題】電気特性と熱特性の相互の影響を反映した電気-熱連携解析を短い計算時間で実行し、正確な解析結果を得る半導体装置のシミュレーション方法及び装置を提供する。

【解決手段】まず電気特性解析を実行する(ステップS1)。次に電流特性とチップ損失特性の平均化を実行する(ステップS2)。そしてモジュールの3次元形状モデルを作成し、第1の平均化式により得た平均化した電流値を3次元形状モデルの端面に設定してジュール損失解析を実行する(ステップS3)。そして上記ジュール損失解析と第2の平均化式で算出したチップ損失の平均値とを用いて発熱量が等しく時間ステップの長い熱解析特性データを得る(ステップS4)。温度変化が一定値以上に達した時点で電気特性解析のジャンクション温度を再設定し(ステップS5)、以降、電気特性解析から平均化、熱解析までの解析フローを繰り返して装置動作時の温度特性を得る(ステップS11〜S15)。

(もっと読む)

半導体装置

【課題】電源配線と接地配線とを有する半導体装置において、配線の一部における電圧ドロップや、電圧ドロップに伴うマイグレーションの発生を抑制することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面に沿うように層状に広がる電源シート状配線PPWRと、主表面に沿うように、主表面に交差する方向に関して電源シート状配線と一定の距離を隔てて層状に広がる接地シート状配線PGNDと、上記主表面上に形成され、主表面内の一の方向に延在する電源配線PWRと、主表面上に形成され、一の方向に沿う方向に延在し、電源配線PPWRと一定の距離を隔てて形成された接地配線GNDとを備える。上記電源シート状配線PPWRは、電源配線PWRと電気的に接続されており、接地シート状配線PGNDは、接地配線GNDと電気的に接続されている。

(もっと読む)

半導体装置

【課題】面積の増加を抑えつつ、ヒューズ構造体のデータの保持量を増加する。

【解決手段】半導体装置100は、基板(不図示)上に形成されたヒューズ構造体120を含む。ヒューズ構造体120は、第1の配線(122)および第2の配線(124)と、これらを接続するビア123とから構成された電気ヒューズ121と、一端がビア123の側方にビア123に接続して形成された抵抗配線128と、を含む。電気ヒューズ121のビア123は、基板の積層方向において、第1の配線(122)との接続箇所から抵抗配線128との接続箇所までの間に、面内方向の断面積が第2の配線(124)との接続箇所から抵抗配線128との接続箇所までの面内方向の断面積よりも小さい箇所を有する。

(もっと読む)

基板ノイズ解析装置

【課題】 本発明の課題は、被ノイズ回路において影響を受けるノイズの大きさに基づいて効率的に基板ノイズ解析を行うことを目的とする。

【解決手段】 上記課題は、導体集積回路の回路ブロック毎に該回路ブロックの回路データを用いてノイズ源解析を行い、各周波数と該周波数に対するノイズ量とを対応させたノイズ源情報を出力するノイズ源解析手段と、回路ブロック毎に該回路ブロックの回路データを用いて各周波数に対して出力ノードから出力される該周波数の振幅をノイズの影響の大きさを示す感度として解析するノイズ感度解析を行い、各周波数と該周波数に対する感度とを対応させたノイズ感度情報を出力するノイズ感度解析手段と、前記ノイズ源情報と前記ノイズ感度情報とに基づいてノイズを受ける被ノイズ回路の動作に影響を与える周波数成分を特定し、該ノイズ源情報から該周波数成分を抽出するノイズ源情報抽出手段とを有する基板ノイズ解析装置により達成される。

(もっと読む)

半導体集積回路装置

【課題】制御信号の系統を整理して、不定信号伝播防止回路等の検討漏れの危険性を回避し、さらに、自動化ツールへの搭載へ向けた検討を容易にし、また、チップ内部での電源遮断制御を容易化することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、各独立した電源領域AreaA〜AreaIごとに電源遮断の優先順を設け、優先順の高い回路がONしている場合にはそれより優先順の低い電源領域はOFFにできないという規則を設けて、設計方法の容易化を図る。また、各独立した電源領域AreaA〜AreaI内において、さらに別の電源を印加できる領域を設け、その領域に中継バッファ(リピータ)やクロックバッファ、情報退避用の情報保持ラッチを集積する。レイアウト上は、電源線の電流を分散させる目的でセルがロウ方向に並ぶ方向と垂直な方向にまとめてレイアウトすればよい。

(もっと読む)

電源回路解析装置,電源回路解析プログラムおよび電源回路解析方法

【課題】電源回路解析を、高速かつ少ないメモリ使用量で高精度に行なえるようにする。

【解決手段】解析対象回路における電源回路の解析対象領域を複数の分割領域に分割する分割部11と、この分割部11によって分割された各分割領域での消費電流値と各分割領域で上下層の電源配線を接続すべく各層間に形成されたビアのホール数とに基づき電源回路を分割領域毎に解析する解析部12とをそなえる。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】RCで鈍る出力電圧を再現し、遅延誤差を抑制すること。

【解決手段】電流テーブル群は、セルへ与える入力電圧の変化開始時からの複数の経過時間の各経過時間でのセルの出力電圧値をセルごとに保持し、設計支援装置がアクセス可能な記憶装置に記憶されている。設計支援装置は、設計対象回路の回路情報の中から選ばれた対象セルに関する各経過時間での出力電圧値を対象セルに基づいて抽出する。設計支援装置は、Vds(出力電圧)<Vgs(入力電圧)−Vth(ゲート閾値電圧)であるVdsの経過時間を補正対象の経過時間に決定する。設計支援装置は、補正対象の経過時間に対象セルの出力側の時定数を加算することにより、該経過時間を補正する。設計支援装置は、補正後の経過時間ごとの出力電圧値と補正対象に決定されなかった経過時間ごとの出力電圧値とを出力する。

(もっと読む)

回路シミュレーション方法および回路シミュレーション装置

【課題】精度の高い回路シミュレーションを実行する回路シミュレーション方法を提供する。

【解決手段】ゲートレベルでの電圧変動解析ステップを実行する(ステップS2)。ゲートレベルでの電圧変動解析ステップは、チップTP全体に対して実行する。そして、次に、電圧変動解析ステップに従う電源電圧および接地電圧(Vss)の電圧波形を取得するステップを実行する(ステップS4)。次に、トランジスタレベルでの信号解析ステップを実行する(ステップS6)。トランジスタレベルでの信号解析解析ステップは、チップTP全体よりも範囲の狭い例えば、すべてではない、1つ又はそれ以上の機能モジュールに対して実行する。そして、信号解析ステップに従う信号解析結果を取得するステップを実行する(ステップS8)。

(もっと読む)

パワーグリッド最適化

【課題】導電材料の第1の層と導電材料の第2の層とを備える集積回路におけるグローバル電源配電網の最適化

をはかる。

【解決手段】パワーメッシュ配線を構成する、第1のレールは、(a)集積回路のコアロジックの1つ以上のコンポーネントに電源を供給し、(b)集積回路の第1の軸に対して位置合わせされ、(c)メッシュが第1の軸に沿って集積回路の境界から集積回路の中心に一様な電圧傾度を有するように構成される。また、第2のレールは、(a)コアロジックの1つ以上のコンポーネントに電源を供給し、(b)集積回路の第2の軸に対して位置合わせされ、(c)メッシュが第2の軸に沿って集積回路の境界から集積回路の中心に一様な電圧傾度を有するように構成された1つ以上のパラメータを有したものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】プロセスマージンを大きく取れる配線配置構造を提供する。

【解決手段】基板上に形成された複数の第1配線6を含む第1配線層と、第1配線層上に形成され、第1配線6に接続された複数のビアコンタクト10を含むコンタクト層と、コンタクト層上に形成され、ビアコンタクト10に接続された複数の第2配線14を含む第2配線層とを備える半導体装置において、コンタクトピッチは、第1配線6の最小配線ピッチ、又は、第2配線14の最小配線ピッチ、よりも大きくなるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増加を抑制しつつ、ウェハ状態でのスクリーニング時に電源電圧低下(IRドロップ)を抑えることができる半導体装置を提供する。

【解決手段】本発明の一形態に係る半導体装置50は、半導体チップ100と、半導体チップ100上面の中央部のチップ中央領域120に形成された複数の外部接続用パッド102及び複数の検査用パッド104と、複数の外部接続用パッド102上に形成されたバンプ105とを備える。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

61 - 80 / 638

[ Back to top ]