Fターム[5F064EE42]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766) | 配線抵抗 (638)

Fターム[5F064EE42]に分類される特許

101 - 120 / 638

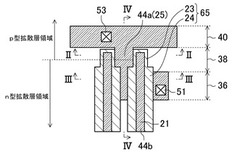

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電気ヒューズに電流を流したときの被切断部の発熱を大きくして、電気ヒューズを切断しやすくする。

【解決手段】半導体装置100は、基板101上に形成された層間絶縁膜108と、層間絶縁膜108中に形成された第1の配線120により構成され、被切断部152を有する電気ヒューズ150と、第1の配線120と同層において、被切断部152の両側方に、それぞれ、被切断部152に沿って延在して形成された第2の配線126および第3の配線128と、を含む。ここで、被切断部152と第2の配線126との間、および被切断部152と第3の配線128との間には、それぞれ、被切断部152に沿って延在して形成されたエアギャップ118が設けられている。

(もっと読む)

半導体装置の設計方法

【課題】クロストークノイズによるディレイ変動量を正確に測定する。

【解決手段】複数のインバータを奇数段直列に接続したリングオシレータROと、リングオシレータROの一部の配線(被害側配線)VICに沿って設けられる第1配線(加害側配線)AGGと、前記第1配線AGGに供給する第1パルスを発生するパルス発生回路PGENと、前記第1配線AGGと前記パルス発生回路PGENの間に接続された第1バッファ(加害ゲート)AGと、前記パルス発生回路PGENと前記第1バッファAGとの間に接続される第2配線を具備し、前記第1配線AGGと前記リングオシレータROの一部の配線VICとの間の距離は、前記第2配線と前記リングオシレータROの一部の配線VICとの間の距離より短くする。

(もっと読む)

半導体集積回路装置およびその製造方法、配線配置装置、配線配置方法、配線配置プログラム、並びに記録媒体

【課題】スタンダードセルを利用して機能回路ブロックをレイアウトする際、供給電源の品質を動作レベルに保ちながら、製造品質を左右する各配線層の占有率のばらつきを少なくする。

【解決手段】スタンダードセル1を、これを構成するセル構成トランジスタを有し、全スタンダードセルに共通接続される電源供給配線及び接地供給配線、および個々のスタンダードセルの機能を実現するための信号配線を含まず、かつ各スタンダードセルの機能を該セル構成トランジスタにより決定する最小限の配置配線、および該セル構成トランジスタの直近に配置され、該スタンダードセルの信号端子を含むよう構成した。

(もっと読む)

半導体装置

【課題】 セルサイズが小さく、かつ配線接続の自由度が向上できるスタンダードセルを用いた半導体装置を提供する。

【解決手段】 半導体装置はメモリ回路と周辺回路を備え、周辺回路を分割した回路ブロックのそれぞれを、同じ高さを有した矩形で、それぞれが基本論理回路として機能するように構成された複数のスタンダードセルを、同じ高さになるように配置したセルブロックとして構成し、スタンダードセルへの入力信号配線が、メモリセルトランジスタと容量下部電極を接続する容量コンタクトパッド配線を用いて配線される。

(もっと読む)

半導体装置

【課題】トランジスタの距離に依存したばらつきに対して、電流源の出力電流誤差を均一にする事ができる、レイアウト構成の半導体装置の提供。

【解決手段】第1の電流源を構成するトランジスタAと、第1の電流源の電流を基準とした第2の電流源を構成する複数のMOSトランジスタBを備えたカレントミラー回路のレイアウトとして、MOSトランジスタAの周囲に、MOSトランジスタBを均等に配置し、入力電流端子及び出力電流端子から、MOSトランジスタA、複数のトランジスタBの同一の端子への配線に関して、それらの特性(寄生抵抗容量)を該配線間で均等化させるレイアウトを有する。

(もっと読む)

半導体集積回路のレイアウト設計方法、半導体集積回路

【課題】ビア抵抗の製造ばらつきによる半導体集積回路の動作不良を低減する。

【解決手段】自動配線ツールを用いて、半導体集積回路の詳細配線が行われる。(S1)

次に、詳細配線が行われた半導体集積回路に対して、セル間の信号パスの静的タイミング解析が行われる。(S2)次に、静的タイミング解析により、タイミング制約に対するタイミング余裕度が取得される。そして、タイミング余裕度が予め設定された基準値未満である信号パスが抽出される。(S3)そして、自動配線ツールを利用して、タイミング余裕度が基準値未満の信号パスのネットに優先的に冗長ビアを挿入する。(S4、S5)そして、タイミング余裕度に基づいて、単一のビアを冗長ビアに置換した後に、タイミング解析を再度行い、信号パスのタイミング違反があるか否かを判定する。(S6)

(もっと読む)

タイミング検証装置、タイミング検証方法、そのコンピュータ・プログラムおよびそのプログラムを記録した記録媒体

【課題】セル内の信号伝播遅延時間の見積り誤差を小さくすることが可能なタイミング検証装置を提供すること。

【解決手段】入出力ピン分割部22は、論理ゲートセル内の入力ピンおよび出力ピンを、寄生抵抗素子によって分割されたサブノードに分割する。セルキャラクタライズ部23は、入出力ピン分割部22によって分割された入力ピンと出力ピンとの組み合わせに対してセルキャラクタライゼーションを行ない、組み合わせのそれぞれに対してセル遅延テーブルを生成する。したがって、セル内の信号伝播遅延時間の見積り誤差を小さくすることが可能となる。

(もっと読む)

集積回路装置及び電子機器

【課題】アナログ処理の特性の向上を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、信号が入力されるパッドPANTと、パッドPANTを介して入力される信号についてのアナログ処理を行うアナログ回路と、アナログ回路の信号入力ノードとパッドPANTとの間に設けられるキャパシターCAを含む。パッドPANTとキャパシターCAの一端とが、最上層金属層ALEで形成されるパッド配線LNPにより接続される。

(もっと読む)

半導体装置

【課題】電源配線やグランド配線に流れる電流の周波数が上がってもインピーダンスが上がるのを抑えられる半導体装置を提供すること。

【解決手段】トランジスタ20、21の近傍に配線された電源配線11a及びグランド配線11cを備え、電源配線11a及びグランド配線11cは、それぞれ、分割した構造となっており、所定間隔をおいて一方向に配線された複数本の分割配線11a、11cよりなる。

(もっと読む)

半導体集積回路の設計方法および半導体集積回路設計支援装置

【課題】IRドロップによる動作不良を改善するための不要な電源配線やチップ面積の増大を抑え、かつ、タイミング制約が厳しい回路ブロックが適切に配置された半導体集積回路を提供する。

【解決手段】半導体集積回路を以下の方法で設計する。まず、(a)設計対象の半導体集積回路のレイアウト領域に回路セルを配置する。次に、(b)回路セルが配置されたレイアウト領域で消費される消費電力を算出する。このとき、(c)レイアウト領域のIRドロップ検証を実行して、IRドロップが発生しているIRドロップ発生領域を特定する。そして、(d)レイアウト領域のSTA解析を実行して、クリティカルパスを特定する。そして、(e)クリティカルパスに含まれない回路セルを、移動候補回路セルとして特定する。そして、(f)IRドロップ発生領域に配置されている移動候補回路セルを、IRドロップ発生領域の外に移動する。

(もっと読む)

回路のジッタを計算する方法、論理装置及びシステム並びに回路のクロックツリーを合成する方法、論理装置及びシステム

【課題】チップレベルの設計に関する問題に対処し、クロストークカップリングが存在する場合でも正確な経路遅延を計算すること。

【解決手段】一実施例でのクロックツリーにてジッタを計算する方法は、クロックツリーを複数のステージに分割し、クロックツリーに関連する回路の少なくとも一部分のモデルに従って、1以上のステージのジッタを算出する。モデルは回路のジッタのソース各々の表現を含む。本方法は、クロックツリー中の経路又は経路対に関するジッタを計算するため、クロックツリー中の経路又は経路対の各ステージのジッタを互いに統計的に合成するステップを含む。一実施例では、ジッタを効率的に計算し且つクロックスキューゼロを達成するため、モデルは回路の対称的なクロックツリーを合成し、そのツリーでは区六浮くツリーのルートからクロックツリーのシンクに至る全てのパス中の関連するステージは、近似的に電気的に互いに等価な性質を示す。

(もっと読む)

半導体装置の設計方法及び半導体装置の設計装置

【課題】レイアウト全体を設計することなく、各部分で設計したレイアウトデータから抽出した寄生容量及び寄生抵抗を用いた回路データを正しく作成する半導体装置の設計方法を提供する。

【解決手段】半導体装置を複数の領域に分割し、各領域のレイアウトから全体のレイアウト設計する設計方法において、領域毎のレイアウトに対して、各領域の境界部の配線領域に配線領域毎に形状が異なる微小抵抗領域を付加するステップS13と、微小抵抗領域が付加されたレイアウトのデータから、抽出された寄生容量及び寄生抵抗と、微小抵抗領域に対応する微小抵抗とを含んだ回路データを作成するステップS14と、回路データに含まれる微小抵抗を識別子として、複数の領域において同一の識別子の微小抵抗同士を接続することで、各領域の回路データを組み合わせるステップS16とを含んでいる。

(もっと読む)

スパイラルコイルの配線構造および集積回路装置

【課題】 第1インダクターおよび第2インダクターを有する3ポートのスパイラルコイルにおける特性の対称性を確保し、かつ、3つのポートを、スパイラルコイルの中心を通る直線を基準として同じ側に配置すること。

【解決手段】 第1ポートと第3ポートとの間に設けられる第1インダクターと、第2ポートと前記第3ポートとの間に設けられる第2インダクターとを含むスパイラルコイルの配線構造であって、スパイラルコイルの中心を通る直線を基準として、前記第1ポートおよび第2ポートは同じ側に配置され、第1ポートから引き出される第1配線と、第2ポートから引き出される第2配線とが、スパイラルコイルの中心を通る直線を基準として、第1ポートおよび第2ポートの側において交差することによって第1交差部が設けられる。

(もっと読む)

回路シミュレーション方法

【課題】半導体抵抗素子の端子部寄生抵抗を正確に見積もることができる回路シミュレーション方法。

【解決手段】半導体抵抗素子102と、半導体抵抗素子102の端子部上に、半導体抵抗素子102の幅方向と長手方向とにそれぞれ等間隔に配置された複数のコンタクトCTと、複数のコンタクトCT上に形成された配線101と、を備えた半導体回路のシミュレーション方法。1つのコンタクトCTの抵抗値と、長手方向において隣接するコンタクトCT間の半導体抵抗素子102による寄生抵抗値との比を、定数kとして定義し、半導体抵抗素子102の端子部と、複数のコンタクトCTと、を含む寄生抵抗ネットを、定数kを用いることによりモデル化する。

(もっと読む)

配線設計方法およびプログラム

【課題】配線性の低下を最小限に抑えながら、信号の特性インピーダンスの変化を抑制する。

【解決手段】ビアVに近接する特定信号配線Whがある場合、該特定信号配線Whを含む配線の配線性を評価すべき領域ERの一端LPを、特定信号配線Whの輪郭線E1〜E4のうちビアVに対向する側の輪郭線E4に一致させた上で、評価関数の値を求める。

(もっと読む)

寄生素子の抽出システムと抽出方法

【課題】ある程度の精度を保ちながらレイアウトデータから寄生素子の寄生値を抽出する時間を短縮することを可能とする。

【解決手段】寄生素子の抽出システムは、半導体装置のレイアウトを構成する各配線層を所定の基準に基づいて上層配線層と下層配線層とに分類する分類部と、上層と下層の配線層を接続するビアを示すマーカーを生成するマーカー生成部と、第1の基準に基づいて上層配線層の寄生素子を抽出することにより上層寄生素子リストを生成する上層寄生素子リスト生成部と、第1の基準と異なる第2の基準に基づいて下層配線層の寄生素子を抽出することにより下層寄生素子リストを生成する下層寄生素子リスト生成部と、マーカーを用いて上層寄生素子リストと下層寄生素子リストとを結合することによりレイアウトの寄生素子リストを生成する寄生素子リスト生成部とを備える。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置のレイアウト方法

【課題】半導体装置の面積を大きくすることなくデカップリング容量を確保する。

【解決手段】機能ブロック12がPMOS領域14とNMOS領域16とに分割され、PMOS領域14には複数のP型のMOS−FET18、NMOS領域16には複数のN型のMOS−FET20が配置され、P型のMOS−FET18とN型のMOS−FET20とがそれぞれ対向して配置されており、P型のMOS−FET18及びN型のMOS−FET20が配置されていないPMOS領域14の空領域にデカップリング容量としてP型のMOS容量22を、NMOS領域16の空領域にN型のMOS容量24を、空領域の形状に応じた形状で形成して配置する。

(もっと読む)

半導体集積回路

【課題】独立してクロック信号の供給と遮断が行われる領域を有する半導体集積回路において、クロックスキューを低減し、かつ、消費電力を低減すること

【解決手段】本発明にかかる半導体集積回路1は、クロック信号が供給される第1の配線と、第1の配線に供給されるクロック信号とは独立して供給と遮断とが切り替えられてクロック信号が供給される第2の配線と、第1の配線からクロック信号が供給される第1のメッシュ形状配線を有する第1の領域と、第2の配線からクロック信号が供給される第2のメッシュ形状配線を有する第2の領域と、第1のメッシュ形状配線と第2のメッシュ形状配線の間の信号の導通と遮断を切り替え可能な切り替え回路とを備える。

(もっと読む)

半導体記憶装置

【課題】2列パッド配置の半導体記憶装置におけるレイアウトを最適化することにより、電源電圧を安定化する。

【解決手段】メモリセルアレイ領域201,202と、これらの間に配置された周辺回路領域301と、メモリセルアレイ領域201と周辺回路領域との間に配置されたパッド列101と、メモリセルアレイ領域202と周辺回路領域との間に配置されたパッド列102と、を備える。メモリセルアレイ領域201とパッド列101との間及びメモリセルアレイ領域202とパッド列102との間に、周辺回路が実質的に配置されていない。これにより、上層の低抵抗配線を用いてメモリセルアレイ領域と所定のパッドとを短距離で接続できるため、メモリセルアレイ領域に電源電位を安定的に供給することが可能となる。

(もっと読む)

101 - 120 / 638

[ Back to top ]