Fターム[5F064EE42]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線(又は配線間)の物理的性質 (2,766) | 配線抵抗 (638)

Fターム[5F064EE42]に分類される特許

121 - 140 / 638

半導体集積回路

【課題】入力回路または出力回路を介して電源配線にサージ電圧が印加された場合においても、素子面積の増大を抑制しつつ、内部回路を静電破壊から安定的に保護する。

【解決手段】入出力セル3c〜3fの間の隙間に電源保護素子6a〜6dをそれぞれ配置し、電源保護素子6a〜6dとして、電源配線7、8間に接続されたダイオードストリングS2〜S5をそれぞれ用いる。

(もっと読む)

半導体集積回路装置

【課題】電源遮断時にそれ以前の情報を保持する低消費電力モードにおいてその復帰を高速にする。その一つに従来のデータ保持型フリップフロップを用いることが考えられるが、そのためにセルを大きくする等の面積オーバーヘッドが生じるのは望ましくない。

【解決手段】電源遮断時のデータ保持のための電源線は一般の電源幹線よりも細い配線にて形成する。望ましくは、データ保持回路の電源を信号線扱いとして、自動配置配線時に配線することである。そのために、セルにはあらかじめ上記データ保持回路用電源のための端子を通常の信号線と同様に設けて設計しておく。[効果]セルに余分な電源線のレイアウトが不要となり省面積化が図られるとともに、既存の自動配置配線ツールにより設計が可能となる。

(もっと読む)

半導体装置

【課題】ESD放電経路におけるメタル配線の電流密度の許容値を高くとることが可能であり、また、配線抵抗を小さくすることが可能である半導体装置を提供する。

【解決手段】信号パッド(101)と、電源線(103)と、接地線(104)と、一端が信号パッド(101)と接続されたインダクタ(111)と、インダクタ(111)の他端と電源線(103)または接地線(104)との間に設けられた終端抵抗(112)と、インダクタ(111)の中間の第1位置(Aa)に接続された第1ESD保護素子(ESD_G)と、インダクタ(111)の中間の第1位置(Aa)とは異なる第2位置(Ab)に接続された第2ESD保護素子(ESD_V)とを備える。

(もっと読む)

半導体装置の設計方法および半導体装置の製造方法

【課題】本発明によれば、素子や配線の配置面積を縮小しつつ、ビアの高抵抗不良およびオープン不良が発生しないようにする。

【解決手段】半導体装置100は、下部電極106と上部電極110と、その間に形成された容量膜108とを含む容量112と、下部電極106に電気的に接続する一以上の第1のビア(128)を含む第1のビア群と、上部電極110に電気的に接続するとともに第1のビア群と同時に形成される一以上の第2のビア(130)を含む第2のビア群と、を含む。半導体装置100は、容量112の容量値を第1のビア群および第2のビア群に含まれる第1のビア(128)および第2のビア(130)の総数で除した値が所定値以下となるように第1のビアおよび第2のビアの数を設定する工程を含む方法で設計される。

(もっと読む)

半導体集積回路、及び半導体集積回路のレイアウト方法

【課題】ロジックセルを配置するためのスペースを十分に確保することのできる、半導体集積回路、半導体集積回路のレイアウト方法、半導体集積回路のレイアウトプログラム、及び半導体集積回路のレイアウト装置を提供する。

【解決手段】自動配置配線ツールにより、ロジックセル、及び前記ロジックセルに接続される信号配線をレイアウトし、ロジックセルレイアウトデータを生成するステップと、前記自動配置配線ツールにより、可変容量セル及び前記可変容量セルの容量を制御する制御配線をレイアウトし、可変容量セルレイアウトデータを生成するステップと、前記ロジックセルレイアウトデータ及び前記可変容量セルレイアウトデータに基づいて、半導体集積回路のレイアウトデータを生成するステップとを具備する。前記可変容量セルレイアウトデータを生成するステップは、前記制御配線を、同一配線層内で単位長あたりの抵抗が前記信号配線のそれと同じになるように、レイアウトするステップを含んでいる。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、設計支援装置、及び半導体集積回路

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、回路情報21に基づいてレイアウト対象回路41、42の消費電流量211を算出するステップと、電源配線2から電源供給可能な領域における単位面積当りの供給可能電流量212を算出するステップと、算出された消費電流量211に基づき、レイアウト対象回路41、42の単位面積当りの消費電流量が、供給可能電流量212以上となるように、対象回路のセルサイズ213を設定するステップとを具備する。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】複数の配線層構造情報を共通化し、各配線層構造情報によって配線の特徴情報が相違することを意識することなく設計でき、設計期間の短縮化および利用者の負担の軽減化を図ること。

【解決手段】設計支援装置は、階層ごとに配線の特徴情報を有する第1の配線層構造情報から第Nの配線層構造情報までの複数の配線層構造情報100から、特徴情報が相違する階層を特定し、特製された階層の特徴情報を包含する特徴情報を生成する。つぎに、配線層構造情報を複製し、複製された配線層構造情報内の特徴情報が相違する階層の特徴情報を、生成した特徴情報に変換する。そして、変換後の配線層構造情報101と複数の配線層構造情報100とを関連付けて記憶装置に格納する。

(もっと読む)

半導体装置の製造方法、製造プログラム、及び半導体装置

【課題】回路規模の増大を抑制しつつ、素子破壊によってノード間の電気的接続を制御する電流制御素子を有する半導体装置の信頼性を高める。

【解決手段】本発明による半導体装置の製造方法は、半導体ウエハ1上に形成された素子特性抽出用パタン30の素子特性を測定するステップと、測定された素子特性を、素子特性抽出用パタン30に対応付けられた電流制御素子20の素子特性として抽出するステップと、抽出された素子特性に基づいて、半導体ウエハ1上におけるノード間に形成された電流制御素子20に供給するエネルギーを設定するステップと、設定されたエネルギーを電流制御素子に供給し、電流制御素子の素子破壊によってノード間の電気的接続を不可逆的に制御するステップとを具備する。

(もっと読む)

半導体装置

【課題】チャネル形成領域が素子分離領域から受けるストレスを、チャネル幅方向において均一化させる。

【解決手段】素子分離領域2と、素子分離領域2によって囲まれる、素子形成領域3とを具備する。素子形成領域3の外周形状は、第1方向に沿って延びる第1辺を有する。素子形成領域3は、第1トランジスタ領域6−1と、2方向において第1辺と第1トランジスタ領域6−1との間にあたる位置に配置された、第2トランジスタ領域6−2と、第1方向における第2トランジスタ領域6−2の側方に配置された、ダミー領域7とを備える。第1トランジスタ領域6−1は、第1チャネル形成領域4−1を有する。第2トランジスタ領域6−2は、第2チャネル形成領域4−2を有する。第1チャネル形成領域4−1は、第2チャネル形成領域4−2と非対向である非対向領域14を有する。ダミー領域7は、第2方向において非対向領域14と対向する。

(もっと読む)

電源ノイズ解析方法及び電源ノイズ解析プログラム

【課題】SSOノイズの解析精度を落とさずにパッケージモデルの回路規模を削減できるSSOノイズ解析方法及び装置を提供する。

【解決手段】複数の信号駆動回路と、複数の信号駆動回路に第1の電源電圧を供給する第1の配線と、複数の信号駆動回路に第2の電源電圧を供給する第2の配線と、複数の信号駆動回路により駆動される信号を伝搬する複数の第3の配線とを含んだモデルを用いる電源ノイズ解析方法は、レイアウト情報から第1乃至第3の配線の自己インダクタンス及び相互インダクタンスを抽出し、信号の駆動時に流れる電流経路を特定し、特定された電流経路の情報に基づいて自己インダクタンスと相互インダクタンスとを合成することにより第1乃至第3の配線の各々の実効インダクタンスを求め、実効インダクタンスを含めたモデルを用いて回路シミュレータを実行する各段階を含む。

(もっと読む)

電子部品装置および変化部品の製造方法

【課題】製造ばらつき等に対しても、高品質で電気的接続状態を変化させる。

【解決手段】電子部品装置200は、第1のヒューズ素子102aを含む第1のヒューズユニット100a、および第2のヒューズ素子102bを含む第2のヒューズユニット100bを含む電気ヒューズ101と、第1のヒューズ素子102aおよび第2のヒューズ素子102bの少なくともいずれか一方が電気的に切断されている場合に、電気ヒューズ101が電気的に切断されていると判定する判定回路150とを含む。第1のヒューズユニット100aおよび第2のヒューズユニット100bは、それぞれ独立に電流が印加され、所定の電流または電圧を印加した場合に電気的接続状態の変化が生じない割合に影響を与える制御パラメータの適正範囲が異なるように構成されるかまたは、値の異なる電流により切断される。

(もっと読む)

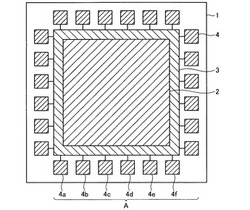

集積回路構造

【課題】スルーシリコンビアから形成されるグリッドマトリクスを用いて電力供給される集積回路を提供する。

【解決手段】集積回路構造は、基板を有するチップと、配電回路網とを含む。配電回路網は、基板を貫通し、グリッドを形成する複数の電力スルーシリコンビア(TSV)と、底部金属化層(M1)中に位置し、複数の電力TSVを、基板上の集積回路装置に結合する複数の金属線とを含む。

(もっと読む)

デカップリング容量決定方法、デカップリング容量決定装置およびプログラム

【課題】簡易に行える、配線のインダクタンスを考慮した高精度のデカップリング容量決定処理方法および装置の実現。

【解決手段】半導体集積回路装置のデカップリング容量決定方法であって、動作周波数f、消費電力P、電源電圧V、許容電源電圧変動量ΔV、パッケージインダクタンス量L、および固有容量Cpを含む設計データを導入しS201、基準ダイ容量Cv1を演算しS203、CpがCv1より小さい時にはCv1とCpの差をデカップリング容量CdとしS205、CpがCv1より大きい時にはCdをゼロとしS206、CpとCdの和である実ダイ容量CvとLから共振周波数Trを演算しS208、比Tr/kTが1より大きいか判定しS209、比が1以下の時にはCdを維持しS212、比が1より大きい時には、さらにCvがCv1Tr/kTより大きい時にはCdを維持し、CvがCv1Tr/kTより小さい時には、CvがCv1Tr/kT以上になるようにCdを決定する。

(もっと読む)

半導体装置

【課題】デカップリング容量セルを用いて電源配線の電圧変動を抑制し、かつ、電源配線の電源共振を防ぐ半導体装置を提供する。

【解決手段】半導体チップ100に複数配置されたデカップリング容量セルを、トランジスタ素子及び容量素子の直列回路で構成する。制御回路CTRCにおいては、半導体チップ100を動作させる基準クロック又はそこから生成される高周波数のクロックが入力され、そのクロックに同期した制御信号CTRLを生成し、デカップリング容量セルの電源配線VDDへの容量素子の接続/非接続を行う。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】対象回路内のセルごとに当該セルの遅延時間を適正化することが可能な遅延時間の補正係数および出力スルーの補正係数を当該対象回路の遅延時間の算出前に用意して遅延時間の見積もり精度の向上化を図ること。

【解決手段】設計支援装置は、駆動能力の値と、集中定数容量の値と、集中定数容量の一部の値である入力容量の値と、を回路モデルに設定し、当該回路モデルをシミュレータに与え、当該シミュレータの模擬により得られた当該回路モデルの第2の遅延時間および第2の出力スルーをシミュレータから取得し、駆動能力の値および集中定数容量の値に基づく回路モデルの第1の遅延時間と第2の遅延時間との相対的な評価値を算出して遅延時間の補正係数とし、駆動能力の値および集中定数容量の値に基づく回路モデルの第1の出力スルーと第2の出力スルーとの相対的な評価値を算出して出力スルーの補正係数とする。

(もっと読む)

半導体集積回路装置及びその設計方法

【課題】フリップチップ構造を有する半導体集積回路装置において、チップサイズを縮小して製造コストを削減できるようにする。

【解決手段】半導体集積回路装置は、複数の入出力セル105を有する半導体チップ100と、半導体チップの表面上に形成された複数のパッド101、102と、半導体チップ100の表面上に形成され、且つ複数の入出力セル105の少なくとも一部と複数のパッド101、102の少なくとも一部とを電気的に接続するパッド間配線103、104とを優している。複数のパッド101、102は、半導体チップ100の中央部おいて四角格子状に配置され、且つ、半導体チップ100の4つの隅部のうちの少なくとも一隅部において千鳥状に配置されている。

(もっと読む)

半導体集積回路のレイアウト方法及び論理修正方法

【課題】論理ゲートや論理ゲートの入出力端子の配置にかかわらず、信号配線の引き出し端子を密集させることなく配置すること。

【解決手段】本発明は、複数の論理ゲート309に接続された配線層301〜303を、論理ゲート出力端子306と論理ゲート入力端子307又は論理ゲート出力端子306及び論理ゲート入力端子307と配線分岐点308とを結ぶ線分に分割する。続いて、この線分において、この線分よりも上層の配線層に配置された配線が最も少ない点を、仮想分割点として抽出する。そして、この線分を仮想分割点にて分割することにより、仮想分割配線401を生成する。続いて、仮想分割配線401を構成する配線層と、配線層303とを接続する追加配線501を配置する。追加配線501は、仮想分割点の直上を避けて配置される。

(もっと読む)

レイアウト設計方法及びレイアウト設計装置

【課題】レイアウト工程を再度行わずに、タイミング違反が発生した配線の遅延時間を微調整することができ、レイアウトプロセスのTATを短くすることができるレイアウト設計方法及びレイアウト設計装置を提供する。

【解決手段】半導体集積回路のレイアウト設計方法は、レイアウトデータにおける第1の論理セルと第2の論理セルの間の対象配線が配置される領域に、ダミーセル(電源間容量セル、バッファセル)を配置するダミーセル配置ステップ(S2)を含む。また、レイアウト後にタイミング検証を実行し(S4)、タイミング違反が発生した対象配線近傍の電源間容量セルを容量セルへ置換し(S8)、対象配線へ接続する(S9)。又は、タイミング違反配線を第1の配線、第2の配線に切断し、バッファセルの入力端子を第1の配線へ、出力端子を第2の配線へと接続する。

(もっと読む)

試験条件調整装置および試験条件調整方法

【課題】チップ規模の増大を防止すること。

【解決手段】比較部2は、設計対象の半導体回路の第1の動作条件での電圧降下と、第2の動作条件での電圧降下とを例えば、シミュレーションを行って比較する。ここで、第1の動作条件は、例えば、半導体回路完成後の実動作時の動作条件であり、第2の動作条件は、例えば、半導体回路完成後の出荷試験を行うとき(試験時)の動作条件である。調整部3は、第2の動作条件での電圧降下が、第1の動作条件での電圧降下よりも大きい場合、半導体回路の遅延特性に基づいて、第2の動作条件を調整する。

(もっと読む)

半導体装置

【課題】局所的な電圧降下を効果的に抑制できる電源配線構造を有した半導体装置を提供する。

【解決手段】第1配線層は複数の第1配線ブロック10を含み、当該各第1配線ブロック10には、第1電位を持ち且つ少なくとも二方向以上に延びる第1配線11と、第1電位と異なる第2電位を持ち且つ少なくとも二方向以上に延びる第2配線12とが配置されている。第2配線層は、隣り合う一対の第1配線ブロック10における第1配線11同士を電気的に接続する第3配線21と、当該一対の第1配線ブロック10における第2配線12同士を電気的に接続する第4配線22とを含む。

(もっと読む)

121 - 140 / 638

[ Back to top ]