Fターム[5F064FF45]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択実行方法 (1,017) | 電圧、電流の供給、変更 (416)

Fターム[5F064FF45]の下位に属するFターム

端子への入力電圧の変更 (95)

Fターム[5F064FF45]に分類される特許

1 - 20 / 321

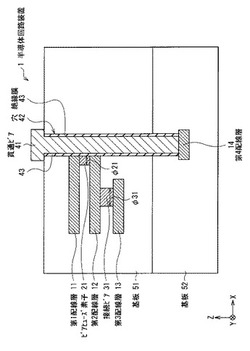

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミングや冗長に用いられるヒューズを有する半導体装置に関し、安定且つ確実に溶断しうるヒューズを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に、第1の絶縁膜を形成し、第1の絶縁膜上に、ヒューズを形成し、ヒューズが形成された半導体基板上に、第1の絶縁膜に接して第2の絶縁膜を形成し、ヒューズ上の第2の絶縁膜に、開口部を形成し、第2の絶縁膜上及び開口部内に第3の絶縁膜を形成する。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法

【課題】カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法を提供する。

【解決手段】カップリングチャネルを使用したアンチヒューズメモリは、第1導電型の基板と、第2導電型のドープ領域と、カップリングゲートと、ゲート誘電層と、アンチヒューズゲートと、アンチヒューズ層と、を含む。基板中に隔離構造を有する。ドープ領域が基板中に設置され、且つドープ領域及び隔離構造の間にチャネル領域を定義する。カップリングゲートがドープ領域及び隔離構造の間の基板上に設置され、且つカップリングゲートとドープ領域と隣り合う。ゲート誘電層がカップリングゲート及び基板の間に設置される。アンチヒューズゲートがカップリングゲート及び隔離構造の間の基板上に設置され、アンチヒューズゲート及びカップリングゲートの間に間隔を有する。アンチヒューズ層がアンチヒューズゲート及び基板の間に設置される。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

トリミング回路及び半導体装置

【課題】ヒューズを切断するための電流を入力する専用の端子を必要としないトリミング回路及び半導体装置を提供する。

【解決手段】内部回路の外部端子であるパッドに接続された入力端子と、電源端子と出力端子との間に設けられたヒューズと、入力端子と出力端子との間に設けられたダイオードと、を備え、パッドにダイオードが順方向バイアスになるように電圧を印加して、トリミング回路のトリミングを行うように構成した。

(もっと読む)

電気ヒューズ、半導体装置、及び、電気ヒューズの情報書き込み方法

【課題】 例えば半導体集積回路等のチップに搭載する電気ヒューズの容量を省スペースで効率よく増加させることのできる電気ヒューズ、及び、それを備える半導体装置を提供する。

【解決手段】 電気ヒューズは、第1導電層4と、第1導電層4上に形成された第2導電層5とを有しフィラメント1を備える。そして、フィラメント1は、第1導電層4の状態及び第2導電層5の状態の組み合わせを変えることにより、少なくとも3つの識別可能な抵抗状態が生成されるように構成される。

(もっと読む)

ランダム・アクセス電気的プログラム可能なEヒューズROM

【課題】ランダム・アクセス電気的プログラム可能なeヒューズROMを提供する。

【解決手段】1回プログラム可能な読み出し専用メモリ(OTPROM)が、アグレッシブにスケール縮小された、シリサイド移動可能なeヒューズの2次元配列において実施される。ワード・ライン選択は、VDDにおいて動作するデコード論理によって実施され、一方ビット・ライン・ドライブは、VDDとプログラミングのためのより高い電圧VPとの間でスイッチ切替えされる。OTPROMは、それゆえコストを加算することなしに他の技術と適合可能で、統合することができ、そして、ヒューズ・プログラミングの間、電圧降下を最小にする高電流経路の最適化をサポートする。プログラム可能参照を有する差動センス増幅器は、センス・マージンを改善するために使用され、個々のヒューズに設けられるセンス増幅器の代りに、ビット・ライン全体をサポートすることができる。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】電圧検出部12は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)へ供給される書き込み電圧を検出し、書き込み電圧が所定の閾値電圧以上となると、書き込み制御部11に、書き込み信号に係わらず電気ヒューズ素子2への書き込みを停止させることで、書き込み電圧に異常が発生し、過電圧になることによる誤書き込みを抑制できる。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

一方向性アンチヒューズ素子及びこれを用いた発光ダイオードユニット

【課題】1列に直列接続された各発光ダイオード(LED)素子の各々にそれぞれ1つのアンチヒューズ素子が並列接続されているLEDユニットにおいて、電源を誤って逆方向に接続した場合にも、LEDユニットを保護する一方向性アンチヒューズ素子を提供する。

【解決手段】1はカソード電極端子Kに接続されたカソード電極層、2はp型不純物層21及びn型不純物層22よりなる半導体層、3は絶縁層、4はボンディングワイヤ5によってアノード電極端子Aに接続されたアノード電極層、6は封止樹脂層である。カソード電極端子Kとアノード電極端子Aとの間に順方向電圧が印加された場合のみ、一方向性アンチヒューズ素子はアンチヒューズとして作用する。カソード電極端子Kとアノード電極端子Aとの間に逆方向電圧が印加された場合には、一方向性アンチヒューズ素子はアンチヒューズとして作用しない。

(もっと読む)

半導体装置およびその製造方法

【課題】銅を主成分とする配線層を有し、かつヒューズの切断によって特性の悪化を招くことのない半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、銅を主成分とするメタル配線34と、メタル配線34よりも上層に形成された最上層配線5と、メタル配線34と最上層配線5との間を接続するためのプラグ9が形成されるプラグ形成層10に少なくとも一部が形成され、銅以外の金属材料を主成分とする導電性材料で形成されたヒューズ膜4とを含む。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体装置およびその製造方法

【課題】電気ヒューズまたはアンチヒューズの保持特性を高める。

【解決手段】半導体装置100は、半導体基板と、該半導体基板の上部に設けられた電気ヒューズ200とを備える。電気ヒューズ200は、直列に接続された第1のヒューズリンク202および第2のヒューズリンク204と、第1のヒューズリンク202の一端および他端にそれぞれ設けられた第1の電流流入/流出端子(第1の端子206)および第2の電流流入/流出端子(第2の端子208)と、第2のヒューズリンク204の一端および他端にそれぞれ設けられた第3の電流流入/流出端子(第2の端子208)および第4の電流流入/流出端子(第3の端子210)とを含む。

(もっと読む)

貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法

【課題】貫通電極を有する積層構造の半導体装置、半導体メモリ装置、半導体メモリ・システム及びその動作方法を提供する。

【解決手段】複数の半導体レイヤ間で伝送される情報の衝突を防止する構造を有する半導体装置であり、該半導体装置は、第1温度情報を出力する第1温度センサ回路を含む少なくとも1つの第1半導体チップと、貫通電極に電気的に連結されずに、第1温度センサ回路に電気的に連結される第1バンプと、第1半導体チップの貫通電極に電気的に連結される第2バンプと、を具備する半導体装置であることを特徴とする。

(もっと読む)

1 - 20 / 321

[ Back to top ]