Fターム[5F064GG03]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798) | エッチング (379)

Fターム[5F064GG03]に分類される特許

101 - 120 / 379

アップサンプリング装置及びダウンサンプリング装置

【課題】レイアウトデータの階層構造を有効に利用して、精度を高く維持しつつ処理の能率を高めることのできるアップサンプリング装置、ダウンサンプリング装置を提供する。

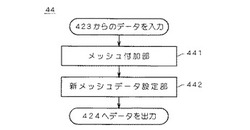

【解決手段】アップサンプリング部44は、メッシュ付加部441および新メッシュデータ設定部442を備えている。メッシュ付加部441は、空間フィルタ部423から入力される画像データに新たなメッシュを付加する。新メッシュデータ設定部442は、付加されたメッシュ上の画像データにゼロの値を設定し、メッシュが付加される前の画像データとともに、逆フーリエ変換部424へ出力する。

(もっと読む)

非等長コンタクトを用いた電気的にプログラム可能なヒューズ及びその製造方法

【課題】改良された熱特性を有する非等長コンタクトを含む電気的にプログラム可能なヒューズ、及びその製造方法を提供する。

【解決手段】その上に形成されたシリサイド層を有するポリシリコン層から形成されたアノード・コンタクト領域110及びカソード・コンタクト領域118と、カソード・コンタクト領域とアノード・コンタクト領域とを導電接続する、プログラミング電流を印加することによってプログラム可能なヒューズリンク116と、カソード・コンタクト領域のシリサイド層上又はカソード・コンタクト領域とアノード・コンタクト領域の両方のシリサイド層上にそれぞれ所定の構成で形成された複数の非等長コンタクト120とを含む、電気的にプログラム可能なヒューズである。

(もっと読む)

低電力多重状態電子ヒューズ(eヒューズ)をプログラミング及び再プログラミングするための回路構造体及び方法

【課題】 低電力多重状態の電子ヒューズをプログラミング及び再プログラミングするための回路構造体及び方法を提供する。

【解決手段】 eヒューズのプログラミング/再プログラミング回路の実施形態を開示する。一実施形態において、eヒューズ(150)は、長い低原子拡散抵抗導体層(120)の同じ端部に両側(121、122)上に配置された2つの短い高原子拡散抵抗導体層(110、130)を有する。電圧源(170)を用いて端子(第1の端子=170/161/110、第2の端子=170/162/130、第3の端子=170/163/導体層120の近位端123、及び第4の端子=170/164/導電層120の遠位端124)に印加する電圧の極性及び随意的に大きさを変化させて、長い導体層内の電子の2方向の流れを制御し、これにより長い導体層と短い導体層との界面(125、126)における開路及び/又は短絡の形成を制御する。このような開路及び/又は短絡の形成を用いて異なるプログラミング状態(11、01、10、00)を実現することができる。他の回路構造体の実施形態は、さらに多くのプログラミング状態を可能にするように、付加的な導体層及び付加的な端子を有するeヒューズ(650)を組み込む。さらに、関連したeヒューズのプログラミング及び再プログラミング方法の実施形態を開示する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来よりも少数のLEを用いてより小面積のDFFを構成できる、ビアパターンによって論理を変更可能な半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、

複数のトランジスタと、これらに接続された第1メタル層とが形成された基板において、第1メタル層の上に、第1ビアパターンを含む第1ビア層を形成する工程と、

第1ビア層の上に第2メタル層、第2ビア層および第3メタル層を形成する工程と、

第3メタル層の上に、第3ビアパターンを含む第3ビア層を形成する工程とを含み、

複数の前記トランジスタによって基本論理素子が構成され、

基本論理素子が、2つのN型トランジスタ及び2つのP型トランジスタ(CS2)と、1つのAOIゲート(AOI)と、2つのインバータ(INV)とを備え、

第1ビアパターンによって基本論理素子の論理を決定し、

第3ビアパターンによって基本論理素子間の配線を決定する。

(もっと読む)

整調可能な特性インピーダンスを有する垂直型共平面導波路、その設計構造、およびその作製方法

【課題】整調可能な特性インピーダンスを有するオンチップ垂直型共平面導波路、その設計構造、およびその作製方法を提供する。

【解決手段】オンチップ伝送線路(60)は、信号ライン(65)、信号ラインの上側にあって該信号ラインから離間された上方接地ライン(70)、および信号ラインの下側にあって該信号ラインから離間された下方接地ライン(75)を包含する。信号ライン、上方接地ライン、および下方接地ラインは、誘電材料(80)中にほぼ垂直並びに配列されている。

(もっと読む)

半導体装置、下層配線設計装置、下層配線設計方法およびコンピュータプログラム

【課題】MIMキャパシタの構造破壊に起因するリーク電流の上昇を低減する構成を備えた半導体装置を提供することを課題とする。

【解決手段】複数の下層配線11を備える下層配線層10と、下層配線層10の上方に設けられる、下部電極21と容量誘電膜22と平面形状が下部電極21より小さい上部電極23とを下からこの順に積層したMIMキャパシタ20と、MIMキャパシタ20の上方に設けられ、ビア40、41を介して下部電極21および上部電極23のそれぞれに接続する複数の上層配線31を備える上層配線層30と、を備えた半導体装置であって、上部電極23の平面形状は矩形に構成され、上部電極23の平面のいずれか一以上の辺であるエッジ部の直下には下層配線11が配置されていない半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上に抵抗素子を備える半導体装置において、シリコン抵抗素子の抵抗値の低下を防ぐ。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとシリコン抵抗素子を備える。抵抗素子は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層37と、からなる。絶縁膜30は、シリコン酸化膜、シリコン窒化膜、HfSiON、HfO2、ZrO2、HfAlO、Al2O3から選ばれる少なくとも一つを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置の設計方法

【課題】配線層の溶出、および酸化を抑制する半導体装置、およびその設計方法を提供する。

【解決手段】接続コンタクトに接続される金属配線の配置を決定するステップと、接続コンタクトを設けるためのスルーホールの配置を決定するステップとを具備する半導体装置に設計方法を適用する。ここで、金属配線の配置を決定するステップは、(a)スルーホールによって露出する金属配線の領域を特定するステップと、(b)金属配線に付帯する容量を特定するステップと、(c)容量が蓄える電荷が、領域を介して金属配線から極性溶媒に移動したときの領域の損傷を抑制するように、金属配線の配置を決定するステップとを含むものとする。

(もっと読む)

集積回路のための電気的に切断される金属ヒューズの構造体及びその形成方法

【課題】 プログラミングを達成するために、過剰な電圧及び電流を用いることなく、電気的に切断される金属ヒューズ構造体を提供する。

【解決手段】 集積回路デバイスのためのヒューズ構造体が、絶縁層内に定められた細長い金属相互接続層(106)と、金属相互接続層の上面の一部分上にのみ形成された金属キャップ層(108)と、金属キャップ層(108)及び金属キャップ層(108)が上に形成されていない金属相互接続層の残りの部分の両方の上に形成された誘電体キャップ層(112)とを含み、金属キャップ層(108)が上に形成されていない金属相互接続層の残りの部分は、エレクトロマイグレーション損傷メカニズムを受けやすく、細長い金属相互接続層(106)を通して電流を流すことによって、ヒューズ構造体のプログラミングが容易になる。

(もっと読む)

半導体装置

【課題】少ない電流で精度よく切断することができる電気ヒューズを備えた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、半導体基板と、半導体基板上に形成された絶縁膜5と、絶縁膜5中に形成された電気ヒューズ3と、電気ヒューズ3の両端に形成された配線2a、2bと、絶縁膜5中に電気ヒューズ3の側面の一部である露出面30に面して形成された空隙4と、を有する。

(もっと読む)

電気接点の製造方法

【課題】 端子の先端に、水平方向に突出する突起を所望の形状で形成できる電気接点の製造方法を提供すること。

【解決手段】 母材を、電気接点20Aの形状にパターニングされたマスク30で覆ってエッチング液で母材の不要な部分を除去することにより、電気接点20Aを形成する。電気接点20Aの先端24の第1の突起24a及び第2の突起24bは、マスクの先端34に設けた突起形成部31a,31bにより形成されるが、突起形成部31a,31bの形状を突起の形状及び形成領域のL/S(ラインアンドスペース)の比率に応じて調整することにより、前記第1の突起24a及び第2の突起24bを所望の形状で形成することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のものと比較して回路面積が縮小されたヒューズ回路を提供することを課題とする。

【解決手段】ヒューズ素子と、該ヒューズ素子を溶断するに必要な電流を供給するために該ヒューズ素子の一端にそのドレイン領域又はソース領域が電気的に接続されているMOSトランジスタ素子とからなる、前記ヒューズ素子の選択的溶断により電気的にプログラム可能なヒューズ回路を備え、前記ヒューズ素子が前記MOSトランジスタ素子の形成領域の直上の絶縁膜上に位置することを特徴とする半導体装置により、上記課題を解決する。

(もっと読む)

エッチング近接効果補正モデルの作成方法、エッチング近接効果補正モデル、マスクパターンの補正方法、フォトマスク、半導体装置の製造方法、および半導体装置

【課題】エッチング近接効果に対するマスクパターンの補正を非常に高精度で行うことができるエッチング近接効果補正モデルを作成する。

【解決手段】基板の配線形成面に形成されたレジストパターンに対しリソグラフィー近接効果補正モデルを用いてシミュレーションを行うことにより算出した、該レジストパターンの線幅のシミュレーション値と、上記レジストパターンをマスクとして上記基板の配線形成面をエッチングすることにより形成した配線パターンの線幅の実測値とから、エッチングによるパターンのシフト量を算出するステップS36と、そのシフト量に対し、パターンサイズおよびパターン間スペースサイズをパラメータとする補正モデルを用いて、最小二乗法によるフィッティングを行うことにより、エッチング近接効果補正モデルを作成するステップS37〜S38と、を含む。

(もっと読む)

半導体装置

【課題】FD型トランジスタで構成された電気回路において、電気回路に電力を供給する電源のスイッチングトランジスタを基板電圧で制御することができる半導体装置を提供する。

【解決手段】半導体装置は、基板上の第1のFinに形成された第1のトランジスタを含む電気回路と、半導体基板上の第2のFinに形成され、電気回路と電源供給線との間に接続された第2のトランジスタを含む電源回路と、基板に基板電圧を印加するための基板コンタクトとを備え、第1のFinの幅は、第1のトランジスタのチャネル部に形成される最大空乏層幅の2倍以下であり、第2のFinの幅は、第2のトランジスタのチャネル部に形成される最大空乏層幅の2倍よりも大きい。

(もっと読む)

多層配線層の電源配線構造およびその製造方法

【課題】互いに交差する上下の電源配線同士を中間配線層に形成される接続用配線を介して接続する際に、中間配線層での接続用配線によって占有される信号配線の配線トラック数を少なくする多層配線層の電源配線構造を提供する。

【解決手段】中間配線層のうち第1の方向を優先配線方向とする1つの中間配線層は、同種の上層電源配線と下層電源配線との交差位置に形成される交差位置形成部と、交差位置形成部から第1の方向の異なる種類の上層電源配線側に張り出した張出部と、を有するビア位置変換接続用配線24A,24Bを有し、配線接続部は、上層配線と交差位置形成部との間と、張出部と下層配線との間と、をビア21A,23A,25A,21B,23Bを介して接続する。

(もっと読む)

半導体装置

【課題】容量素子を構成する第1電極及び第2電極を形成するためのリソグラフィ工程で重ね合わせズレが生じた場合にも容量ばらつきを抑制できる半導体装置を提供する。

【解決手段】複数の配線層L1〜L5のそれぞれは、絶縁膜103〜106と、当該絶縁膜中に相互に離隔し且つ向かい合うように埋め込まれた第1電極101及び第2電極102とを有する。一の配線層の第1電極101と、その上方又は下方に設けられた他の配線層の第2電極102とは相互に向かい合うように配置されている。一の配線層の第1電極101の幅と、他の配線層の第2電極102の幅とは異なっている。

(もっと読む)

パターン検証方法およびパターン検証プログラム

【課題】半導体集積回路の各レイヤの3次元構造を考慮しつつ、半導体集積回路を作製するために用いられるパターンデータを検証する。

【解決手段】スペック設定部15aは、半導体集積回路の各レイヤの3次元構造に基づいて、各レイヤに配置されるレイアウトパターンのレイアウトに関するスペックを設定し、検証処理部15bは、半導体集積回路の各レイヤのレイアウトパターンがスペックを満たしているかどうかを検証する。

(もっと読む)

スイッチング素子、スイッチング素子の製造方法、電子デバイス、論理集積回路及びメモリ素子

【課題】半導体プロセス親和性に優れる酸化物イオン伝導体を適用し、且つ低電圧で駆動できるスイッチング素子、スイッチング素子の製造方法、電子デバイス、論理集積回路及びメモリ素子を提供する。

【解決手段】スイッチング素子は、第1電極11と、第2電極12と、第3電極13と、酸化物を含有するイオン伝導層と、を有し、第1電極11は、イオン伝導層に電子を供給し、第1及び第3電極の少なくとも1以上の電極は、イオン伝導層に金属イオンを供給し、金属イオンは、電子を受け取ってイオン伝導層中で金属を形成し、金属は、第1及び第2電極間を接続し、第3電極13は、第1及び第2電極間を接続する金属の形成及び消去を制御し、イオン伝導層は、第1電極11と第2電極12と第3電極13とに接して設けられ、酸化物の結晶化温度で結晶化した酸化物の結晶よりも小さい結晶である微結晶を含有し、微結晶は、結晶粒界を形成することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】印加電界の履歴によって抵抗値が変化する抵抗変化層を有するスイッチ素子を多層配線中に形成し、かつ配線又は抵抗変化層の表面がダメージを受けることを抑制できるようにする。

【解決手段】この半導体装置は、第1配線層12、第2配線層16、及びスイッチビア35を備える。第1配線層12は第1配線32を有しており、第2配線層16は第2配線39を有している。スイッチビア35は、第1配線32と第2配線39を接続する。またスイッチビア35は、少なくとも底部に、抵抗変化層33を有しているスイッチ素子を有している。抵抗変化層33は、電界印加履歴に応じて抵抗値が変化する。

(もっと読む)

101 - 120 / 379

[ Back to top ]