Fターム[5F064GG03]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798) | エッチング (379)

Fターム[5F064GG03]に分類される特許

21 - 40 / 379

半導体装置の製造方法

【課題】ロジック回路を含む半導体装置に関し、処理時間を短縮し製造コストを低減する。

【解決手段】ロジック回路の形成領域(114)は、所定の精度で光近接補正処理された第1領域(114b,170)と、所定の精度より低い精度で光近接補正処理された第2領域(114a,180)とを備える。特に第1領域(114b,170)は、トランジスタとして動作するゲート配線(172)を有し、第2領域(114a,180)は、トランジスタとして動作しないダミーレイアウト(182)を有する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

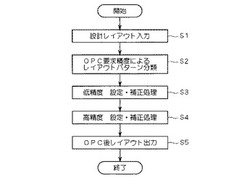

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

(もっと読む)

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】銅を主成分とする配線層を有し、かつヒューズの切断によって特性の悪化を招くことのない半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、銅を主成分とするメタル配線34と、メタル配線34よりも上層に形成された最上層配線5と、メタル配線34と最上層配線5との間を接続するためのプラグ9が形成されるプラグ形成層10に少なくとも一部が形成され、銅以外の金属材料を主成分とする導電性材料で形成されたヒューズ膜4とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置では、コンデンサの容量値が配置場所で変化するため、容量値の見積もりが煩雑になるという問題を解決する。

【解決手段】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置の補償容量部のレイアウト配置の際に、補償容量部を構成する領域に拡散層の矩形領域を配置する。また、該拡散層の矩形領域の各辺に対し、各辺の中心が直行する箇所に矩形開口部を設ける。また、該拡散層の矩形領域の中心線近傍に沿ってゲート電極を直行するように形成する。また、該拡散層の該矩形領域の四隅に上層の金属層と接続するためのコンタクトを形成する。また、該ゲート電極と該拡散層の矩形開口部の重なる箇所にゲート電極と上層の金属層を接続するコンタクトを形成する。また、該ゲート電極が直行する箇所で容量を形成する。また、補償容量の単位セルを構成する。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、半導体基板の上方に形成された半導体素子と、半導体素子の上方に形成された第1絶縁膜と、第1絶縁膜上に形成されたアルミニウム(Al)を含有する第1導電性膜よりなるヒューズ素子Fと、を有する。さらに、第1絶縁膜上に形成され、第1導電性膜よりなる第1配線と、第1配線上に形成された第2絶縁膜と、を有し、ヒューズ素子Fのプログラム領域は、第2絶縁膜に設けられた開口部OA1から露出している。また、ヒューズ素子Fのプログラム期間およびヒューズ素子にプログラムされたデータの読み出し期間以外の期間において、ヒューズ素子Fの両端を接地電位に維持する。例えば、ヒューズ素子Fの一端は、接地電位に接続され、他端は、スイッチング素子を介して接地電位に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】金属シリサイド層を利用した電気ヒューズの信頼性を向上する。

【解決手段】半導体装置50は、電気ヒューズ16を有する。電気ヒューズ16は、第1の端子領域16aと、第2の端子領域16bと、第1の端子領域16a及び第2の端子領域16bを接続するヒューズリンク領域16cとを備える。ヒューズリンク領域16cは、第1のシリコン膜12cと、第1のシリコン膜上に形成された第1の金属シリサイド層15cとを有する。平面視において、第1の端子領域16aと第2の端子領域16bとが並ぶ方向に垂直な方向の寸法を幅とするとき、第1のシリコン膜12cの少なくとも一部の幅は、第1の金属シリサイド層15cの幅よりも大きい。

(もっと読む)

半導体装置

【課題】2つの入力端子の配置形態を工夫することにより配線層の増設スペースを確保しスタンダードセルの原価低減を図る。

【解決手段】入力端子34bはゲート配線2bに接続され、入力端子34cはゲート配線2cに接続される。また、入力端子34b、34cは、Y方向に互いに近接して配置され、入力端子34bの第2コンタクト配線4bは、第1コンタクト配線3bと隣接し、且つ該第1コンタクト配線3bに対しX方向に延在する。入力端子34cの第2コンタクト配線4cは、第1コンタクト配線3cと隣接し、且つ該第1コンタクト配線3c対して第2コンタクト配線4bとは逆のX方向に延在する。即ち、入力端子34bの第1コンタクト配線3bと入力端子34cの第2コンタクト配線4cとはY方向に互いに対向して配置され、入力端子34bの第2コンタクト配線4bと入力端子34cの第1コンタクト配線3cはY方向に互いに対向して配置される。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒューズ配線を溶断する際に素子分離構造や半導体基板に与えるダメージを抑制することができる半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板10と、半導体基板の主面の面内方向に互いに離間するように形成された一対の電極12A,12Bと、これら電極12A,12Bを被覆し、上面に凹部13cを有する下層絶縁膜13と、凹部13cに形成されたヒューズ配線20Cと、下層絶縁膜13及びヒューズ配線20Cを被覆する層間絶縁膜21と、層間絶縁膜21上に形成され、ヒューズ配線20Cの直上にレーザトリミング用の開口部1hを有する上層絶縁膜31とを備える。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

21 - 40 / 379

[ Back to top ]