Fターム[5F064GG03]の内容

ICの設計・製造(配線設計等) (42,086) | 製造プロセス技術 (798) | エッチング (379)

Fターム[5F064GG03]に分類される特許

141 - 160 / 379

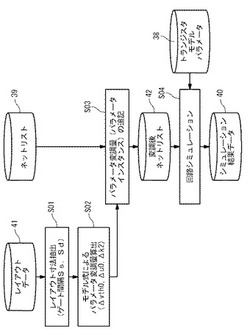

回路シミュレーション装置、回路シミュレーション方法及びプログラム

【課題】回路シミュレーションの精度を向上する。

【解決手段】回路シミュレーション装置30は、集積回路のレイアウトデータから、対象MOSトランジスタ11のゲート12と対象MOSトランジスタ11に隣接するMOSトランジスタ15、16のゲート17、18との間のゲート間隔Ss、Sdを抽出し、抽出されたゲート間隔Ss、Sdから対象MOSトランジスタ11のトランジスタモデルパラメータvth0’を算出するパラメータ算出手段と、算出されたトランジスタモデルパラメータvth0’を用いて前記集積回路の回路シミュレーションを行う回路シミュレーション手段とを備える。

(もっと読む)

パターン形成不良領域算出方法およびパターンレイアウト評価方法

【課題】段差パターンに起因するパターン形成不良領域を、段差パターンレイアウト面内で正確かつ短時間に算出する露光不良領域算出方法を得ること。

【解決手段】基板上の段差パターンとしてゲートG1を形成した後、ゲートG1よりも後にピラーパターンPを形成するとピラーパターンPがパターン形成不良となる領域を不良発生危険度マップ21として算出するために、基板面内でのゲートG1のパターンからの距離と露光不良領域となる可能性に関する情報との対応関係と、ゲートG1のパターン形成に用いたレイアウトと、を用いる。

(もっと読む)

半導体装置の製造方法

【課題】高集積化が容易で製造コストが増加しないヒューズ回路を有する半導体装置の構造及びその製造方法、並びに、このようなヒューズの切断に適したレーザ装置を提供する。

【解決手段】下地基板10上に形成されたブロック層12と、ブロック層12上に形成された絶縁膜14と、絶縁膜14上に形成されたヒューズ22とにより半導体装置を構成する。ヒューズ22の下層部にブロック層12を設けることにより、レーザアブレーションによりヒューズを切断し、且つ、ブロック層12によってレーザアブレーションを制御性よく停止することができる。

(もっと読む)

半導体チップ

【課題】 加工処理を行なうための加工位置を精度よく特定することができる半導体チップを提供する。

【解決手段】 複数の半導体回路素子が形成され、それら半導体回路素子上に層間絶縁膜と配線層とが交互に積層されてなる半導体チップ10において、この半導体チップ10を構成する最上層の配線層であるダミーメタル13に、半導体チップ10上のX座標の位置を表わすX座標用コードパターン13_1およびY座標の位置を表わすY座標用コードパターン13_2を付加した。

(もっと読む)

半導体装置及びその製造方法

【課題】追加工程なくフューズ下に配線等を配置可能な半導体装置及びその製造方法を提供する。

【解決手段】この半導体装置は、絶縁層に設けられた複数の第1キャパシタ孔52と、第1キャパシタ孔52に形成された容量素子Cと、容量素子Cと結合するトランジスタTrとからなるDRAMセルと、絶縁層に設けられた複数の第2キャパシタ孔40と、第2キャパシタ孔40の間に形成されるフューズ素子(31、51)と、を備えている。

(もっと読む)

膜厚予測方法、レイアウト設計方法、露光用マスクのマスクパターン設計方法、及び、半導体集積回路の作製方法

【課題】回路パターンの上に形成される薄膜の膜厚をより正確に予測し得る膜厚予測方法を提供する。

【解決手段】膜厚予測方法にあっては、第2の被処理層の断面形状に関する第1の実測データベース、回路パターンの周辺長と第2の被処理層の厚さとの関係に関する第2の実測データベース、第2の被処理層の平坦化レートに関する第3の実測データベース、第2の被処理層の基準膜厚Tblkを予め求めておき、基板の上に形成すべき第1の被処理層を所定の大きさの碁盤目状のメッシュに区切り、各メッシュ(i,j)におけるパターン面積率αij、回路パターンの周辺長Lij、第2の被処理層の初期厚さT2_INI_ij、基準膜厚Tblk、第1の実測データベース、第2の実測データベース及び第3の実測データベースに基づき、第2の被処理層の初期膜厚予測値Prij及び第2の被処理層の平坦化量Hijを求め、第2の被処理層を平坦化した後の第2の被処理層の膜厚を予測する。

(もっと読む)

見込み欠陥位置同定方法、見込み欠陥位置同定ツール

【課題】欠陥同定ツールが開示される。

【解決手段】欠陥同定ツールは、微小デバイス内の欠陥が生じ易い位置を予測する。前記ツールは、欠陥の種類及び欠陥が生じ易い個々のネットリストの両方を同定し得る。試験回路生成ツールは、次に続いて、この欠陥情報を用い、微小回路の同定された部分内の欠陥を試験する試験回路を生成する。同様に、自動試験パターン生成ツールは、欠陥位置情報を用い、微小回路の指定部分内の同定された欠陥に対応する故障を検査するために特別に作成された試験データを生成し得る。ツールの種々の実施は、製造過程の欠損又は不具合のような器材誤差により生じる欠陥が生じ易い位置及び無秩序に作られる欠陥が生じ易い位置の両方を同定するために利用されて良い。

(もっと読む)

半導体装置及びその製造方法

【課題】レーザ照射により切断されるヒューズを備えた半導体装置において、レーザの反射率の増加を抑えてヒューズへ加わるエネルギーの低下を抑制することにより、ヒューズの飛散を防止できるようにする。

【解決手段】絶縁膜1上に、密着層2a、メタル層3a及びTiN反射防止膜4aから構成されるヒューズ11が形成されている。ヒューズ11を覆うように絶縁膜1上にシリコン酸化膜5が形成されている。シリコン酸化膜5上にシリコン窒化膜8が形成されている。ヒューズ11上に位置するシリコン酸化膜5aにおけるヒューズ11の短辺方向の断面は三角形状を有している。

(もっと読む)

半導体装置および光電変換システム

【課題】相対的な精度が要求される複数個の回路素子のそれぞれの特性が高い整合性を持つようにすることが可能な半導体装置を提供する。

【解決手段】この半導体装置10は、所定数のMOSトランジスタ素子2を含む入力側回路素子10aと、入力側回路素子10aに含まれるMOSトランジスタ素子2の数とは異なる数のMOSトランジスタ素子2を含む出力側回路素子10bとを備えている。入力側回路素子10aおよび出力側回路素子10bは相対的な精度が要求されるものであり、入力側回路素子10aおよび出力側回路素子10bからなる回路素子は、互いに同一の形状で、かつ、同一のサイズを有する複数個の活性領域3のうちの少なくとも1個の活性領域に2個以上のMOSトランジスタ素子2が形成され、複数個の活性領域3のうちの他の活性領域3のそれぞれに残りのMOSトランジスタ素子2が形成された構造となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】コーナー部を有する微細金属配線を備えた半導体装置の信頼性を向上させることを目的とする。

【解決手段】第1層間絶縁膜82に埋め込まれ、屈曲したコーナー部を有する第1配線21を一定のコーナー数毎に区切る。区切った第1配線21同士は、第2層間絶縁膜87に埋め込まれたプラグ22及び第2配線23によって連結する。第1配線はコーナー部により結晶粒径が減少するが、一定のコーナー部数で短く区切られるためエレクトロマイグレーション耐性が向上する。また、第2配線23の配線幅を調整することにより、第1配線21のコーナー部による抵抗上昇を、第2配線23で補償することができる。

(もっと読む)

半導体装置

【課題】ダマシン構造を有し、屈曲部を有する配線パターンの抵抗値を低減する。

【解決手段】半導体装置は、活性素子を含む基板と、前記基板上方に形成され、配線層と層間絶縁膜を含む多層配線構造と、を備え、前記配線層は、前記層間絶縁膜中に形成されたダマシン構造の配線パターンを有し、前記配線パターンは、第1の配線幅でそれぞれの方向に延在する複数の延在部と、各々前記複数の延在部のうちの2つを接続する複数の屈曲部を含み、前記複数の屈曲部の少なくとも一つは、前記第1の配線幅の√2倍よりも大きい第2の配線幅を有する。

(もっと読む)

ダミー・フィル構造、方法、ダミー・フィル形状発生器及び設計構造(スペーサ・フィル構造、デバイス変動を減少するための方法及び設計構造)

【課題】 ダミー・フィル形状を有する構造を提供する。

【解決手段】 本発明は、スペーサ・フィル構造(100及び300)のための設計構造(図1)を提供する。更に具体的にいうならば、本発明は、スペーサ・フィル構造(100及び300)、並びにデバイス変動を減少するための設計構造及び製造方法を提供する。構造は、デバイスの異なる領域に設けられた複数のダミー・フィル形状(100)を含み、このダミー・フィル形状は、ゲート周囲長及びゲート面積の比がチップに亘って一様な総周辺密度を生じるように構成されている。

(もっと読む)

設計レイアウトデータ作成方法および半導体装置の製造方法

【課題】加工変換差のばらつきを抑えたフォトマスクのレイアウトデータを短時間で作成することができるレイアウトデータ作成方法を得ること。

【解決手段】半導体装置に形成するパターンの設計レイアウトデータを作成する設計レイアウトデータ作成方法において、設計レイアウトデータに対応するパターンをウェハ上に形成した場合にウェハ上に形成されるパターンがウェハ面内で所定範囲内のパターン被覆率となり、かつ設計レイアウトデータに対応するパターンをウェハ上に形成した場合にウェハ上に形成されるパターンの合計周囲長がウェハ面内で所定範囲内のパターン周囲長となるよう、半導体装置の製品パターン以外のダミーパターン領域D2にダミーパターンdyを配置して設計レイアウトデータを作成する。

(もっと読む)

半導体集積回路の設計方法、製造方法、回路設計プログラム、及び半導体集積回路

【課題】レイアウト修正による遅延変動を抑制しつつ半導体集積回路のプラズマダメージを軽減する製造方法を提供する。

【解決手段】半導体集積回路の製造方法は、コンピュータによって実行され、第1ゲート電極21に接続する金属配線と、第1ゲート電極21とのアンテナ比を検証するステップと、アンテナ比の検証結果に基づいて半導体集積回路のレイアウトを変更するステップとを具備する。レイアウトを変更するステップは、複数の論理セルから、アンテナ比の検証結果に応じたゲート面積の論理セルを選択するステップと、論理セルを、論理動作しないフィルセル40として空き領域に配置するステップと、フィルセル内の第2ゲート電極41を金属配線に接続するステップとを備える。

(もっと読む)

磁気素子及び集積回路並びに磁気ランダムアクセスメモリ

【課題】磁気素子本体に電流を流すことなく、磁性体電極の磁化反転が可能な磁気素子及び集積回路並びに磁気ランダムアクセスメモリを提供する。

【解決手段】磁気素子1は、基板6上に第1の強磁性体電極3及び第2の強磁性体電極4を隔置し磁気素子本体2と、第1の強磁性体電極3に接触して高スピンホール効果を有する電極5を配設し、高スピンホール効果を有する電極5に電流を流して第1の強磁性体電極3へスピン注入して磁化反転する。磁気素子本体2へ電流を流すのではなく、高スピンホール効果を有する電極5に電流を流すことでスピンホール効果によるスピン分極を発生させ、第1の強磁性体電極3への移行により磁化反転できる。高インピーダンスの微小磁気メモリ素子及び磁気論理素子やスピン電界効果トランジスタを多段に接続した再構成可能微小磁気論理素子の磁化反転が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】抵抗素子を備えた半導体集積回路の製造において、抵抗素子の抵抗値バラツキを抑えた製造方法を提供する。

【解決手段】抵抗素子形成工程に等倍露光機を用い一定周期毎に抵抗値の面内バラツキを測定し、そのバラツキを前述の等倍露光機のマスク(レチクル)に寸法補正として反映させることによって、抵抗値のバラツキを抑えた抵抗素子の製造を可能とする。

(もっと読む)

回路構造とそれを定義するためのフォトマスク

【課題】フォトマスクパターンがOPCによって従来技術よりも更に容易に補正できるラインとピックアップパッドとを含む回路構造およびそのフォトマスクを提供する。

【解決手段】回路構造とそれを定義するフォトマスクを提供する。回路構造が複数のピックアップパッド320と平行な複数のライン310とを含み、連続的に配列されたラインの一部にそれぞれ1つのピックアップパッドが配置される。1つのピックアップパッドを配置された任意のラインのピックアップパッドが、ラインの一側において隣接するラインの不連続点330を通過して、次のラインに接続される。フォトマスクが上記ラインを定義する複数のラインパターンと前記ピックアップパッドを定義する複数のピックアップパッド定義パターンとを有する。

(もっと読む)

半導体装置

【課題】トリプル・ウェル構造を有する半導体装置において、製造歩留まり及び製品信頼性を向上させることのできる技術を提供する。

【解決手段】p型の基板Sub内に形成された深いn型ウェルDNW0、浅いp型ウェルPW及び浅いn型ウェルNWが形成された領域と異なる領域に浅いp型ウェルPW100を形成し、この浅いp型ウェルPW100内に形成されたp型拡散タップPD100と、深いn型ウェルDNW0内の浅いn型ウェルNW0内に形成されたp型拡散タップPD0とを第2層目の配線を用いて結線し、深いn型ウェルDNW0内に形成されたnMIS200nのゲート電極及びpMIS200pのゲート電極と、基板Sub内に形成されたnMIS100nのドレイン電極及びpMIS100pのドレイン電極とを第2層目以上の配線を用いて結線する。

(もっと読む)

回路装置および制御方法

【課題】イオン伝導層を用いたイオン伝導素子をより高速に動作させる。

【解決手段】第1電極101と、第2電極102と、第1電極101および第2電極102の間に配置されたイオン伝導層103とを備えるイオン伝導素子と、このイオン伝導素子に、正電圧の印加および負電圧の印加を行うことでイオン伝導素子の動作を制御する両極動作制御部104と、第1電極101に、異なる電圧の負電圧を印加することでイオン伝導素子の動作を制御する単極動作制御部105とを備える。

(もっと読む)

半導体装置およびその製造方法

【目的】ジャンクションブロックを不要とし、またワイヤーハーネスの占有スペースを縮小化し、過電流となった主電流を確実に遮断できて、電気経路を確実に開放できるヒューズ素子を半導体基板内に形成した半導体装置およびその製造方法を提供する。

【解決手段】p半導体基板1に形成したトレンチ18の内壁にシリコン酸化膜21を介してヒューズ素子22を形成し、トレンチ18の開口部を塞ぐようにポリイミド膜23を被覆することで、溶断したヒューズ素子22が再度固化したときに、固化したヒューズ材で第1表面端子aと第2表面端子bの間を短絡しないようにする。半導体装置内にヒューズ素子22を有することで、ジャンクションブロックを不要とし、またワイヤーハーネスの占有スペースを縮小化できる。

(もっと読む)

141 - 160 / 379

[ Back to top ]