Fターム[5F064HH01]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ハードウェア関係 (668)

Fターム[5F064HH01]の下位に属するFターム

Fターム[5F064HH01]に分類される特許

41 - 60 / 345

設計ライブラリデータベース

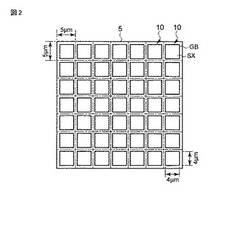

【課題】結晶化半導体薄膜に対して適正かつ効率的なフォトマスクの作成を可能にする。

【解決手段】1実施形態に係る設計ライブラリデータベースは、2次元的に区画して各々薄膜トランジスタのチャネル領域のサイズを超える複数の結晶粒規定領域が配置された結晶化半導体薄膜を用いる薄膜トランジスタ回路の設計ライブラリデータベースであって、各々のチャネル領域が単一の前記結晶粒規定領域内の固定位置に配置される2個以上の薄膜トランジスタおよび前記2個以上の薄膜トランジスタを相互接続する配線を含む様々な論理ゲート回路をそれぞれ表す複数のスタンダードセル、並びに前記様々な論理ゲート回路の様々な組み合わせをそれぞれ表す複数のマクロセルの少なくとも一方のセルのライブラリ、および前記複数の結晶粒規定領域が配置された結晶化アレイパターンのスタンダードセルのライブラリを含みハードディスクに登録される。

(もっと読む)

LSIの電源遮断領域拡張方法及びそのプログラム

【課題】LSIにおける電源遮断領域を拡張する方法及びそのプログラムを提供する。

【解決手段】回路要素とネット情報とを記述したハードウエア記述ファイルに対して,電源遮断領域の入力端子Aから第1のノードBであるラッチ回路または入力ポートをトレースによって抽出し,さらに,遮断領域の出力端子に接続される第1のアイソレーションセルの出力端子A’から第2のノードB’であるラッチ回路または出力ポートをトレースによって抽出する第1の抽出工程と,第1のノードBから第3のノードCとなるラッチ回路または出力ポートをトレースによって抽出し,さらに,第2のノードB’から第4のノードC’であるラッチ回路または入力ポートをトレースによって抽出する第2の抽出工程とにより,無駄に動作する組み合せ回路を抽出し、前記回路をハードウエア記述ファイルと電源仕様ファイルに追加するとともに,アイソレーションセルを移動する工程とを有する。

(もっと読む)

回路設計装置、回路設計プログラム及び回路設計方法

【課題】効率的且つ十分に低消費電力化を行なうことを課題とする。

【解決手段】回路設計装置は、回路に含まれるFFのうち、動作していないFFを抽出し、抽出されたFFに対する制御信号の出力元である無動作起因端子を探索する。また、回路設計装置は、無動作起因端子が同一となるFFを1つのドメインとしてドメイン化し、ドメイン化されたFFそれぞれについてバックトレースを実施する。また、回路設計装置は、バックトレースにおいてFFに到達するまでに存在する組み合わせ回路を抽出する。また、回路設計装置は、到達したFFのうち同一ドメインでないFFそれぞれについてフォワードトレースを実施し、到達したFFが同一ドメインである場合に該当する組み合わせ回路も同一ドメインとしてドメイン化する。

(もっと読む)

半導体集積回路設計装置、該設計装置に用いられる配線設計方法及び配線設計プログラム

【課題】半導体集積回路の配線設計において、配線領域上の配線要求群に対して配線経路探索を効率的に行う半導体集積回路設計装置を提供する。

【解決手段】チップ情報記憶部19により、ネットリスト及び配線格子情報が記憶される。配線要求クラスタリング部12により、配線要求クラスタが生成される。配線格子クラスタリング部13により、配線格子クラスタが生成される。配線経路探索繰返し手段(配線経路探索部14、配線要求クラスタ分解部15、経路探索終了条件判定部16、配線格子クラスタ分解部17、配線格子レベル判定部18)により、配線要求クラスタに対する配線経路探索が配線格子クラスタ上で行われ、配線要求クラスタの分解、配線格子クラスタの分解及び配線経路探索が、配線経路探索用の配線格子が最細粒度配線格子のレベルに分解されるまで繰り返される。

(もっと読む)

アサーションベース検証装置、およびアサーションベース検証方法

【課題】大規模で複雑化した半導体集積回路に対する機能検証を効率よく実行しつつ、検証対象の半導体集積回路の品質を向上させる技術を提供する。

【解決手段】論理シミュレーション実行部(15)(17)の機能によって、制御可アサーション記述ファイル(25)の、処理対象アサーション記述と処理非対象アサーション記述とを特定する。処理対象アサーション記述を用いてDUT(22)に対するアサーションベース検証を実行しつつ、発火条件を満足したか否かを判定した結果に基づいて発火情報レジスタ(28)を書き換える。発火情報レジスタ(28)のデータに基づいてアサーション制御情報(27)を更新して新たなアサーション制御情報(27)とし、新たなアサーション制御情報(27)を用いてアサーションベース検証を実行する。

(もっと読む)

高耐圧配線、配線設計装置および方法

【課題】層間絶縁膜を厚くすることなく、放電耐圧を向上させ、デバイスの特性の安定化や性能の向上を図る。

【解決手段】高耐圧配線は、Si基板101上に形成された配線層103と、絶縁膜104と、上層配線105,106と、絶縁膜104に形成された溝107とを有する。配線層103上の絶縁膜104の厚さTは、上層配線105と106間の距離dよりも小さく、溝の幅Wは、距離dよりも小さい。絶縁膜104の厚さTは、配線層103と上層配線105,106との間に与えられる最大の電位差Vmaxよりも絶縁膜104の耐圧が大きくなるように設定され、絶縁膜104の露出量Xは、溝の幅Wと距離dとが等しいときの絶縁膜104に沿った沿面放電開始電圧をV0(V0=b×lnT+c、b,cは定数)としたとき、Vmax<aX+V0(aは定数)となるように設定される。

(もっと読む)

タイミング解析方法、タイミング解析プログラム

【課題】実際に即した配線OCVp係数を用い、タイミング解析の精度を向上させる。

【解決手段】配線OCVp係数を用いて配線遅延値を補正することにより、設計回路に含まれる第1パスと第2パスとの間の遅延差を検証する。配線OCVp係数の変動成分ΔOCVpは、配線のグローバルばらつきに起因するΔOCVp_λと、同層の配線のローカルばらつきに起因するΔOCVp_θと、異層間の配線のローカルばらつきに起因するΔOCVp_ωと、を含む。ΔOCVp_λは、それぞれのパスを構成する配線の各配線層における配線長に依存する。ΔOCVp_θは、上記配線長に加えてパス間距離に依存する。ΔOCVp_ωは、上記配線長に加えてチップサイズに依存する。それら配線長、パス間距離、及びチップサイズを示すデータを読み出し、読み出されたデータを用いて配線OCVp係数を算出し、算出された配線OCVp係数を配線遅延値に適用する。

(もっと読む)

半導体装置の配線抵抗算出装置

【課題】配線に多数のスルーホールが存在する場合にも、多数のスルーホール分割要素に分割されることを回避し、分割要素の数の増大を抑制し、配線抵抗の算出時間を短縮する装置の提供。

【解決手段】第1配線層と第2配線層の配線を接続する複数のスルーホールを有する領域に、複数のスルーホールを含む枠図形FF1を設定し、枠図形を複数の枠領域FR1〜3に分割する。各枠領域内の複数のスルーホールを合成して1つのスルーホールにまとめ、各枠領域内にはそれぞれ1つの合成スルーホールCT1〜3が設定される。各枠領域に1つに設定されたスルーホールの位置を基準として、第1配線層、第2配線層における枠図形に対応する配線抵抗を分割した抵抗値RL11〜14、RL21〜22と、各枠領域内で1つに設定されたスルーホールの抵抗値RCT1〜3とを用いて、抵抗回路網を作成し、抵抗回路網を1つの抵抗RSに合成する。

(もっと読む)

半導体装置の設計方法及び製造方法

【課題】トランジスタ等の電気的特性のばらつきを低減し得る半導体装置の設計方法及び半導体装置の製造方法を提供する。

【解決手段】素子領域の実パターンである複数の第1の実パターンと、ゲート配線の実パターンである複数の第2の実パターンとを配置するステップと、レイアウト領域を複数の分割領域に分割するステップと、レイアウト領域内に、ダミーの素子領域のパターンである複数の第1のダミーパターンと、ダミーのゲート配線のパターンである複数の第2のダミーパターンとを配置するステップであって、分割領域内における第1の実パターン、第2の実パターン、第1のダミーパターン及び第2のダミーパターンの周囲長の総和の、分割領域間におけるばらつきが、所定の範囲内となるように、第1のダミーパターン及び第2のダミーパターンを配置する。

(もっと読む)

再構成可能なプロセッサーのシミュレーション装置及び方法

【課題】 アプリケーションを実行するプロセッサーの性能を評価したりあるいはそのプロセッサーで最適に実行可能なアプリケーションを作成するために使用されるプロセッサーのシミュレーション技術が開示される。

【解決手段】 いくつかの機能ユニットを含んでいる再構成可能プロセッサーのシミュレーション装置はオペランドを生成する機能ユニットとそのオペランドを消耗する機能ユニットの間のルーティング経路をキューで表現してプロセッサーをモデリングする。これらのキューのサイジュは機能ユニットの間のルーティングのディレーに関する情報とスケジューラーから受信したモジューロスケジューリングによる循環ループのステージ情報をもとに決定される。各ルーティングキューの動作に関するホスト向バイナリコードを保存するモデリングコードDBを備えており、バイナリファイルの代わりに対応するホスト向バイナリコードを実行してシミュレーションする。

(もっと読む)

半導体集積回路装置の設計方法

【課題】タイミング最適化後のタイミング、および面積を見積もることにより、タイミング最適化後のセルの配置変更を大幅に低減し、レイアウト設計にかかる期間を短縮する。

【解決手段】ネットリスト1、タイミング制約2、フロアプラン3、レイアウトライブラリ4、およびタイミングライブラリ5などを用いた初期配置処理中に、タイミング最適化後のタイミング、面積を見積もるためのタイミング・面積見積もり用ライブラリを予め作成しておき、タイミング制約2を満たすことができるかを見積もる。タイミング制約2を満たすことが困難なパスにあるセルは、近接配置し、逆に容易なパスは離して配置する。その際、面積増加も見積もり、配線混雑が発生しないようにする。

(もっと読む)

基板の配線設計方法及びプログラム

【課題】配線設計において、簡易的に配線混雑を回避することが可能な配線設計方法を提供することを目的とする。

【解決手段】複数の第1方向配線の配線層及び複数の第2方向配線の配線層を備える基板対して概略配線を行い、基板を複数のタイルに分割し、複数のタイルに対応するように、複数の第1方向配線の配線層及び複数の第2方向配線の配線層を分割して、複数の第1方向配線の部分配線領域と、複数の第2方向配線の部分配線領域と、を形成し、タイルにおける第1方向配線がオーバーフローしている場合には、このタイルに対応する第2方向配線の部分配線領域を、第1方向配線の部分配線領域に変更する。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びレイアウト設計プログラム

【課題】

複数階層を有する半導体集積回路の階層レイアウトを行なう際に、複数個所で使用される下位モジュールについての各配置箇所における下位モジュール近傍の上位階層の配線状況を考慮して、下位モジュールのレイアウト設計を行なうことを課題とする。

【解決手段】

上記課題を解決するために、本発明に係るレイアウト設計装置は、複数階層を有する半導体集積回路のレイアウト設計装置であって、複数個所で使用される下位モジュールについて、前記下位モジュールが配置される上位モジュール内のそれぞれの配置箇所近傍の上位階層の配線情報を抽出し、抽出した上位階層の配線情報を、前記下位モジュールのレイアウト設計を行なう際の配線禁止領域として設定し、前記下位モジュールのレイアウトを行なう。

(もっと読む)

半導体回路の設計装置および設計方法

【課題】配線のしやすさを損なうことなく、ビアの不良による歩留まりの低下を抑制可能な半導体回路の設計装置および設計方法を提供する。

【解決手段】半導体回路の設計方法は、論理回路を構成するセルの配置およびセル間の配線を行い、複数箇所にビアが設けられる配線を含むレイアウトパターンを生成するステップ(ステップS1、S2)と、ビアから、配線上の信号を受信するレシーバセルまでの負荷容量をビア毎に算出するステップ(ステップS4)と、ビアごとの、負荷容量に基づいて、負荷容量が大きいビアを優先的に低抵抗のビアに置換するステップ(ステップS6、S7)を備える。

(もっと読む)

ガードリング設計装置、ガードリング設計方法、プログラム及び記録媒体

【課題】半導体集積回路の素子及び配線のレイアウトにおけるガードリングの設計の自由度を高める。

【解決手段】設計装置は、デザインルールを記憶するデザインルール記憶部11、予め設計されたレイアウトを記憶するレイアウト記憶部12、デザインルールに適合したガードリング幅を設定幅として設定するガードリング幅設定部21、レイアウト上にガードリングの形成経路を指定するための経路指定部32、指定経路に基づいてガードリング形成経路を認識する経路認識部22、ガードリング形成用のレイヤーリストを記憶するガードリング形成用レイヤー記憶部13、認識経路の下地レイヤーに応じたガードリング形成用のレイヤーを設定するガードリング形成用レイヤー設定部23及び認識経路に設定幅で設定レイヤーを反映させてガードリングを生成するガードリング生成部24を備えている。

(もっと読む)

回路シミュレータおよび半導体装置の設計方法

【課題】インパクトイオン化電流の算出精度を向上させる。

【解決手段】飽和ソース−ドレイン電圧Vdsatがソース−ゲート電圧Vgsおよびソース−ドレイン電圧Vdsの関数にて与えられたドレイン横方向電界Edの計算式に基づいて電界効果トランジスタのインパクトイオン化電流Iiiを計算する。

(もっと読む)

フロアプランデータ生成装置及び方法

【課題】チップの設計期間を短縮する。

【解決手段】CPU1は、設計対象の回路を構成するセルのうち、所定のサイズより大きいセルサイズを有するセルのみの回路情報をゲートレベルで記述した簡易ネットリスト43と、所定のサイズより大きいセルサイズを有するセルのみの仕様データを含むセルリスト44とを用いてフロアプランを行い、仮フロアプランデータ47を生成する。CPU1は、ユーザによって回路全体のフロアプランが行われるときに、回路を構成するセルの仕様データである全体ライブラリ42と、回路を構成するセルの回路情報をゲートレベルで記述した全体ネットリスト45と、仮フロアプランデータ47と、簡易ネットリスト43を全体ネットリスト45に整合させるためのセルリスト44とを出力する。

(もっと読む)

半導体集積回路のレイアウト装置及びレイアウト方法

【課題】集積度の高い半導体集積回路の場合でもレイアウト設計における配線に係る時間を短縮する。

【解決手段】半導体集積回路のレイアウト方法は、回路構成要素の配置された領域へ配線を実施後に、予め設定された条件よりも配線が混雑する配線混雑箇所を抽出するステップと、配線混雑箇所を含む領域に、配線の実施が禁止される複数の配線禁止領域を生成するステップと、複数の配線禁止領域を迂回して配線を実施するステップと、迂回して配線を実施した後に、複数の配線禁止領域を削除するステップと、複数の配線禁止領域を削除した後に、再配線を実施するステップとを具備する。複数の配線禁止領域を生成するステップは、配線層毎に、配線の混雑に対応した領域内に配線禁止領域を発生させる割合に基づいて、複数の配線禁止領域の大きさ及び間隔を算出するステップと、算出結果に基づいて、領域に複数の配線禁止領域を生成するステップとを備える。

(もっと読む)

多電源集積回路設計装置およびその方法、ならびに、多電源集積回路製造方法

【課題】異電源ドメイン間におけるタイミング収束性が改善された回路設計を容易に行うことができる多電源集積回路設計装置の提供。

【解決手段】回路構成情報および電源構成情報に基づいて、異電源ドメインと接続するデータパスに対し、最初および最後に接続される同期式フリップフロップである境界FFの少なくともいずれかを抽出して、境界FFデータとして出力する境界FF抽出部と、回路構成情報および境界FFデータに基づいて、境界FFに接続されたクロックラインに配されたバッファを抽出し、入力を分岐させて当該分岐を入力とする新たなバッファを追加するバッファ追加部と、境界FFが新たなバッファに接続されるようにクロックラインを繋ぎ換えるように、回路構成情報を変更して、変更された回路構成情報のデータを出力するクロックライン再構成部と、を有する多電源集積回路設計装置。

(もっと読む)

設計支援方法

【課題】開発期間の短縮を図ること。

【解決手段】設計支援装置は、実回路レイアウト25から認識したデバイスのレイアウトデータについて、そのデバイスを含む所定領域内の着目パターンのエッジを格子分割し、各格子に含まれるエッジの有効無効を判定する。次に、設計支援装置は、判定結果に応じて着目パターンに対する形状情報を含む格子テーブルを生成する。そして、設計支援装置は、評価レイアウト22に基づいてエッジ位置に対するデバイスの特性変動に対応する重み付け情報を格子位置に関連付けた形状依存テーブル24と、格子テーブルとに基づいてデバイスの形状に応じた特性変動量を算出する。

(もっと読む)

41 - 60 / 345

[ Back to top ]