Fターム[5F064HH01]の内容

ICの設計・製造(配線設計等) (42,086) | 設計、製造における計算機技術 (6,629) | ハードウェア関係 (668)

Fターム[5F064HH01]の下位に属するFターム

Fターム[5F064HH01]に分類される特許

21 - 40 / 345

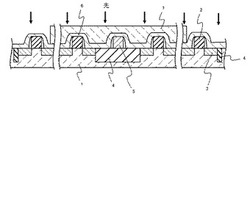

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

静的タイミング解析装置及び静的タイミング解析方法

【課題】静的タイミング解析の所要時間の短縮。

【解決手段】静的タイミング解析装置は、時刻関数生成部12と、スラック関数生成部13と、電源ドメイン電圧定数決定部14と、スラック値計算部15と、出力部16と、を備える。時刻関数生成部12は、ネットリストと、セルの遅延時間情報と、タイミング制約情報と、電源ドメインとその電源電圧範囲との対応関係を示す電源ドメイン情報とに基づいて、電源電圧の関数である、セルへの信号到着時刻を表す時刻関数を生成する。スラック関数生成部13は、タイミング制約情報及び時刻関数に基づいて、セルへの信号到着時刻の余裕度を示す電源電圧の関数であるスラック関数を生成する。電源ドメイン電圧定数決定部14は、電源電圧の下限電源電圧と上限電源電圧の間でスラック関数が最小となる電源電圧定数を決定し、スラック値計算部15は、スラック関数に電源ドメイン電圧定数を代入し、スラック値を計算する。

(もっと読む)

自動配置配線装置および自動配置配線方法

【課題】複数の電源電圧を有する半導体装置設計の自動化による作業工数の削減とレイアウト面積の省面積化を図ることが可能な自動配置配線装置を提供する。

【解決手段】処理部は、自動配置の結果から複数のセル間を接続する複数の配線経路であって、第1のパワードメイン中のセルから第2のパワードメイン中のセルへ接続される配線経路を抽出する(16)。処理部は、第1のパワードメインと第2のパワードメインとの各々の動作モード毎の電源活性情報を抽出し(17)、第1のパワードメインと第2のパワードメインとが活性状態であるときに活性状態である第3のパワードメインを抽出し(18)、特定セルの仕様項目違反を解消するために、第3のパワードメインに追加セルを挿入し(19)、かつ、第1のパワードメイン中の特定セルと第2のパワードメイン中の特定セルとの間を追加セルを経由して配線する(22)。

(もっと読む)

クロックツリー設計装置及びクロックツリー設計方法

【課題】クロックレイテンシを最小にする条件下において、クロックスキュー及びバッファ数を比較的少なくする。

【解決手段】実施形態のクロックツリー設計装置は、ターゲットシンクからのマンハッタン距離と最遠シンクからのマンハッタン距離とが等しくなる等距離点の集合を求める等距離点集合算出部と、クロックパスのパス長を最短のマンハッタン距離にするパス設定ブロック領域を設定するパス設定ブロック設定部と、等距離点の集合のうちパス設定ブロック領域内でクロックソースから最も遠い距離の点を分岐点とする分岐点設定部と、クロックソースから分岐点までのパス設定ブロック領域内にターゲットシンクと最遠シンクとの共有パスを設定すると共に、分岐点からターゲットシンクまでのクロックパス及び分岐点から最遠シンクまでのクロックパスをパス長が最短のマンハッタン距離となるように設定するパス設定部とを具備する。

(もっと読む)

半導体装置の設計支援装置、設計支援プログラム及びレイアウト情報生成方法

【課題】従来の設計支援装置により生成したインダクタは、周囲の回路の影響により特性ずれが生じる問題があった。

【解決手段】本発明の設計支援装置は、生成対象のインダクタに接続される接続対象回路領域の第1、第2の接続端子の位置情報を回路設計情報から生成されるフロアプラン結果から得て、インダクタを他の回路と接続する第3、第4の接続端子を、第1の接続端子と第3の接続端子との間及び第2の接続端子と第4の接続端子との間が最短の配線によって接続可能な位置に設定する端子位置設定部10と、第3、第4の接続端子の位置を基準としてインダクタの配線パターンを生成し、当該配線パターンに基づきインダクタのレイアウト情報を生成するパターン生成部13と、を有する。

(もっと読む)

論理回路の遅延計算・タイミング検証方法および遅延検証装置

【課題】より実動作に近いタイミング判定を行う。

【解決手段】遅延計算・タイミング検証方法は、被検証回路を示すネットリストを保持するステップと、被検証回路に含まれる順序回路間のパスを抽出するステップと、順序回路の出力がメタステーブル状態になることを許容して設定されるセットアップ時間およびホールド時間を示す緩和制約時間に対する入力信号のタイミング余裕度を算出するステップと、タイミング余裕度に基づいて、順序回路の出力信号の値が確定する出力遅延時間を算出するステップと、順序回路間のパスにおける遅延時間を示す伝搬遅延時間を算出するステップと、出力遅延時間と伝搬遅延時間と緩和制約時間とに基づいてタイミング検証するステップとを具備する。

(もっと読む)

半導体集積回路の設計方法及び半導体集積回路の設計支援装置

【課題】論理回路の面積縮小化を実現しつつ、設計TATの短縮を可能とする技術を提供する。

【解決手段】複合論理マクロセルを、基本マクロセルに置き換えて面積の総和を抽出し、その面積の総和と複合論理マクロセルの面積とを比較して面積縮小化に有効となる複合論理マクロセルを選択する。その選択された複合論理マクロセルにフラグを設定する。フラグを設定したマクロセルと同等の論理を論理情報から検索する論理構造検索処理を行い、置換対象となる基本マクロセルにフラグを設定する。置換対象のフラグを設定した基本マクロセルを、フラグ設定した複合論理マクロセルに置き換える等価論理置換処理を行う。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】LSIのレイアウト設計において、TAT(Turn Around Time)を増加させることなくタイミング収束を実現する。

【解決手段】LSIのレイアウト設計方法は、レイアウト対象の集積回路のネットリストに基づいて、前記集積回路をクロックドメインに分けることでクロックドメイン回路集合体に区分する工程と、前記クロックドメイン回路集合体の各々に対するタイミング制約を作成する工程と、所定の基準に基づいて前記クロックドメイン回路集合体間の配置順序を決定する工程と、前記クロックドメイン回路集合体を前記配置順序に従って配置し配線することにより前記集積回路のレイアウトを作成する工程とを備える。レイアウト設計後のタイミング収束のTATを短縮することが可能となる。

(もっと読む)

タイミング解析方法、タイミング解析装置、およびタイミング解析プログラム

【課題】遅延計算に要する処理時間を短縮して、タイミング解析全体に要する処理時間を短縮可能とする。

【解決手段】タイミング解析方法は、半導体チップ上にレイアウトされた回路に対して電圧降下解析を行い、電圧降下解析結果に基づいて、チップ上の電圧降下を所定の電圧範囲ごとの領域として電圧降下領域ファイルを作成し、遅延のばらつきを表現する第1OCV係数が電圧降下を考慮して所定の電圧ごとに対応付けられたOCV係数ファイルを用いて、電圧降下領域ファイルの所定の電圧範囲に対応する第2OCV係数を領域ごとに算出し、算出した第2OCV係数と領域とを対応付けてOCV領域ファイルを作成し、遅延ライブラリを用いてレイアウトされた回路に対して遅延計算を行い、遅延計算結果とOCV領域ファイルの領域ごとの第2OCV係数を用いてタイミング解析を行う。

(もっと読む)

半導体設計支援装置、タイミング制約生成方法、およびプログラム

【課題】半導体集正規回路の設計時に論理合成以後にあたる下流工程に用いる設計ツールに、設計者に依存することなく適切なタイミング制約を与える。

【解決手段】半導体設計支援装置に、非同期回路を内在する電気回路の設計時に ソースコードに対して行われたCDC検証結果と 当該ソースコードのコーディングに用いられた仕様策定工程で定められた既知情報とから、ソースコードに含まれる全てのクロックについて明確化処理してCDC検証用設定ファイルとして収集取得する手段と、CDC検証用設定ファイルとCDC検証結果から得られた非同期パス毎の入出力パスと から、下流工程で用いられる設計ツールで読み込み可能な形式に合わせるように所定の情報を抽出処理してタイミング制約ファイルを生成出力する手段を設ける。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】半導体集積回路の遅延時間の変動を抑制すること。

【解決手段】回路設計支援装置1は、選択部1bと配置部1cとを有している。選択部1bは、設計対象の半導体集積回路モデルが備えるレジスタモデル2bにクロック信号を供給するクロック信号線の分岐点P1からレジスタモデル2bのクロック信号入力端子に至る第1の経路と、分岐点P1からレジスタモデル2bのデータ信号入力端子に至る第2の経路の、配線に関する物理パラメータの差分値に基づいて、物理パラメータが異なる配線負荷を有する複数の遅延回路モデルから遅延回路モデルBを選択する。配置部1cは、選択された遅延回路モデルBをデータ信号入力端子に接続されるデータ信号線に配置する。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】配線の遅延特性のばらつきを抑制すること。

【解決手段】回路設計支援装置1は、設定部1aと生成部1bとを有している。設定部1aは、半導体集積回路モデル2の層2a、2bそれぞれに、積層方向および面方向に隣接するユニット3の配線方向が互いに異なる方向に配線が生成される複数の矩形のユニット3を設定する。生成部1bは、ユニット3の境界で異なる層のユニット3に跨る配線を生成する。

(もっと読む)

設計支援装置、設計支援プログラムおよび回路設計方法

【課題】クロックゲーティング回路を使用した、より効率的な低消費電力化を実現するための設計方法を提供する。

【解決手段】デジタル回路内のフリップフロップの出力がフリップフロップの入力側の組合せ回路に回帰している論理において、フリップフロップの出力がマルチプレクサに回帰ルートとして、またマルチプレクサに前段組合せ論理の出力が更新ルートとして接続されている論理に変換をするクロックゲーティング回路設計方法により解決できる。

(もっと読む)

回路レイアウト設計システム、リーク対策セル、回路レイアウト設計方法及びプログラム

【課題】正規回路のタイミングを変えずに、未使用セル群の全てのセルのダイナミック電流及びチャンネルリーク電流を削減することができる回路レイアウト設計システムを提供する。

【解決手段】本発明の回路レイアウト設計システムは、レイアウトデータから、出力端子がオープン状態の未使用インバーターセルを検出する出力オープンセル検出部と、オープンセル検出部が検出した未使用インバーターセルの出力オープンセル情報を、出力オープンセル情報ファイルに格納する出力オープンセル情報抽出部と、レイアウトデータから、未使用インバーターセルを削除する出力オープンセル削除部と、出力オープンセル情報のセル名を、リーク対策セルに対応するセル名に変換した置換情報ファイルに格納するセル名変換部と、置換情報ファイルを参照して、レイアウトデータの未使用インバーターセルをリーク対策セルに置換する出力オープンセル置換部とを備える。

(もっと読む)

ダミーメタル配置評価装置、ダミーメタル配置評価方法及びダミーメタル配置評価プログラム

【課題】配線オブジェクトの敷設方向に対してずれを持たせたダミーメタルの配置を評価すること。

【解決手段】ダミーメッシュ情報作成部21は、配線オブジェクトの方向に対してずれを設けて規則的に配置したダミーメタルのブロック群を、各メッシュ内のダミーメタルの配置が同一となるようにメッシュ形状に分割する。重複判定部23は、分割によって得られた複数のダミーメッシュについて、配線オブジェクトとメッシュ内のダミーメタルのブロックとの重複を判定する。判定の結果、配線オブジェクトと重複するダミーメタルのブロックを除去したダミー情報をダミー情報算出部25が算出し、情報統合部26が配線オブジェクトの情報と統合する。評価部27は、統合したダミー挿入後の回路レイアウトが設計基準を満たすかを評価する。

(もっと読む)

設計支援装置、制御方法および制御プログラム

【課題】配線の効率化を図ること。

【解決手段】設計支援装置1は、表示部2に接続されており、記憶部1aと、選択部1bと、配置部1cと、判断部1dと、配線部1eと、確定部1fとを有している。記憶部1aは、回路の論理接続情報と配置対象のセルのセル情報を記憶する。選択部1bは、記憶部1aに記憶されたセル情報のうち、配置対象のセルのセル情報を選択する。配置部1cは、入力された座標に基づき、選択されたセル情報のセルの仮の配置を行う。判断部1dは、配線モードであるか否かを判断する。配線部1eは、判断部1dが配線モードであると判断した場合、仮の配置がされたセルに接続する配線について仮の配線を行う。確定部1fは、セルの配置位置の確定に基づいて、配線されたセルの仮の配線の配置位置を確定する。

(もっと読む)

半導体装置の設計方法、設計支援装置

【課題】ランプアニール工程での基板の温度ばらつきを抑制する。

【解決手段】半導体チップ(22)に導入、配置される複数の回路ブロック(A1〜E6)の初期レイアウト(31)を決定する。複数の回路ブロック(A1〜E6)の各々に対し、製造時にアニール用光源から照射される光の影響を受ける受光面を特定する。複数の回路ブロック(A1〜E6)の各々の面積に対する受光面の面積の比率を、受光面積率として算出する。初期レイアウトを、面積が均等な複数の領域の集合(A1〜E6、A2’、B2’、C5’、C6’、D5’、D6’、E3’、E4’)として特定する。基準ブロックの周辺の領域を周辺ブロックとして特定し、基準ブロックの受光面積率と周辺ブロックの受光面積率との和を周辺和とする。複数の領域の各々の周辺和のばらつきが最小となるように、複数の回路ブロックのレイアウトを変更する。

(もっと読む)

基板ノイズ解析装置

【課題】 本発明の課題は、被ノイズ回路において影響を受けるノイズの大きさに基づいて効率的に基板ノイズ解析を行うことを目的とする。

【解決手段】 上記課題は、導体集積回路の回路ブロック毎に該回路ブロックの回路データを用いてノイズ源解析を行い、各周波数と該周波数に対するノイズ量とを対応させたノイズ源情報を出力するノイズ源解析手段と、回路ブロック毎に該回路ブロックの回路データを用いて各周波数に対して出力ノードから出力される該周波数の振幅をノイズの影響の大きさを示す感度として解析するノイズ感度解析を行い、各周波数と該周波数に対する感度とを対応させたノイズ感度情報を出力するノイズ感度解析手段と、前記ノイズ源情報と前記ノイズ感度情報とに基づいてノイズを受ける被ノイズ回路の動作に影響を与える周波数成分を特定し、該ノイズ源情報から該周波数成分を抽出するノイズ源情報抽出手段とを有する基板ノイズ解析装置により達成される。

(もっと読む)

回路モデル生成装置

【課題】 本発明の課題は、素子データを含むアナログ回路モデルを生成することを目的とする。

【解決手段】 上記課題は、回路図データとレイアウトデータとを格納する記憶領域と、前記レイアウトデータから寄生素子に係る素子データを抽出する抽出手段と、前記回路図データに前記素子データを含む回路モデルをハードウェア記述言語によって生成する回路モデル生成手段とを有する回路モデル生成装置により達成される。

(もっと読む)

回路設計装置、回路設計プログラム及び回路設計方法

【課題】効率的且つ十分に低消費電力化を行なうことを課題とする。

【解決手段】回路設計装置は、回路に含まれるFFのうち、動作していないFFを抽出し、抽出されたFFに対する制御信号の出力元である無動作起因端子を探索する。また、回路設計装置は、無動作起因端子が同一となるFFを1つのドメインとしてドメイン化し、ドメイン化されたFFそれぞれについてバックトレースを実施する。また、回路設計装置は、バックトレースにおいてFFに到達するまでに存在する組み合わせ回路を抽出する。また、回路設計装置は、到達したFFのうち同一ドメインでないFFそれぞれについてフォワードトレースを実施し、到達したFFが同一ドメインである場合に該当する組み合わせ回路も同一ドメインとしてドメイン化する。

(もっと読む)

21 - 40 / 345

[ Back to top ]