Fターム[5F083AD21]の内容

Fターム[5F083AD21]の下位に属するFターム

横フィン型 (30)

王冠型(縦フィン型) (807)

コンタクトホール部を利用したもの(コンタクト部に切込) (109)

ストレージ電極の厚膜化(側面積の増加) (125)

複数の層間絶縁膜のエッチングレート差の利用 (6)

複数の導電膜のエッチングレート差の利用 (2)

ビット線層の上部にキャパシタを形成(COB) (490)

平坦化層間絶縁膜上にキャパシタ形成 (552)

Fターム[5F083AD21]に分類される特許

201 - 220 / 501

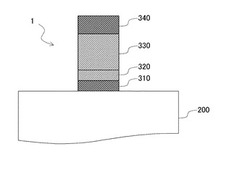

半導体デバイスの製造方法および半導体デバイス

【課題】下地膜の結晶性の影響を抑え、高誘電率の結晶構造としたキャパシタ絶縁膜とする。

【解決手段】基板200の上に形成された結晶質膜310の上に非晶質膜320を形成する非晶質膜形成工程と、非晶質膜320の上に結晶質膜310の結晶構造とは独立して制御される結晶構造を持つ絶縁膜330を形成する結晶性絶縁膜形成工程と、を有する。結晶性絶縁膜形成工程においては、基板200を加熱して前記絶縁膜330の少なくとも一部を正方晶系へ相転移させる相転移工程と、を有する。

(もっと読む)

キャパシタ、該キャパシタを備える半導体装置および半導体装置の製造方法

【課題】アスペクト比の高い電極を上下に接続して、静電容量の大きいキャパシタを形成する際、電極間の剥離を防止し、電極の倒壊を抑制する。

【解決手段】導電膜を外壁に有する下部電極30と、該下部電極の導電膜に対して、容量絶縁膜を介して形成された上部電極とを有するキャパシタにおいて、下部電極は少なくとも2層の積層構造であって、該積層構造は、下層側電極18に設けた掘り込み部に上層側電極22の底部が埋め込まれた構造であるキャパシタ。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体又は高誘電体を用いた容量絶縁膜を有する半導体装置において、容量絶縁膜の結晶化時に酸素バリアが還元されることを確実に防止する。

【解決手段】半導体装置は、複数の酸素バリア膜16と、複数の酸素バリア膜16の各々の上に、下部電極17、容量絶縁膜19及び上部電極20からなるキャパシタ21と、複数のキャパシタ21を覆うように形成された層間絶縁膜22とを備えている。層間絶縁膜22における隣り合うキャパシタ21間に位置する部分の上面が、層間絶縁膜22におけるキャパシタ21の直上に位置する部分の上面よりも低い。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】TiO2膜やSrTiO膜の結晶性を制御し、誘電率を増大させる。

【解決手段】基板上に立方晶もしくは斜方晶の結晶性を持つ第1の高誘電率絶縁膜を形成する工程と、第1の高誘電率絶縁膜上に第2の高誘電率絶縁膜を形成し、第1の高誘電率絶縁膜の結晶性を第2の高誘電率絶縁膜に反映させて、第2の高誘電率絶縁膜の結晶性をルチル構造とする工程と、を有する。

(もっと読む)

誘電体薄膜の形成方法及び該方法により形成された誘電体薄膜

【課題】薄膜キャパシタ等に用いた場合に、高いチューナビリティ及び高い誘電率を発現させ得る誘電体薄膜を形成する方法及び該誘電体薄膜を提供する。

【解決手段】誘電体薄膜形成用組成物を耐熱性基板に塗布し乾燥する工程を繰返し行って所望の厚さの組成物の未焼成膜を得た後、基板上に形成した未焼成膜を焼成することにより誘電体薄膜を形成する方法において、形成する誘電体薄膜がペロブスカイト型酸化物を主成分とする薄膜であるとき、基板上に形成した未焼成膜の焼成が、60〜6000℃/分の急速昇温加熱による第一次焼成と、0.5〜30℃/分の低速昇温加熱による第二次焼成とをこの順番に少なくとも含むことを特徴とする。

(もっと読む)

不揮発性メモリ

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】 製造工程における強誘電体キャパシタの劣化を抑制することが可能な半導体装置およびその製造方法を提供する。

【解決手段】 加工後のキャパシタ側面に、例えば、第二の保護膜としての第二のCeZrO膜125を形成し、熱処理を加えることでCeZrO膜中の酸素原子が、キャパシタの誘電体膜であるPZT膜120および酸化物により形成されるキャパシタの電極の酸素欠損を補充するように拡散することとなる。但し、加工後のキャパシタ側面にCeZrO膜125を形成した後に、熱処理の工程をあえて追加して行わない場合であっても、CeZrO膜125の形成後に層間絶縁膜を形成するCVD工程において加熱が行われ、PZT膜120およびキャパシタの電極に酸素供給が行われることとなる。

(もっと読む)

シリコン層の形成方法、半導体装置の製造方法

【課題】シリコン層表面の溶解を防止しつつ、エピタキシャル成長により形成された凝集性異物を除去する。清浄な表面を有し、膜厚が均一なシリコン層を形成する。

【解決手段】シリコン基板上にエピタキシャル成長によりシリコン層を形成した後に、シリコン層の表面を酸化する。このシリコン層の表面を洗浄して、エピタキシャル成長時にシリコン層の表面に発生した異物を除去する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成される。

(もっと読む)

窒化膜の形成方法、酸窒化膜の形成方法、窒化膜のスパッタリング方法、ゲート絶縁膜の形成方法

【課題】実質的なリーク電流を生じることなく膜厚を減少させることができる高品質で均一な酸化膜、窒化膜あるいは酸窒化膜の形成方法を提供する。

【解決手段】基板上に絶縁膜を形成する工程と、前記絶縁膜をKrあるいはArを不活性ガスとしたプラズマに伴い生成された原子状酸素O*あるいは原子状窒化水素NH*に曝し、膜質を改変する工程とよりなる絶縁膜の形成方法を提供する。

(もっと読む)

半導体装置

【課題】効率的にかつ確実にブロー状態に設定しかつ通常動作モード時に、確実に、プログラム情報を保持する所望の耐圧特性を有するキャパシタ型アンチヒューズを実現する。

【解決手段】プログラムモード時と通常動作モード時とで、キャパシタ型アンチヒューズに対する電圧印加極性を変更する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜を用いたキャパシタの更なる特性の向上を実現し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された下部電極48と;下部電極上に直接形成され、Laが添加されたチタン酸ジルコン酸鉛の第1の強誘電体膜50と、第1の強誘電体膜上に直接形成され、第1の強誘電体膜より膜厚が薄く、LaとCaとSrとが添加されたチタン酸ジルコン酸鉛の第2の強誘電体膜52とを有するキャパシタ誘電体膜54と;キャパシタ誘電体膜上に形成された上部電極60とを有するキャパシタを有している。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ内に形成されたビット線の底面からのリーク電流を低減する。また、トレンチのアスペクト比を大きく増加させることなく、その後の工程でトレンチ内の空間に安定して成膜して、高アスペクト比による加工性の低下といった問題が生じない半導体装置を提供する。

【解決手段】半導体基板内にトレンチを形成する。このトレンチ内壁の底面上に第一の絶縁膜を形成する。また、トレンチ内壁の側面上に熱酸化により第一の絶縁膜よりも膜厚が薄い第二の絶縁膜を形成する。トレンチ内の第一の絶縁膜上に、ビット線を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】ビット線の上面にハードマスク膜を形成し、ビット線の側壁に窒化膜をエッチバックして形成したサイドウォールを設けるSAC(セルフアラインコンタクト)プロセスを用いることなくビット線と容量コンタクトとの間の短絡を防止する。

【解 決手段】SAC構造を採用していない半導体装置に対して、ビット線6が形成されている場所以外のビットコンタクト層間膜13をエッチング処理により除去した後に、 ダイレクト窒化膜19をビット線6の上面および側面の全面にビット線6を覆うようにして形成する。ビット線6上の上面の窒化膜の膜厚を側面とほぼ同一にで きるため、ビット線6自体の高さが低くなり、微細化を図ることができる。また、エッチバックを必要とせずに、ビット線6の側壁に窒化膜を形成するため、 SAC構造に比べて、ビット線6の側壁に一定の膜厚を有する窒化膜を容易に形成できる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】所望の等価酸化膜厚(EOT)及びリーク電流特性を有するキャパシタを備えた半導体記憶装置を提供する。

【解決手段】第1の電極と容量絶縁膜と第2の電極からなるキャパシタを備えた半導体記憶装置において、この容量絶縁膜は、金属酸化物結晶化膜からなる第1の誘電体膜と、第1の誘電体膜上の窒素含有アモルファス金属酸化物からなる第2の誘電体膜と、第2の誘電体膜上の金属酸化物結晶化膜からなる第3の誘電体膜を含む。

(もっと読む)

半導体装置の製造方法

【課題】アスペクト比の高い下部電極は、エッチングにより倒壊が生じやすいという問題があった。

【解決手段】複数の筒状の第一の下部電極9上に、前記第一の下部電極9の上端に接合するとともに前記第一の下部電極9同士を連結する第一梁10aを形成する工程の後に、前記第一の下部電極9同士の間の空間を残しつつ、前記第一梁10を覆うように第二の層間絶縁膜11を形成した後に、前記第二の層間絶縁膜11を貫通する複数の筒状の第二の下部電極12を形成する工程と、前記第二の層間絶縁膜11上に、前記第二の下部電極12の上端に接合するとともに複数の前記第二の下部電極12を連結する第二梁13aを形成する工程と前記第二の層間絶縁膜11する工程と、を少なくとも一以上繰り返すことを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体基板の表面に形成された拡散層領域における半導体基板の膨張の発生を抑制することが可能な、半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板111と、半導体基板111の表面に形成され、半導体基板111の表面に平行な所定方向に沿って交互に設けられ、素子分離層121の上面の高さが活性層122の上面の高さよりも低くなっている素子分離層121及び活性層122と、活性層122の表面に形成された拡散層131と、拡散層131の上面及び側面に形成され、半導体基板111を形成する半導体よりも格子定数の小さい材料で形成されたストレスライナー132とを備える。

(もっと読む)

半導体装置の製造方法

【課題】

高い誘電率のチタン酸化膜を低温で形成する。

【解決手段】

ウエハ14上に下電極155を形成するステップ(S100)と、下電極155界面にAlOx膜160を形成するステップ(S200)と、AlOx膜160上にHfAlOx膜165を形成するステップ(S300)と、HfAlOx膜165が形成されたウエハ14をアニーリング(熱処理)するステップ(S400)と、アニーリングされたHfAlOx膜165上にTiO2膜170を形成するステップ(S500)と、TiO2膜170が形成されたウエハ14をアニーリングするステップ(S600)と、を行いキャパシタ絶縁膜を形成し、このキャパシタ絶縁膜の上に上電極175を形成する(S700)。

(もっと読む)

半導体装置およびその製造方法

【課題】拡散層と拡散層に接続されるコンタクトとの接触抵抗を低減した半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置の製造方法は半導体基板にピラー部を設ける工程と、前記ピラー部の基端部近傍に第1の不純物拡散領域を形成する工程と、ピラー部の側面を被覆する第1の絶縁膜を形成するとともに、第1の絶縁膜を介してピラー部の側面に対向する電極層を形成する工程と、ピラー部及び第1の絶縁膜の周囲を埋める第2の絶縁膜を形成する工程と、第1の層間膜を除去して前記ピラー部の先端面を露出させる工程と、ピラー部の先端部に第2の不純物拡散領域を形成する工程と、第1の絶縁膜をエッチングして前記ピラー部の先端部の側面を露出させる工程と、ピラー部の先端面及びピラー部の先端部の側面を覆うようにコンタクトプラグを形成する工程と、を具備してなる。

(もっと読む)

201 - 220 / 501

[ Back to top ]