Fターム[5F083AD21]の内容

Fターム[5F083AD21]の下位に属するFターム

横フィン型 (30)

王冠型(縦フィン型) (807)

コンタクトホール部を利用したもの(コンタクト部に切込) (109)

ストレージ電極の厚膜化(側面積の増加) (125)

複数の層間絶縁膜のエッチングレート差の利用 (6)

複数の導電膜のエッチングレート差の利用 (2)

ビット線層の上部にキャパシタを形成(COB) (490)

平坦化層間絶縁膜上にキャパシタ形成 (552)

Fターム[5F083AD21]に分類される特許

161 - 180 / 501

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

Zr−Ge−Ti−OまたはHf−Ge−Ti−Oの誘電材料を備えた物質とその製造方法

【課題】 フィルム、またはRがZrとHfから選択されたR−Ge−Ti−Oを備えた誘電材料とその製造方法を提供する。

【解決手段】 本発明は、RがZrとHfから選択される、R−Ge−Ti−Oのフィルムを備えた誘電材料に関し、また、その製造方法に関連する。誘電材料は、公式Rx−Gey−Tiz−Owを有することが好ましく、ここで、.05≧x≦1、.05≦y≦1、0.1≧z≦1、1≧w≦2、x+y+z≡1であり、さらに好ましくは、0.15≧x≦0.7、.05≧y≦0.3、0.25≧z≦0.7、1.95≧w≦2.05であり、x+y+z≡1である。本発明は、ダイナミック・ランダム・アクセス・メモリ(DRAM)装置のコンデンサを備えたシリコンチップ集積回路装置での使用に特に有用である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】メモリセルアレイを構成する複数のメモリセルが、複数行ごとに複数のブロックに分割され、共通ビット線は、各ブロックにおいて、選択トランジスタを介して分割ビット線と電気的に接続されており、メモリセルの一は、第1のチャネル形成領域を含む第1のトランジスタと、第2のチャネル形成領域を含む第2のトランジスタと、容量素子と、を有し、ソース線は、第1のソース電極と接続され、分割ビット線は、第1のドレイン電極および第2のソース電極と接続され、ワード線は、容量素子の電極の一方と接続され、信号線は、第2のゲート電極と接続され、第1のゲート電極と、第2のドレイン電極と、容量素子の電極の他方とが接続される半導体装置を提供する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、メモリセルアレイを有する半導体装置において、直列に接続された第1乃至第mのメモリセルに含まれる各ノードに生じる寄生容量の値を同等の値とすることで、安定して動作可能な半導体装置とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタ160と、第2のトランジスタ162と、第1のトランジスタ160のソース領域またはドレイン領域120と、第2のトランジスタ162のチャネル形成領域144との間に設けられた絶縁層128と、を含むメモリセルを有し、第1のトランジスタ160と、第2のトランジスタ162とは、少なくとも一部が重畳して設けられる半導体装置である。また、絶縁層128と第2のトランジスタのゲート絶縁層146は、式((ta/tb)×(εrb/εra)<0.1)を満たす。(但し、式中、taはゲート絶縁層146の膜厚を示し、tbは絶縁層128の膜厚を示し、εraはゲート絶縁層146の誘電率を示し、εrbは絶縁層128の誘電率を示す。)

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタにおける強誘電体層の結晶配向度を向上する半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、下部電極層41上にバッファ層44を形成する工程と、バッファ層44に対して、100体積%の濃度よりも低い酸素濃度の雰囲気下で且つ第1の温度で第1の熱処理を行った後、第1の温度よりも高い第2の温度で第2の熱処理を行う工程と、バッファ層44上に誘電体層42を形成する工程と、誘電体層42上に上部電極層43を形成する工程と、誘電体層42を熱処理して結晶化する工程と、を備える。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

半導体装置の駆動方法

【課題】酸化物半導体層によってチャネル領域が形成されるトランジスタのソース及びドレインの一方に電気的に接続されたノードにおいて電荷の保持を行う半導体装置に記憶された情報の経時変化を抑制すること。

【解決手段】書き込み期間と保持期間の間に、トランジスタのゲートに強い負電位を与える期間(反転期間)を設ける。反転期間において、当該トランジスタのドレインから酸化物半導体層に対する正電荷の供給が促進される。これにより、酸化物半導体層内又は酸化物半導体層及びゲート絶縁膜の界面への正電荷の蓄積を短期間で収束させることができる。そのため、反転期間後の保持期間における当該トランジスタのドレインに電気的に接続されたノードにおける正電荷の減少を抑制することが可能である。すなわち、当該半導体装置に記憶された情報の経時変化を抑制することが可能である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の平面形状を大きくせずに、その容量を大きくすることができ、かつ容量素子のリーク電流が増大することを抑制する。

【解決手段】下部電極410は、表層に、厚さが2nm以下の金属含有酸化層414を有している。金属含有酸化層414は、下部電極410の表面を酸化することにより形成されている。そして誘電膜420は、バルク状態において常温で出現する第1相と、バルク状態において第1相より高温で出現する第2相と、を含んでいる。第2相は第1相より比誘電率が高い。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】データの保持時間を長くすることができるキャパシタレスDRAMの半導体装置及びその製造方法を提供する。

【解決手段】基板層42、埋め込み絶縁層43、及び半導体層41が順次積層された基板11と、半導体層41の主面41aに形成され、Y方向に延在し、半導体層41よりなるピラー状電荷保持部26と、ピラー状電荷保持部26と埋め込み絶縁層43との間に位置する半導体層41よりなり、ピラー状電荷保持部26と一体に形成され、X方向の幅がピラー状電荷保持部26の幅よりも広い第1の板状チャネル部25と、X方向から第1の板状チャネル部25を挟む第1及び第2の不純物拡散領域32,33と、少なくともピラー状電荷保持部26及び第1の板状チャネル部25の上面に設けられた電極用絶縁膜34と、電極用絶縁膜34を覆うように設けられ、ピラー状電荷保持部26に電圧を加える電荷保持用電極35と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体装置の製造方法

【課題】溝内の一部のみを覆うマスクパターンを、フォトレジスト膜を用いて形成する必要のない半導体装置の製造方法を提供する。

【解決手段】半導体基板1に、第1溝7を形成する工程と、第1溝7に第1絶縁膜8を形成する工程と、上面が第1絶縁膜の上端よりも下方になるように第1溝7内に第1導電膜9を充填する工程と、第1溝7の側面にカーボン膜10を形成する工程と、第1溝7内を第2絶縁膜11で充填する工程と、第1溝7内の側面の一方を覆うカーボン膜10を除去し、第1絶縁膜8の一部を露出させる工程と、第2絶縁膜11と露出された第1絶縁膜8を除去し、半導体基板1の一部を露出する工程と、を有することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】チャネル領域を従来よりも拡大することが可能な半導体装置を提供する。

【解決手段】埋め込みゲート用の溝部9,10のうち、活性領域6に形成される第1の溝部9よりも素子分離領域5に形成される第2の溝部10の深さを深くすることによって、第2の溝部10の底面の間から活性領域6の一部が突き出した第1のフィン部12aと、埋め込みゲート用の溝部9,10の少なくとも上面開口部よりも下部側において、第1の溝部9よりも第2の溝部10の第1の方向における幅を大きくすることによって、第2の溝部10の両側面の間から第1のフィン部12aに連続して活性領域6の一部が突き出した一対の第2のフィン部と12bとを形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

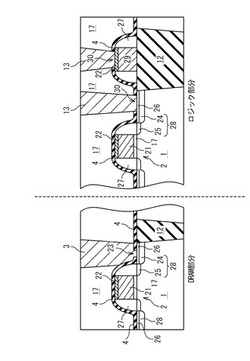

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

161 - 180 / 501

[ Back to top ]