Fターム[5F083AD21]の内容

Fターム[5F083AD21]の下位に属するFターム

横フィン型 (30)

王冠型(縦フィン型) (807)

コンタクトホール部を利用したもの(コンタクト部に切込) (109)

ストレージ電極の厚膜化(側面積の増加) (125)

複数の層間絶縁膜のエッチングレート差の利用 (6)

複数の導電膜のエッチングレート差の利用 (2)

ビット線層の上部にキャパシタを形成(COB) (490)

平坦化層間絶縁膜上にキャパシタ形成 (552)

Fターム[5F083AD21]に分類される特許

81 - 100 / 501

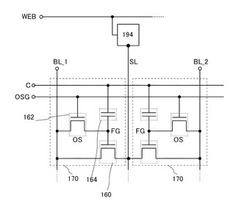

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料を用いたトランジスタと、第1の半導体材料とは異なる第2の半導体材料を用いたトランジスタと、容量素子とを有する複数のメモリセルを有し、書き込み期間にソース線に電源電位を供給する機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に抑えることができる。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールに埋め込まれたコンタクトプラグが埋め込み配線と非導通になることを防止した半導体装置及びその製造方法を提供する。

【解決手段】ゲート絶縁膜を介してピラー部9の側面と対向する位置において幅広となる形状を有する第1の溝部8を形成し、この第1の溝部8の幅広となる部分8bに埋め込まれた状態で第1の埋め込み配線15を形成し、複数のピラー部9が並ぶ領域よりも外側の領域において、第1の溝部8の間に位置すると共に、第1の溝部8の幅広となる部分8bに埋め込まれた第1の埋め込み配線15に至る深さで第1のコンタクトホール25を形成する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置およびその駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のチャネル形成領域と、第1のゲート電極と、第1のソース領域およびドレイン領域と、を有する第1のトランジスタと、少なくとも第1のソース領域またはドレイン領域の一部と重畳するように設けられた、酸化物半導体材料からなる第2のチャネル形成領域と、第2のソース電極と、第1のゲート電極に電気的に接続される第2のドレイン電極と、第2のゲート電極と、を有する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間の絶縁層と、を含むメモリセルを有し、第2のトランジスタをオフ状態とすべき期間において、少なくとも第1のソース領域またはドレイン領域に正の電位が与えられるときに第2のゲート電極に負の電位が与えられる半導体装置。

(もっと読む)

半導体デバイスの製造方法

【課題】チャネル領域となる領域の直下だけに熱拡散によってビット線となる拡散層を形成することができる半導体デバイスの製造方法を提供する。

【解決手段】半導体基板の法線方向に複数の半導体ピラーを形成する工程、前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程、前記溝の内部全体を覆うように第1のポリシリコン膜を形成する工程、前記第1のポリシリコン膜上に前記半導体基板内へ拡散させる不純物で構成された不純物層を形成する工程、前記不純物層上に第2のポリシリコン膜を形成する工程、前記第2のポリシリコン膜上に前記不純物の外方拡散を防止する第1の拡散防止膜を形成する工程を経た後、前記不純物を前記溝の底部において前記半導体ピラー内に熱拡散させてビット線となる拡散層を形成する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

酸化物材料および半導体装置

【課題】トランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。また、このような半導体装置を実現する酸化物材料を提供する。

【解決手段】それぞれ、c軸配向し、ab面、上面または被形成面に垂直な方向から見て少なくとも三角形状または六角形状の原子配列を有し、c軸においては、金属原子が層状または金属原子と酸素原子とが層状に配列しており、In2SnZn2O7(ZnO)m(mは0または自然数。)で表される、ab面(または上面または被形成面)においては、a軸またはb軸の向きが異なる二種以上の結晶部分を含む酸化物膜を用いる。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供すること。また、安定した電気的特性が付与された、信頼性の高い半導体装置を提供すること。

【解決手段】絶縁層に凸状構造体を形成し、該凸状構造体に接して酸化物半導体層のチャネル形成領域を設けることで、チャネル形成領域を3次元方向(基板垂直方向)に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、凸状構造体の上面と側面とが交わる上端コーナー部に曲面を形成し、酸化物半導体層が当該曲面に垂直なc軸を有する結晶を含むように形成する。これによって、酸化物半導体層の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

半導体記憶装置

【課題】電力の供給がない状況でも記憶内容の保持が可能かつ、書き込み回数にも制限がない新たな構造の半導体記憶装置を提供する。

【解決手段】第1のトランジスタのソースまたはドレインの一方が第2のトランジスタのソースまたはドレインの一方と接続し、第1のトランジスタのゲートが第3のトランジスタのソースまたはドレインの一方、およびキャパシタを構成する一対の容量電極の一方と接続し、第1のトランジスタのソースまたはドレインの他方および第3のトランジスタのソースまたはドレインの他方がビット線と接続し、第3のトランジスタのゲートがワード線と接続し、第2のトランジスタのゲートおよびソースまたはドレインの他方がソース線と接続し、キャパシタを構成する一対の容量電極の他方が共通配線と接続し、共通配線はGNDに接続し、共通配線は上面から見て網状に設けられ、第3のトランジスタはその網の目に設けられる半導体記憶装置。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】トランジスタの作製工程において、酸化物半導体層、ソース電極層、ドレイン電極層、ゲート絶縁膜、ゲート電極層、酸化アルミニウム膜を順に作成した後、酸化物半導体層および酸化アルミニウム膜に対して熱処理を行うことで、水素原子を含む不純物が除去され、かつ、化学量論比を超える酸素を含む領域を有する酸化物半導体層を形成する。また、酸化アルミニウム膜を形成することにより、該トランジスタを有する半導体装置や電子機器の作製工程での熱処理でも大気から水や水素が酸化物半導体層に侵入し、拡散することを防止することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

81 - 100 / 501

[ Back to top ]