Fターム[5F083BS13]の内容

Fターム[5F083BS13]の下位に属するFターム

Fターム[5F083BS13]に分類される特許

21 - 40 / 128

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

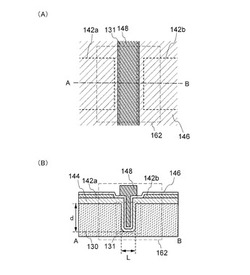

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体記憶装置

【課題】低消費電力化できる半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、ワード線WLと相補関係にあるビット線対(BLc,BLt)との交差位置に配置され、第1ノード(1N)に与えられる第1電源電圧Vddと仮想ノードVNに与えられる電圧との間におけるデータを記憶するメモリセルMCと、入力および出力が前記仮想ノードと第2電源電圧Vssとの間に配置され、制御端子が前記ビット線対に接続され、前記ビット線対の振幅をモニタし、前記ビット線対に十分な振幅が発生した場合に、前記第2電源電圧Vssへの電流経路を制限するリミッター回路11とを具備する。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

記憶装置、集積回路装置、及び電子機器

【課題】マルチポートメモリーとして機能する場合に、クロストークノイズを大幅に低減して、誤動作を防止して回路動作の安定化を図る記憶装置等を提供する。

【解決手段】メモリーセルアレイ10を有する半導体記憶装置100は、第1の方向に並ぶメモリーセルを選択するための第1のワードラインと、第2の方向に並ぶメモリーセルを選択するための第2のワードラインと、第1のワードラインによって選択されたメモリーセルに接続される一対の第1のビットライン及び第1の相補ビットラインと、前記第2のワードラインによって選択されたメモリーセルに接続される第2のビットラインとを含み、第2のワードラインは、対応する一対の第1のビットライン及び第1の相補ビットラインに対し、上面から見て第1の方向又は該第1の方向の反対方向に隣接して、第2の方向に延びるように配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の形状を精度良く形成すると共に、隣り合うゲート電極同士がショートすることを防止する。

【解決手段】開口部を有するマスク16Mを用いて、導電膜15にイオンを注入し、ミキシング膜20Xを形成する。次に、マスクを除去した後、導電膜及びミキシング膜の上に、平面形状がライン形状のレジストパターン21を形成する。次に、レジストパターンをマスクとして、導電膜及びミキシング膜をエッチングし、導電膜15aを有するゲート電極を形成すると共に、ゲート電極のゲート幅方向の側面の上に、ミキシング膜20xを残存させる。次に、熱処理により、ミキシング膜に含まれるイオンと、元素(元素は、導電膜に由来する)とを反応させて、絶縁膜24xを形成する。絶縁膜は、ゲート電極と一体に形成されている。絶縁膜により、ゲート電極と、該ゲート電極とゲート幅方向に沿って隣り合う他のゲート電極との間が電気的に分離されている。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

半導体記憶装置

【課題】SRAMのゲート配線形成にあたって、ゲート形状を複雑に変形させることなく転写及び加工マージンを確保する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1組及び第2組のドライバトランジスタ11、ロードトランジスタ12及びアクセストランジスタ13とを備えたメモリセルが半導体基板上に2次元配列されたメモリセルアレーと、複数のワードラインと、複数のビットラインと、第1組のドライバトランジスタ11とロードトランジスタ12とを接続し、直線状の側辺を有する長方形状の第1ゲート配線3aと、アクセストランジスタ13と接続され、直線状の側辺を有する長方形状の第2ゲート配線3cと、第1ゲート配線3aと、第2組のドライバトランジスタ11とロードトランジスタ12とを接続する第1コネクタ5aと、第2ゲート配線3cとワードラインとを接続する第2コネクタ5cとを備える。

(もっと読む)

半導体集積回路

【課題】トランジスタの性能の劣化の防止に有利な半導体集積回路を提供する。

【解決手段】実施形態によれば、半導体集積回路は、ワード線とビット線との交差位置にそれぞれ配置されデータを保持するデータ記憶部(SRAMセル)と前記データ記憶部に記憶された保持データを論理的に反転させる反転回路22と、前記データ記憶部が記憶するデータの論理反転の有無を識別するフラグをロウ単位で記憶するフラグビットカラム11−1とを備える、メモリセルアレイ11を具備する。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定かつ高速に動作する半導体記憶装置を実現する。

【解決手段】メモリセル列ごとにアレイ電源線(ARVD)およびダウン電源線(DWVD)を配置する。ダウン電源線は、読出し時に接地に結合され、書込み時にフローティング状態とされる。書込み時、選択列のアレイ電源線への電源電圧の供給を停止するとともに該アレイ電源線を対応のダウン電源線に接続する。電源系統を複雑化することなく、低電源電圧下においても安定にデータの書込/読出を行うことのできる半導体記憶装置を実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】マスクの新規な作製技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、第1の膜を形成する工程と、第1の膜上方に、第1マスク膜を形成する工程と、第1マスク膜をパターニングする工程と、パターニングされた第1マスク膜の側部にプラズマ処理を行って、側部を変質層に変換する工程と、プラズマ処理の後、第1マスク膜の上部及び側部を覆う第2マスク膜を形成する工程と、第2マスク膜をエッチングして、側部に形成された第2マスク膜を残存させつつ、第1マスク膜上部に形成された第2マスク膜を除去する工程と、第2マスク膜のエッチングの後、変質層を除去する工程と、変質層を除去した後、残った部分の第1マスク膜、及び第2マスク膜をマスクとして、第1の膜をエッチングする工程とを有する。

(もっと読む)

マスタスライス方式メモリセル

【課題】複数種類の回路構成をマスタスライス方式で対応可能なメモリセル専用のマスタスライス方式メモリセルを提供すること。

【解決手段】メモリユニットが2行2列に配置されてメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第3拡散層を備え、各拡散層で並列接続のトランジスタが構成される。第1および第2ワード線は第1〜第3拡散層の両端部外方に配置される。第1〜第3拡散層の第1コンタクト層とゲート層の第2コンタクト層との間、第1コンタクト層と第1/第2ワード線との間に、行方向に沿って第1のメタル配線領域が確保される。第1のメタル配線領域には、第2または第3メタル層の何れかが配線可能である。第1及び第2拡散層、第2及び第3拡散層の間には、列方向に沿って第2のメタル配線領域が確保される。第2のメタル配線領域には第3メタル層が配線可能である。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

対電極を有する4つのトランジスタを持つSRAMメモリセル

【課題】製造方法の複雑さが増加することを避けつつ、非常にコンパクトであるメモリセルを提供する。

【解決手段】4つのトランジスタを持つSRAMのメモリセルは、半導体材料から形成された第1の領域5aを有し、この第1の領域は、直列に接続された第1の伝送トランジスタ1aと第1のドライバトランジスタ2aとを有し、これらの共通端子は第1の電気ノードFとなっている。第2の伝送トランジスタ1bと第2のドライバトランジスタ2bとは、半導体材料で形成された第2の領域上で直列に接続されており、これらの共通端子は第2の電気ノードSとなっている。第1の伝送トランジスタ1aと第2のドライバトランジスタ2bとは、第1の電気ノードFと第2の電気ノードSとを通過する面FSの第1の側の上にあり、これに対し、第1のドライバトランジスタ2aと第2の伝送トランジスタ1bとは、面FSの他の側の上にある。

(もっと読む)

21 - 40 / 128

[ Back to top ]