Fターム[5F083BS27]の内容

Fターム[5F083BS27]の下位に属するFターム

拡散層ゲート (1)

Fターム[5F083BS27]に分類される特許

201 - 220 / 629

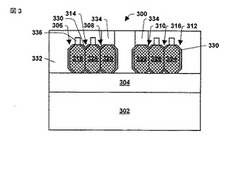

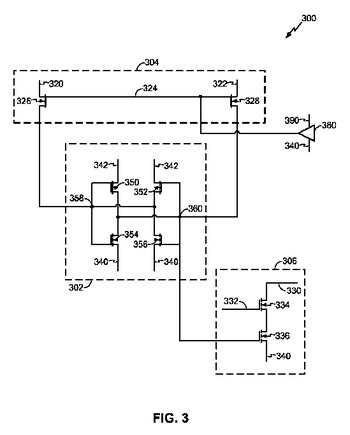

非プレーナ型トランジスタを用いた半導体装置および製造方法

【課題】より速い駆動電流およびより小さな短チャネル効果を備え、微細化されたスタティック・ランダム・アクセス・メモリ・セルを提供する。

【解決手段】スタティック・ランダム・アクセス・メモリ・セル300は、半導体基板上の1つ以上のフィンを備える2つの非プレーナ型パスゲート・トランジスタを備える。2つの非プレーナ型プルアップ・トランジスタは、半導体基板上の1つ以上のフィンを備える。2つの非プレーナ型プルダウン・トランジスタは、半導体基板上の1つ以上のフィンを備える。半導体基板上の2つのアシスト・バー314、316は、非プレーナ型プルアップ・トランジスタのフィンの一部と非プレーナ型プルダウン・トランジスタのフィンの一部とを電気的に接続する。

(もっと読む)

ソフトエラーアップセット不感性を有する揮発性記憶素子

高エネルギーの原子粒子衝突に曝される際に、ソフトエラーアップセット事象に対して不感性を呈する記憶素子が提供される。記憶素子はそれぞれ、2つのアドレストランジスタと、双安定要素を形成するように相互接続される4つのトランジスタの対とを含む、10個のトランジスタを有してもよい。トゥルーおよびコンプリメントクリアライン等のクリアラインは、あるトランジスタの対と関連している正の電源端子および接地電源端子にルーティングされてもよい。クリア操作の際、トランジスタの対の一部または全部は、選択的にクリアラインを使用して、電力供給を停止することが可能である。これは、論理0値が、アドレストランジスタを介して駆動されるクリア操作を促進し、クロスバー電流サージを低減させる。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

半導体集積回路

【課題】トランジスタの特性ばらつきによる遅延回路の遅延時間の変動を抑制することが可能で、更に、製造工程における加工ばらつきに強く、レイアウト拡張性に優れた半導体集積回路を小面積に提供する。

【解決手段】第1の電源VDDと第2の電源(接地電源)との間に直列に接続されたP型MOSトランジスタMP11と2以上のN型MOSトランジスタMN11、MN12とが備えられる。入力端子INは前記P型MOSトランジスタMP11のゲート端子と前記N型MOSトランジスタMN11、MN12のゲート端子とに接続される。更に、P型MOSトランジスタMP11とN型MOSトランジスタMN11の接点である出力端子OUTに接続した1以上の容量素子C1を有し、P型MOSトランジスタMP11の駆動能力を、2以上に直列接続したN型MOSトランジスタMN11、MN12の総駆動能力よりも大きく構成する。

(もっと読む)

メモリ装置の金属構造

【課題】メモリ装置の金属構造を提供する。

【解決手段】半導体装置が提供され、基板と、基板に形成されるスタティック・ランダム・アクセス・メモリ(SRAM)ユニットセルと、基板の上に形成され、SRAMユニットセルに局部内部接続を提供する第一金属層と、第一金属層の上に形成され、それぞれ、第一厚さを有するビットラインと相補ビットラインと、ビットラインと相補ビットライン間に配置されるVccラインと、を有する第二金属層と、第二金属層の上に形成され、第一厚さよりも厚い第二厚さを有するワードラインを有する第三金属層と、からなる。

(もっと読む)

半導体記憶装置

【課題】スタンバイ電流が小さく、ラッチアップに強い半導体記憶装置を提供する。

【解決手段】このSRAMは、各行に対応して設けられて対応の行のメモリセル電源配線MVLの一方端と電源電位VDD′のラインとの間に接続され、比較的高い導通抵抗値を有するPチャネルMOSトランジスタ1を備える。したがって、スタンバイ電流を低減化し、ラッチアップ現象の発生を抑制することができる。

(もっと読む)

半導体装置

【課題】メモリブロックを含んだ半導体装置において、高速化を実現する。

【解決手段】例えば、メモリブロックMB1内に複数のメモリアレイARY[0]〜ARY[3]が備わった構成において、ARY[0]〜ARY[3]のサイズA[0]〜A[3]が段階的に異なるように形成される。具体的には、MB1への内部制御信号(例えばクロック信号CLK)の入力パッドPD_CLKや、MB1からのデータ信号の出力パッドPD_DOからの距離が、ARY[0]<ARY[1]<ARY[2]<ARY[3]の場合、例えば、A[0]>A[1]>A[2]>A[3]となるように形成される。これによって、このパッドからの距離の違いに伴う伝送遅延時間の差分を各メモリアレイの動作遅延時間の差分で相殺することができ、MB1全体として高速化が図れる。

(もっと読む)

炭素ナノチューブ薄膜を利用したSRAM

【課題】炭素ナノチューブ(CNT:Carbon NanoTube)薄膜を利用したSRAMを提供する。

【解決手段】少なくとも第1CNTトランジスタを備える第1CNTインバータと、少なくとも第2CNTトランジスタを備え、第1CNTインバータに連結された第2CNTインバータと、少なくとも第1CNTインバータに連結された第1スイッチングトランジスタと、少なくとも第2CNTインバータに連結された第2スイッチングトランジスタと、を備えるSRAMである。

(もっと読む)

重イオン・アップセット硬化浮遊ボディSRAMセル

【課題】ソフトエラーに耐えるSOICMOSSRAMを提供する。

【解決手段】シリコン−オン−絶縁物MOSFETトランジスタを有するCMOSメモリ素子。トランジスタのボディが電源に接続されておらず、その代わりに電気的浮遊を許容するように、MOSFETトランジスタの少なくとも一つが構成されている。重イオン放射によって生じるエラーに対する増加した免疫を備えた開示されたメモリ素子の実施態様。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧でもSNMと書き込みマージンを両立させたSRAMを備える。

【解決手段】第1インバータを構成する第1NMOSとこれに接続された第2NMOSとが形成された第1部分、第1インバータを構成する第1PMOS、第2インバータを構成する第2PMOSとが形成された第2部分と第2インバータを構成する第3NMOSと、これに接続された第4NMOSとが形成された第3部分の順に配置されたSRAMメモリセルを、前記第1方向および第2方向に複数行列状に配列してメモリセルアレイを構成する。複数の第1ビット線は、第2方向のメモリセルの列ごとに設けられ、第2NMOSにそれぞれ接続される。複数の第2ビット線は、第2方向のメモリセルの列ごとに設けられ、各メモリセルの第4NMOSにそれぞれ接続される。

(もっと読む)

半導体装置

【課題】短チャネル効果および閾値の変動の双方を抑制することの可能な半導体装置を提供する。

【解決手段】p型MOSトランジスタ11が形成された第1領域10と、n型MOSトランジスタ21が形成された第2領域20との間に分離部37が形成されている。分離部37は、第1領域10と第2領域20との境界に沿って延在しており、第1領域10と第2領域20とを互いに分離している。分離部37は、さらに、p型MOSトランジスタ11のバックゲートおよびn型MOSトランジスタ21のバックゲートを、少なくとも双方のバックゲート間に電流が流れるのを阻害する程度に互いに電気的に分離している。

(もっと読む)

半導体装置

【課題】ソフトエラー耐性の大きいSRAM(半導体記憶装置)を提供する。

【解決手段】横長型セル(3分割されたウェルがワード線の延在方向に並び、ビット線方向よりもワード線方向に長いメモリセル)上に、第1と第2ドライバMOSトランジスタN1,N2と、第1ロードMOSトランジスタP1,P2と、第1と第2アクセスNMOSトランジスタN3,N4とを設けたフルCMOSSRAMにおいて、記憶ノードとなる埋め込み配線5D,5Gは、ポリシリコン配線3C,3Bの長手方向と交差する方向に延びる傾斜部50D,50Gを有する。

(もっと読む)

半導体集積回路

【課題】SRAMを内蔵した半導体集積回路において、書き込み/読み出し回路と入出力回路とを接続するバスラインの配線長を短縮して、書き込み/読み出し動作の高速化を図る。

【解決手段】この半導体集積回路は、SRAMを内蔵した半導体集積回路であって、該SRAMが、データの複数のビットを複数群に分けてそれぞれ格納する複数群のメモリセルと、複数群のメモリセルの内で対応する群のメモリセルに最も近接するように、所定の間隔で配置された複数群の入出力回路と、複数群の入出力回路に入力されたデータの各群のビットを、対応する群のメモリセルに書き込み、複数群のメモリセルから読み出されたデータの各群のビットを、対応する群の入出力回路に出力する複数群の書き込み/読み出し回路とを具備する。

(もっと読む)

半導体集積回路

【課題】本発明は、メモリ回路部と非メモリ回路部を有する集積回路に関し、論理回路素子に対するソフトエラーとしてのSET(Single Event Transient)を効果的に抑制できる、集積回路を提供する。

【解決手段】論理回路ブロック202に含まれるNMOSトランジスタのチャネルが形成される第2導電型半導体領域101のP型濃度が、SRAMブロック201内のN型の(駆動)トランジスタN1,N2のチャネルが形成される第2導電型半導体領域101のP型濃度より低い。このため、論理回路ブロック202において、より容易に寄生バイポーラトランジスタがオンし、SETの発生要因となるドレイン電位低下を防止する。そのため、回路的負担増なしにSETを効果的に抑制できる。

(もっと読む)

スタティック・ランダム・アクセス・メモリ

【課題】スタティックノイズマージンの低下を抑制できるスタティック・ランダム・アクセス・メモリを得ること。

【解決手段】スタティック・ランダム・アクセス・メモリのメモリセルにおける一対のロードトランジスタは、それぞれ、第1のSiGe膜がシリコン基板のソース領域と第1のシリサイド膜との間に存在し、第2のSiGe膜がシリコン基板のドレイン領域と第2のシリサイド膜との間に存在し、前記第1のSiGe膜ならびに前記第2のSiGe膜は、前記前記ソース領域と前記ドレイン領域の間のチャネル領域のシリコン基板の表面よりも低い位置に存在することを特徴とする。

(もっと読む)

半導体装置の製造方法およびフォトマスク

【課題】極微細なパターンを有するSRAM領域のフィンと周辺回路領域の活性領域とを低コストかつ正確なデザインで形成することのできる半導体装置の製造方法、およびその製造方法に用いられるフォトマスクを提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、第1および第2の領域を有する半導体基板上にマスク材を形成する工程と、前記第1の領域の前記マスク材上に芯材をパターン形成する工程と、前記芯材の両側面に側壁マスクを形成した後、前記芯材を除去する工程と、前記芯材を除去した後、前記第1の領域の前記マスク材に前記側壁マスクのパターンを転写する工程と、前記第1の領域の前記側壁マスクのパターンを転写された前記マスク材のトリミングと、前記第2の領域の前記マスク材への所定のパターンの形成とを同時に行う工程と、を含む。

(もっと読む)

半導体記憶装置

【課題】横型メモリセルレイアウトの6トランジスタ型SRAMメモリセルにおいて、ワード線の寄生容量負荷の増大や、配線パーティクルによる歩留低下を解消する。

【解決手段】第2層目配線にて、列方向に並んで配置された複数のワード線351と、第3層目配線にて、行方向に並んで配置された複数の対をなすビット線352,353と、それぞれ対をなすビット線の間に配置された複数のVDD電源配線354と、第4層目配線にて、ビット線より1層上の配線層で形成されたVSS電源配線とを設けた。VSS電源配線は、VSS電源配線より1層下の配線層で形成された島形状VSSパターンを介してCMOS型SRAMセルと接続されており、VSS電源配線と島形状VSSパターンとの接続が1つの島形状VSSパターンあたり複数のビア部の配置によってなされる。

(もっと読む)

半導体集積回路

【課題】同時に読み書きを行うデュアルポートSRAMにおいて、データの読み出し速度を改善する。

【解決手段】各々のメモリセルは、第1及び第2のストアノードにデータを保持する第1及び第2のインバータと、第1のビット線対と第1及び第2のストアノードとの間にそれぞれ接続された第1及び第2のNチャネルトランジスタによって構成される書き込み/読み出しポートと、第1のストアノードのデータをゲートに受ける第1のPチャネルトランジスタ、第2のビット線対の一方と第1のPチャネルトランジスタのドレインとの間に接続された第2のPチャネルトランジスタ、第2のストアノードのデータをゲートに受ける第3のPチャネルトランジスタ、第2のビット線対の他方と第3のPチャネルトランジスタのドレインとの間に接続された第4のPチャネルトランジスタによって構成される読み出しポートとを具備する。

(もっと読む)

デュアル技術トランジスタを用いた低リーク高性能スタティックランダムアクセスメモリセル

メモリセルは、記憶素子、記憶素子に結合した書込み回路、および記憶素子に結合した読出し回路を具備する。記憶素子の少なくとも一部、および書込み回路の少なくとも一部は、厚い機能性ゲート酸化膜を用いて作られており、読出し回路の少なくとも一部は、薄い機能性ゲート酸化膜を用いて作られている。  (もっと読む)

(もっと読む)

メモリ回路とその導電層の配線

【課題】メモリ回路のビットライン、電圧ライン、ワードラインの配線を提供する。

【解決手段】メモリ回路100のメモリアレイ100aは、データを記憶する少なくとも一つのメモリセル101aを含む。メモリセル101aは、ワードラインWL、ビットラインBL、ビットラインバー、第一電圧ライン、及び第二電圧ラインに結合される。メモリ回路100は、第一導電層、第一導電層に結合される第二導電層、及び、第二導電層に結合される第三導電層を備える。第三導電層は、ワードラインWLに対して配線され、メモリセル101a内で、ビットラインBL、ビットラインバー、第一電圧ライン、及び第二電圧ラインがない。

(もっと読む)

201 - 220 / 629

[ Back to top ]