Fターム[5F083BS27]の内容

Fターム[5F083BS27]の下位に属するFターム

拡散層ゲート (1)

Fターム[5F083BS27]に分類される特許

121 - 140 / 629

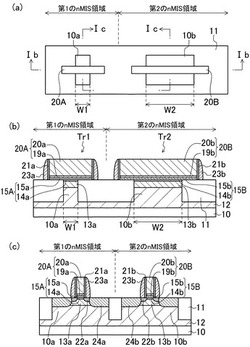

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

マスタスライス方式メモリセル

【課題】複数種類の回路構成をマスタスライス方式で対応可能なメモリセル専用のマスタスライス方式メモリセルを提供すること。

【解決手段】メモリユニットが2行2列に配置されてメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第3拡散層を備え、各拡散層で並列接続のトランジスタが構成される。第1および第2ワード線は第1〜第3拡散層の両端部外方に配置される。第1〜第3拡散層の第1コンタクト層とゲート層の第2コンタクト層との間、第1コンタクト層と第1/第2ワード線との間に、行方向に沿って第1のメタル配線領域が確保される。第1のメタル配線領域には、第2または第3メタル層の何れかが配線可能である。第1及び第2拡散層、第2及び第3拡散層の間には、列方向に沿って第2のメタル配線領域が確保される。第2のメタル配線領域には第3メタル層が配線可能である。

(もっと読む)

半導体装置の製造方法

【課題】デュアルゲート構造を有する半導体装置の製造技術において、MISFETのしきい値電圧の上昇を抑制することができる製造技術を提供する。

【解決手段】ポリシリコン膜PF1上にレジスト膜FR2を形成する。そして、レジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FR2をパターニングする。その後、パターニングしたレジスト膜FR2をマスクにしたイオン注入法により、露出しているnチャネル型MISFET形成領域NTRのポリシリコン膜PF1にアルゴン(Ar+)を導入する。このアルゴン注入工程により、nチャネル型MISFET形成領域NTRのポリシリコン膜PF1はアモルファス化する。

(もっと読む)

半導体装置

【課題】高集積なCMOS型SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体137と第1の第2導電型半導体104との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、第1の第1導電型半導体137の上下に配置された第1の第2導電型高濃度半導体182と、第2の第2導電型高濃度半導体141と、第1の第2導電型半導体104の上下に配置された第1の第1導電型高濃度半導体186と、第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート導電体167と、を有するインバータを用いてSRAMを構成する。

(もっと読む)

半導体記憶装置

【課題】ワード線コンタクトが隣接セルと共有されるSRAMセルを有する半導体記憶装置において、ビット線対の充放電による消費電力を抑える。

【解決手段】半導体記憶装置は、ワード線WLA、WLBと、SRAMセルMC1、MC2と、仲介セルDCとを備える。SRAMセルMC1はワード線WLA、WLBを有し、ワード線WLAが接続されている。SRAMセルMC2はワード線WLA、WLBを有し、ワード線WLBが接続されている。仲介セルDCは、SRAMセルMC1とSRAMセルMC2とに隣接して設けられ、ワード線WLA、WLBが接続されている。複数のSRAMセルMC1及び仲介セルDCの隣接するセル同士がワード線WLA用のコンタクトを共有している。複数のSRAMセルMC2及び仲介セルDCの隣接するセル同士がワード線WLB用のコンタクトを共有している。

(もっと読む)

SRAM装置

【課題】本発明は、SRAMアレイ上のすべてのセルに適切な選択トランジスタのしきい値電圧設定が可能なSRAM装置を提供することを課題とする。

【解決手段】電気的に切り離されたトランジスタ駆動用のゲート及びしきい値制御用の端子を有する電界効果トランジスタを選択トランジスタとして用い、前記選択トランジスタのしきい値制御用端子に対して与える電圧を、読み出し動作時には、読み出し開始時の電圧から徐々に増加させていく回路を具備したSRAM装置。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

半導体装置およびそれを用いた半導体集積回路

【課題】バックゲートを有するMOSを、回路の動作特性に応じて使い分け、幅広い温度範囲にて高速かつ低電力なLSIを実現する。

【解決手段】薄膜埋め込み酸化膜層を持つFD−SOIを使用し、薄膜埋め込み酸化膜層の下層半導体領域をバックゲートとし、論理回路ブロックにおいてブロック中の負荷の軽い論理回路にはバックゲートの電圧をブロック活性化に合わせてブロック外から制御する。このバックゲート駆動信号を発生する回路、及び回路ブロック出力部など負荷の重い論理回路には、ゲートとバックゲートとを接続したトランジスタを用い、そのゲート入力信号でバックゲートを直接制御する。

(もっと読む)

SRAMメモリセル

【課題】現存のデバイスの欠点を取り除き、さらにSRAM型メモリセルの体積を減少させる。

【解決手段】SRAM型メモリセルであって、絶縁層によってベース基板から隔離された半導体材料の薄膜を含む絶縁基板上の半導体と、2個のアクセストランジスタT1,T4と、2個の伝導トランジスタT2,T5と、2個の充電トランジスタT3,T6とを含み、メモリセルは、トランジスタT1−T6のそれぞれが、チャネルの下方でベース基板内に形成されたバックコントロールゲートBG1,BG2を有し、トランジスタの敷居電圧を調整するようにバイアスをかけられ、第1のバックゲートラインはアクセストランジスタT1,T4に接続し、第2のバックゲートラインは伝導トランジスタT2,T5および充電トランジスタT3,T6に接続し、各々の電位はセル制御動作の型に応じて調整される。

(もっと読む)

半導体メモリ装置及びその製造方法

【課題】半導体メモリ装置及びその製造方法を提供する。

【解決手段】第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、第1ウェル領域は、第2ウェル領域と第3ウェル領域との間に配され、第1ウェル領域は、第1タイプ導電体を含み、第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板;第1ウェル領域に一列に形成され、電源端子を共有する第1プルアップ素子及び第2プルアップ素子;第2ウェル領域に第1プルアップ素子と隣接するように配される第1プルダウン素子;第3ウェル領域に第2プルアップ素子と隣接するように配される第2プルダウン素子;第2ウェル領域に第2プルアップ素子と隣接するように配される第1アクセス素子;第3ウェル領域に第1プルアップ素子と隣接するように形成される第2アクセス素子;を含む半導体メモリ装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】集積度が高くリソグラフィーコストが低いn型及びp型FETの積層構造を有した半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板1上にそれぞれ離隔しつつ列状に形成された第1グループの複数の柱状ゲート電極10と、前記半導体基板1上であって前記第1グループの隣接する柱状ゲート電極10間に形成された第1導電型の第1半導体層12と、前記第1半導体層の上であって前記第1グループの隣接する柱状ゲート電極間に形成された第1絶縁層20と、前記第1絶縁層20の上であって前記第1グループの隣接する柱状ゲート電極10間に形成された前記第1導電型と異なる第2導電型の第2半導体層13とを備え、前記第1半導体層12をチャネルとする前記第1導電型の第1MOSFETが形成され、前記第2半導体層13をチャネルとする前記第2導電型の第2MOSFETが形成されている。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた高性能な半導体装置を提供する。

【解決手段】基板上に酸化物半導体層を形成し、酸化物半導体層上に第1の導電層を形成し、第1の導電層上に第2の導電層を形成し、第2の導電層をエッチングすることで、第1のパターンを形成し、第1のパターンを酸化することにより膨張させ、膨張後の第1のパターンをマスクとして第1の導電層をエッチングすることで、ソース電極及びドレイン電極となる第2のパターンを形成し、膨張後の第1のパターン及び第2のパターン及び酸化物半導体層を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する。

(もっと読む)

不揮発性記憶素子及びその制御方法

【課題】故障率及び消費電力を充分に小さくすることができる不揮発性記憶素子を提供する。

【解決手段】複数のメモリセルが配列された不揮発性記憶素子100であって、複数のメモリセルのそれぞれは、端子Aと端子Bとを有するインバータ部と、端子Aとビット線140との導通及び非導通を切り替える選択トランジスタ120と、端子Bとビット線141との導通及び非導通を切り替える選択トランジスタ121と、一端が端子Aに接続された固定抵抗130と、固定抵抗130の他端と信号線144との導通及び非導通を切り替える制御トランジスタ122と、一端が端子Bに接続され、固定抵抗130より高抵抗又は低抵抗となることが可能な可変抵抗131と、可変抵抗131の他端と信号線144との導通及び非導通を切り替える制御トランジスタ123とを備える。

(もっと読む)

半導体集積回路

【課題】セル面積が小さい不揮発性SRAMセルを提案する。

【解決手段】本開示に係わる半導体集積回路は、第1及び第2のインバーターINV1,INV2と、ゲートにワード線WLが接続され、ソースに第1のビット線BLが接続され、ドレインに第2のインバーターINV2の入力端子が接続される第1のトランジスタM5と、ゲートにワード線WLが接続され、ソースに第2のビット線bBLが接続され、ドレインに第1のインバーターINV1の入力端子が接続される第2のトランジスタM6と、第1の端子に第1のトランジスタM5のドレインが接続され、第2の端子に第1のインバーターINV1の出力端子が接続される第1の可変抵抗素子R1と、第1の端子に第2のトランジスタINV2のドレインが接続され、第2の端子に第2のインバーターINV2の出力端子が接続される第2の可変抵抗素子R2とを備える。

(もっと読む)

半導体装置

【課題】並列に並ぶゲートパターンを有する半導体装置において、ゲートパターンのレイアウトを工夫することによって、光近接効果を補正しつつ、集積度を向上させる。

【解決手段】並列に並ぶゲートパターン21,22の端部と、並列に並ぶゲートパターン23,24の対向端部とにおいて、ゲートパターン21の端部はゲートパターン22の端部よりもゲートパターン23,24の方に突き出ており、ゲートパターン24の対向端部はゲートパターン23の対向端部よりも、ゲートパターン21,22の方に突き出ている。引っ込んでいる方の、ゲートパターン22の端部およびゲートパターン23の対向端部について、仕上がり形状において後退が生じない程度に、補正量を大きく設定することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

半導体記憶装置

【課題】マルチポートSRAMのアクセスタイムを高速化すること。

【解決手段】マルチポートSRAMセルを構成する一対のCMOSインバータが形成されたPウエル領域およびNウエル領域に関し、Pウエル領域を、二つのPウエル領域PW1およびPW2に分割してNウエル領域NWの両側に、かつそれら間の境界線がビット線と平行となるように形成する。また、一対のアクセスゲートN3およびN5とN4およびN6とがそれぞれ分割された2つのPウエル領域に形成されることにより、ビット線長を短くし、配線容量を低減させる。

(もっと読む)

電子機器

【課題】実装面積、消費電力、および処理時間の増大を抑えつつ、MNUをはじめとするソフトエラーによって発生する不具合を防止することができる電子機器10を提供する。

【解決手段】本発明の電子機器10は、所定数の命令毎に設けられたチェックポイントを実行する都度、演算装置14内の順序回路に含まれるフリップフロップの状態を示すデータを取って置き、ソフトエラーの予兆を検出した場合に、直前のチェックポイントにおける命令の実行後に取って置いたデータに基づいて演算装置14内の順序回路に含まれるフリップフロップの状態を設定し、直前のチェックポイントに対応する命令の次の命令から実行を再開する。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

スピンMOSトランジスタを用いた不揮発性メモリ回路

【課題】MTJ素子を用いた不揮発性メモリ回路では、電源立ち上げ時にMTJ素子の抵抗値によりメモリの記憶内容が決まる。しかしながら、電源電圧が低いときはMOSトランジスタの抵抗が非常に大きいため、MTJ素子の抵抗値の影響が非常に小さい。そのため、電源電圧が低いときにMOSトランジスタの抵抗値のばらつきにより誤動作を引き起こしやすく、高い信頼性が得られない。信頼性の高い不揮発性メモリ回路を提供することを可能にする。

【解決手段】6トランジスタ(11,12,15,16、21,22)で構成されるメモリセルにおいて、トランジスタ12及びトランジスタ16をn型スピンMOSトランジスタとする。

(もっと読む)

121 - 140 / 629

[ Back to top ]