Fターム[5F083BS27]の内容

Fターム[5F083BS27]の下位に属するFターム

拡散層ゲート (1)

Fターム[5F083BS27]に分類される特許

161 - 180 / 629

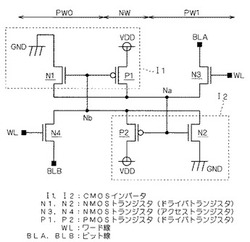

半導体記憶装置及び半導体装置

【課題】回路構成を複雑化することなくソフトエラー低減化を図ったメモリセル構造を有する半導体記憶装置を得る。

【解決手段】NMOSトランジスタN1及びPMOSトランジスタP1によるインバータI1(出力部が記憶端子Na)とNMOSトランジスタN2及びPMOSトランジスタP2によるインバータI2(出力部が記憶端子Nb)とが交叉接続され、さらにNMOSトランジスタN3及びN4が記憶端子Na及びNbにそれぞれ接続される。記憶端子Naに一方電極が接続されるNMOSトランジスタN1及びN3はPウエル領域PW0及びPW1に分けて形成されるともに、記憶端子Nbに一方電極が接続されるNMOSトランジスタN2及びN4はPウエル領域PW1及びPW0に分けて形成される。Pウエル領域PW0及びPW1はNウエル領域NWを挟んで各々反対側に形成される。

(もっと読む)

半導体装置

【課題】CAMにおけるメモリセル面積の縮小化を図る。

【解決手段】データ線(D0,D1)を第1記憶部(MA)及び第2記憶部(MB)とで共有し、また、第1比較データ線(CD0)に結合された第1トランジスタ(MC0)と、第1記憶部の記憶ノードに結合された第2トランジスタ(MCA)とを直列接続して第1比較回路(11)を形成し、第2比較データ線(CD1)に結合された第3トランジスタ(MC1)と、上記第2記憶部の記憶ノードに結合された第4トランジスタ(MCB)とを直列接続して第2比較回路(12)を形成することは、拡散層や配線層のレイアウトにおける対称性を向上させ、メモリセルをその中心を通る中心線に対して線対称となるレイアウトの容易化を達成する。それにより製造プロセス条件を最適化し易くなり、製造プロセスのばらつきが低減されてメモリセルの微細化が達成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルの面積を減少させる。

【解決手段】半導体装置は、基板上のメモリセル領域内に設けられた第1活性領域と、第1活性領域と素子分離により分離され、第1活性領域内よりもメモリセル領域の中心に近い位置に設けられた第2活性領域と、第1活性領域を横断する第1ゲート電極と、第1ゲート電極と離間し、第1活性領域および第2活性領域を横断する第2ゲート電極と、第1活性領域で、第1ゲート電極と第2ゲート電極との間の第1ドレイン部と、第2活性領域で、第2ゲート電極の第1ドレイン部側の第2ドレイン部と、第1ドレイン部と第2ドレイン部とを接続する第1配線と、第1ゲート電極および第2ゲート電極と離間し、端部が第1ゲート電極の第2活性領域側の端部と対向する第3ゲート電極と、第2ドレイン部と第3ゲート電極とを接続する第2配線とを備え、第3ゲート電極の上面と第2配線の上面はほぼ同じ高さに形成されている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

半導体記憶装置

【課題】SRAMメモリセルをFD−SOIトランジスタで構成し、駆動トランジスタを構成するSOIトランジスタの埋め込み酸化膜の下の層の電位を制御して、低電源電圧状態でのSRAM回路の性能を向上させる。

【解決手段】FD−SOIトランジスタを用いて構成されたSRAMメモリセルにおいて、駆動トランジスタのBOX層下のウエル電位を制御することでVthを制御して電流を増加させて、メモリセルの安定動作を可能とする。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の評価方法

【課題】大規模なSRAMセルの特性を高精度に測定する半導体装置及びそれを用いた評価方法を提供する。

【解決手段】m行n列のマトリクス状に配列されるSRAMセルを有する評価セルC11〜Cnmと、SRAMセルのSNM特性を測定する際にSRAMのラッチノードへ入力電圧を供給し、或いは出力電圧を検出する第1の主入出力線V0等と、評価セルを選択するための行選択信号供給用の行選択線X1〜Xmと、列選択信号供給用の列選択線Y1〜Ynと、入力される行選択信号と列選択信号に応じてSRAMセルの選択/非選択を表す選択信号を出力する選択回路10と、を備え、選択信号供給回路に入力される選択制御信号等により行選択信号と列選択信号を生成し、評価セル各々に設けられた第1のトランジスタT1〜第6のトランジスタT6を切り替え、SRAMセルの測定評価を行う。

(もっと読む)

半導体装置

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲む第1のゲート電極と、第1のゲート電極の周囲を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲を取り囲む第1の筒状半導体層と、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第1の筒状半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第1の筒状半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有するインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

半導体記憶装置

【課題】低電圧動作させた場合においても、メモリセルのサイズを低減させつつ、安定動作を実現するとともに、セルトランジスタのばらつきによる影響を低減する。

【解決手段】第1および第2のPMOSのソースは第1の電源線、第1のPMOSのドレインは第1のノード、第2のPMOSのドレインは第2のノード、第1および第2のNMOSのソースは第2の電源線、第1のNMOSのドレインは第1のノード、第1のノードは、第2のPMOSのゲートと第2のNMOSのゲート、第2のノードは、第1のPMOSのゲートと第1のNMOSのゲート、第1のトランジスタのゲートは、第1の信号線、ソースは第1のノード、ドレインは第2のノード、第2のトランジスタのゲートは、第2のノード、ソースは第3のノード、ドレインは第2の信号線、第3のトランジスタのゲートは、第3の信号線、ソースは第4の信号線、ドレインは第3のノードに接続される。

(もっと読む)

半導体集積回路およびその動作方法

【課題】スタンバイ時の保持データ量の変化に対応すること。

【解決手段】半導体集積回路は、ロジック回路logicと、複数のSRAMモジュール2、3を具備する。複数のSRAMモジュールは、ロジック回路と独立に電源制御が可能とされ、複数のSRAMモジュールの間で独立した電源制御が可能とされる。具体的には、各SRAMモジュールの電位制御回路の一方の端子arvssと他方の端子vssmはセルアレーcell_arrayとローカル電源線vssmに接続される。一方のSRAMモジュール2と他方のSRAMモジュール3とのローカル電源線vssmは、共有ローカル電源線vssm22によって共有されている。一方と他方のSRAMモジュール2、3の一方と他方の電源スイッチPWSW22、PWSW23とは、共有ローカル電源線vssm22に共通に接続される。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成されたトランジスターの閾値電圧のバラツキを低減できるようにした半導体装置を提供する。

【解決手段】絶縁層上に半導体層が形成された基板と、前記半導体層に形成されたトランジスターと、を備え、前記トランジスターは、前記半導体層上にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極の両側下の前記半導体層に形成されたソース又はドレインと、前記ゲート電極直下の前記半導体層において前記トランジスターのゲート幅方向に沿って電流を流すための入力側端子及び出力側端子と、を有する。

(もっと読む)

断熱充電メモリ回路

【課題】pMOSトランジスタのソース電極の電位を一定にしつつ、微細化に起因するエレクトロマイグレーションによる配線の断線を防止する。

【解決手段】まず、ワード線WLを零電位とし、スイッチ素子S1、S2がオン、オフの状態で、ビット線BL、NBLを正電位VDDまで昇圧する。スイッチ素子S1をオフし、スイッチ素子S2をオンし、スイッチ素子S2を介して、グラウンド線MCGLを、フリップフロップ回路FFの時定数より長い時間をかけて、正電位VDDに昇圧する。スイッチ素子S2をオフする。ワード線を正電位VDDとする。ビット線BL、NBLの内のフリップフロップ回路FFにデータ0を書き込む側のビット線、例えば、ビット線NBLを、フリップフロップ回路FFの時定数より長い時間をかけて、零電位に降圧する。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置が備えるnMOSトランジスタ及びpMOSトランジスタの形成面積を縮小する。

【解決手段】半導体装置の製造方法は、基板上に環状の突起部を形成する工程と、環状の突起部に第1のn型チャネル領域を形成する工程と、環状の突起部に第1のp型チャネル領域を形成する工程と、環状の突起部に形成された第1のn型チャネル領域及び第1のp型チャネル領域を跨ぐ第1のゲート電極を形成することにより、第1のnMOSトランジスタ及び第1のpMOSトランジスタを形成する工程と、を備える。

(もっと読む)

半導体装置、電気光学装置、電子機器

【課題】ある応力がかかっても回路全体としての動作特性が変化しない薄膜の半導体素子を実現し、これによって、動作マージンが広く大型化が容易なフレキシブルな半導体装置、電気光学装置、電子機器を提供する。

【解決手段】本発明の半導体装置は、基板100上に薄膜トランジスタ8を有し、この薄膜トランジスタ8は、基板100の湾曲に対してチャネル内のキャリアの移動度が相補的に変化する第1のチャネル領域1cおよび第2のチャネル領域1cを有している。

(もっと読む)

デュアルポートSRAMセルの構造

【課題】デュアルポートSRAMセルの構造とレイアウト設計を提供する。

【解決手段】マルチポートSRAMセルと、第1ビット線導体と、第1相補ビット線導体と、第2ビット線導体と、第2相補ビット線導体と、SRAMセルのアクセスポートに接続された第1ワード線と第2ワード線、及びVdd電力供給導体と、4つのVss電力供給導体とを含み、前記ビット線導体と前記電力供給導体は、第1共通金属化層に平行に設置されるメモリデバイス。

(もっと読む)

161 - 180 / 629

[ Back to top ]