Fターム[5F083BS27]の内容

Fターム[5F083BS27]の下位に属するFターム

拡散層ゲート (1)

Fターム[5F083BS27]に分類される特許

101 - 120 / 629

半導体装置およびその製造方法

【課題】高密度で素子特性に優れた、SRAMを備えた半導体装置を提供する。

【解決手段】一対の駆動トランジスタと一対の負荷トランジスタと一対のアクセストランジスタを備えたSRAMセル単位を有する半導体装置であって、前記トランジスタはそれぞれ、基体平面に対して上方に突起した半導体層と、この半導体層を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体層の間に介在するゲート絶縁膜と、前記半導体層に設けられた一対のソース/ドレイン領域を有し、前記駆動トランジスタはそれぞれ、前記負荷トランジスタ及び前記アクセストランジスタの少なくとも一方の各トランジスタのチャネル幅より広いチャネル幅を有する半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

メモリセルアレイを用いたIDチップおよびその生成方法

【課題】認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報を半導体メモリに予め搭載でき、セキュリティの向上を図れるIDチップおよびその生成方法を提供する。

【解決手段】本IDチップは、メモリセルアレイを構成する個々のメモリセルの閾値電圧のバラツキにより、メモリセルアレイに生成されたランダムなデータを固有の識別情報として用いた構成とされる。このメモリセルは、“0” または“1”の初期データが書き込まれた後に、両ビット線を同時に“Low”または“High”としてデータを生成する。そして、生成されたデータを用いて同一チップか否かを判別する。チップの判別は、メモリセルアレイのデータのハミング距離を測定し、ハミング距離が所定閾値以内の場合に同一チップと判別する。

(もっと読む)

半導体記憶装置

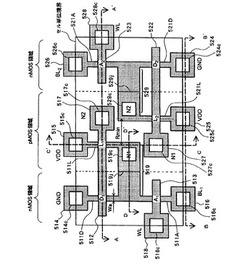

【課題】SRAMのゲート配線形成にあたって、ゲート形状を複雑に変形させることなく転写及び加工マージンを確保する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1組及び第2組のドライバトランジスタ11、ロードトランジスタ12及びアクセストランジスタ13とを備えたメモリセルが半導体基板上に2次元配列されたメモリセルアレーと、複数のワードラインと、複数のビットラインと、第1組のドライバトランジスタ11とロードトランジスタ12とを接続し、直線状の側辺を有する長方形状の第1ゲート配線3aと、アクセストランジスタ13と接続され、直線状の側辺を有する長方形状の第2ゲート配線3cと、第1ゲート配線3aと、第2組のドライバトランジスタ11とロードトランジスタ12とを接続する第1コネクタ5aと、第2ゲート配線3cとワードラインとを接続する第2コネクタ5cとを備える。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定かつ高速に動作する半導体記憶装置を実現する。

【解決手段】メモリセル列ごとにアレイ電源線(ARVD)およびダウン電源線(DWVD)を配置する。ダウン電源線は、読出し時に接地に結合され、書込み時にフローティング状態とされる。書込み時、選択列のアレイ電源線への電源電圧の供給を停止するとともに該アレイ電源線を対応のダウン電源線に接続する。電源系統を複雑化することなく、低電源電圧下においても安定にデータの書込/読出を行うことのできる半導体記憶装置を実現することができる。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体集積回路

【課題】トランジスタの性能の劣化の防止に有利な半導体集積回路を提供する。

【解決手段】実施形態によれば、半導体集積回路は、ワード線とビット線との交差位置にそれぞれ配置されデータを保持するデータ記憶部(SRAMセル)と前記データ記憶部に記憶された保持データを論理的に反転させる反転回路22と、前記データ記憶部が記憶するデータの論理反転の有無を識別するフラグをロウ単位で記憶するフラグビットカラム11−1とを備える、メモリセルアレイ11を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】動作マージンの向上に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板上に、互いのゲート電極が接続されて配置される第1トランジスタ(P2)と、前記第1トランジスタと異なる導電型を有する第2トランジスタ(N4)とを具備し、前記第1トランジスタのゲート電極は、第1不純物と前記第1不純物の拡散を抑制する第2不純物とを含有し、前記第1不純物の濃度ピーク(PE1)は、前記第2不純物の濃度ピーク(PE2)よりも浅い位置に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】マスクの新規な作製技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、第1の膜を形成する工程と、第1の膜上方に、第1マスク膜を形成する工程と、第1マスク膜をパターニングする工程と、パターニングされた第1マスク膜の側部にプラズマ処理を行って、側部を変質層に変換する工程と、プラズマ処理の後、第1マスク膜の上部及び側部を覆う第2マスク膜を形成する工程と、第2マスク膜をエッチングして、側部に形成された第2マスク膜を残存させつつ、第1マスク膜上部に形成された第2マスク膜を除去する工程と、第2マスク膜のエッチングの後、変質層を除去する工程と、変質層を除去した後、残った部分の第1マスク膜、及び第2マスク膜をマスクとして、第1の膜をエッチングする工程とを有する。

(もっと読む)

半導体記憶装置

【課題】給電セルのレイアウト面積を縮小することによりメモリアレイ全体のレイアウト面積をさらに縮小することが可能な半導体記憶装置を提供する。

【解決手段】第1の金属配線層に、Nウェル電圧VDDBを供給するメタル312を設ける。メタル312は、共有コンタクト216および219によりNウェル領域に設けられた活性層300と電気的に結合され、Nウェル領域に対してNウェル電圧VDDBが供給される。第3の金属配線層にPウェル電圧VSSBを供給するメタル332,333を設ける。Nウェル電圧VDDBを供給するメタル312は、第1の金属配線層のメタルを用いた構成としているため下層へのくい打ち領域を必要とせず、Pウェル電圧VSSBのメタル332,333の下層へのくい打ち領域のみ確保すればよい。したがって、給電セルPMCのY方向の長さを縮小して、給電セルのレイアウト面積を縮小することができる。

(もっと読む)

半導体装置

【課題】CMOSインバータを含むメモリセルにおいて、リーク電流によるゲート配線の制約やデザインルールの制約を起因とするメモリセルの面積の増大を抑える。

【解決手段】第1のインバータIV1と第2のインバータIV2を含むメモリセル1Aの第1の金属層として、第1の配線FL1及び第2の配線FL2が配置されている。第1の配線FL1は、第1のインバータIV1の2つのドレインDと第2のインバータIV2の第2のゲート配線GL2と接続している。第2の配線FL2は、第2のインバータIV2の2つのドレインDと第1のインバータIV1の第1のゲート配線GL1と接続している。第1の配線FL1は第2のゲート配線GL2と重畳し、第2の配線FL2は第1のゲート配線GL1と重畳して配置される。第1の金属層よりも上層には、第2の金属層と、その上層の第3の金属層が配置されている。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

サブスレッショルドSRAMのための電源電圧制御回路及び制御方法

【課題】サブスレッショルド領域で動作するSRAMの書き込み動作安定性を改善する回路及び方法を提供する。

【解決手段】所定の遅延時間でサブスレッショルド領域で動作し、pMOSFETの典型値におけるしきい値電圧と、nMOSFETの典型値におけるしきい値電圧の差の絶対値が0.1V以上であるサブスレッショルドSRAMに対して制御出力電圧を電源電圧として供給する電源電圧制御回路であって、電源電圧に基づいて所定の微小電流を発生する微小電流発生回路と、発生された微小電流に基づいて遅延時間のバラツキを補正するためのpMOSFET又はnMOSFETのしきい値電圧の変化を含む制御出力電圧を発生して、制御された電源電圧としてサブスレッショルドSRAMに対して供給する制御出力電圧発生回路とを備えた。

(もっと読む)

SRAM

【課題】配線不良が生じ難いSRAM。

【解決手段】第1方向に平行に延設された第1、第2ゲート電極と、第1ゲート電極と直交して第1負荷トランジスタを構成する第1拡散領域及び第1の駆動トランジスタを構成する第2拡散領域と、第2拡散領域と直交して第1アクセストランジスタを構成する第3ゲート電極と、第1拡散領域と第2ゲート電極との第1共通コンタクトと、第1及び第3ゲート電極間の第2拡散領域に形成された第1拡散領域コンタクトと、第3ゲート電極に接続された第1ゲートコンタクトと、第1共通コンタクトと第1拡散領域コンタクトとを接続する第1配線と、第1ゲートコンタクトに接続された第2配線と、を備えたSRAM。第1共通コンタクトと第1ゲートコンタクトとが階段状の2層構造を有し、第1及び第2配線はいずれも第1方向を長手方向とする矩形形状を有し、第1の方向の一直線上に並べて配置されている。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

対向電極を有する小型電界効果トランジスタおよび製造方法

【課題】小型化の増進を可能にするとともに、実現が容易な、対向電極を備えた電界効果トランジスタの製造方法を提供する。

【解決手段】ゲート電極9ソースコンタクト12,ドレインコンタクト13、および対向電極コンタクトの輪郭描写パターンを含むエッチングマスクが、セミコンダクタ・オン・インシュレータ型の基板上に形成される。基板は、誘電体5の層およびゲート材料により覆われる。対向電極コンタクトは、ゲート電極9のパターン内に配置される。ゲート材料は、ゲート電極9、ソースコンタクト12およびドレインコンタクト13、ならびに対向電極コンタクトを画定するためにエッチングされる。支持基板2の一部分は、対向電極コンタクト領域のパターンの中を通って解放される。導電性材料22が支持基板2の自由部分上に堆積されて、対向電極コンタクトを形成する。

(もっと読む)

プロセス評価用半導体集積回路

【課題】 微妙なプロセスコントロールのための判断材料となる情報を短時間のうちに採取することができるプロセス評価用半導体集積回路を提供する。

【解決手段】 プロセス評価用半導体集積回路としてのSRAMは、メモリセルに電源電圧を供給する給電系統と、メモリセル以外の回路に電源電圧を供給する給電系統とが分離されており、メモリセルに供給する電源電圧を他の回路に対する電源電圧と独立に制御可能な構成となっている。メモリセルに対する電源電圧を段階的に下げつつ、各メモリセルに対するアクセスを試み、動作不良を検出することにより、メモリセル間のトランジスタの電気的特性の微妙な変化を判定することができる。

(もっと読む)

SRAM

【課題】微細かつリーク電流が抑制されたSRAM。

【解決手段】第1の負荷トランジスタLT1を構成する第1のゲート電極G1bと、第1のゲート電極G1bの長手方向の延長上に、これと離間して延設され、第1の駆動トランジスタDT1を構成する第2のゲート電極G1aと、第1のゲート電極G1bと平行に延設され、第2の負荷トランジスタLT2を構成する第3のゲート電極G1bと、第3のゲート電極G1bと交差して形成され、第2の負荷トランジスタLT2を構成する第1のP型拡散領域PD21と、第1のゲート電極G1b及び第2のゲート電極G1a及び第1のP型拡散領域PD21に跨って形成された第1の共通コンタクトSC2と、を備えるSRAM。第1のP型拡散領域PD21は、第1のゲート電極G1bと第2のゲート電極G1aとの間隙領域近傍まで延設され、かつ、当該間隙領域には形成されていない。

(もっと読む)

101 - 120 / 629

[ Back to top ]