Fターム[5F083BS27]の内容

Fターム[5F083BS27]の下位に属するFターム

拡散層ゲート (1)

Fターム[5F083BS27]に分類される特許

81 - 100 / 629

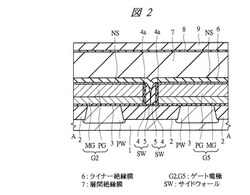

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

半導体記憶装置

【課題】メモリアレイの面積を不必要に増大させることなく、マスクパターンの孤密差に起因する特性ばらつきを低減する。

【解決手段】半導体記憶装置は、複数の要素ブロックA及びBを含むメモリアレイと、メモリアレイの終端部に配置された要素ブロックAに隣接して設けられるが実際には使用されないダミーブロックD1及びD2と、を有し、ダミーブロックD1及びD2のレイアウトパターンは、要素ブロックAのレイアウトパターンの一部分のみである。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

電界効果トランジスタを備える半導体素子及びその製造方法

【課題】電界効果トランジスタを備える半導体素子及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成され、第1活性領域の上面及び向き合う側面を経て伸張する第1ゲート電極を有する第1導電型の第1FET素子と、前記第1FET素子上に形成された層間絶縁膜と、前記層間絶縁膜上に形成され、第2活性領域の上面及び向き合う側面を経て伸張する第2ゲート電極を有する第2導電型の第2FET素子と、を備える。

(もっと読む)

半導体記憶装置

【課題】低消費電力化できる半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、ワード線WLと相補関係にあるビット線対(BLc,BLt)との交差位置に配置され、第1ノード(1N)に与えられる第1電源電圧Vddと仮想ノードVNに与えられる電圧との間におけるデータを記憶するメモリセルMCと、入力および出力が前記仮想ノードと第2電源電圧Vssとの間に配置され、制御端子が前記ビット線対に接続され、前記ビット線対の振幅をモニタし、前記ビット線対に十分な振幅が発生した場合に、前記第2電源電圧Vssへの電流経路を制限するリミッター回路11とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクトの接触不良を防止して、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】高密度版回路における電界効果トランジスタTr3のゲート電極G3と電界効果トランジスタTr4のゲート電極G4とのピッチは、高速版回路における電界効果トランジスタTr1のゲート電極G1と電界効果トランジスタTr2のゲート電極G2のピッチよりも小さいが、シェアードコンタクトホールSCが達する部分のゲート電極G3に切欠を設けることにより、シェアードコンタクトホールSCと不純物領域S/Dとの接触面積を広くする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

記憶装置、集積回路装置、及び電子機器

【課題】マルチポートメモリーとして機能する場合に、クロストークノイズを大幅に低減して、誤動作を防止して回路動作の安定化を図る記憶装置等を提供する。

【解決手段】メモリーセルアレイ10を有する半導体記憶装置100は、第1の方向に並ぶメモリーセルを選択するための第1のワードラインと、第2の方向に並ぶメモリーセルを選択するための第2のワードラインと、第1のワードラインによって選択されたメモリーセルに接続される一対の第1のビットライン及び第1の相補ビットラインと、前記第2のワードラインによって選択されたメモリーセルに接続される第2のビットラインとを含み、第2のワードラインは、対応する一対の第1のビットライン及び第1の相補ビットラインに対し、上面から見て第1の方向又は該第1の方向の反対方向に隣接して、第2の方向に延びるように配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の形状を精度良く形成すると共に、隣り合うゲート電極同士がショートすることを防止する。

【解決手段】開口部を有するマスク16Mを用いて、導電膜15にイオンを注入し、ミキシング膜20Xを形成する。次に、マスクを除去した後、導電膜及びミキシング膜の上に、平面形状がライン形状のレジストパターン21を形成する。次に、レジストパターンをマスクとして、導電膜及びミキシング膜をエッチングし、導電膜15aを有するゲート電極を形成すると共に、ゲート電極のゲート幅方向の側面の上に、ミキシング膜20xを残存させる。次に、熱処理により、ミキシング膜に含まれるイオンと、元素(元素は、導電膜に由来する)とを反応させて、絶縁膜24xを形成する。絶縁膜は、ゲート電極と一体に形成されている。絶縁膜により、ゲート電極と、該ゲート電極とゲート幅方向に沿って隣り合う他のゲート電極との間が電気的に分離されている。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタの特性ばらつきを増大させることなく、面積が縮小可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1における第1の素子分離領域2aに囲まれた第1の活性領域1aと、第1の活性領域上に順次形成された第1のゲート絶縁膜6a、第1のゲート電極9aとを有する第1のMISトランジスタと34と、半導体基板1における第2の素子分離領域2bに囲まれた第2の活性領域1bと、第2の活性領域上に順次形成された第2のゲート絶縁膜6b、第2のゲート電極9bとを有する第2のMISトランジスタ32とを備える。第1のゲート電極9aは、第1の活性領域1aの上面上だけでなく側面上に第1のゲート絶縁膜6aを介して形成されており、第2のゲート電極9bは、第2の活性領域1bの上面上に形成されており、側面上には形成されない。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】SRAMは高速で省電力なメモリであるが、携帯機器等で使用するにはさらなる省電力化が求められる。

【解決手段】オフ抵抗が極めて高いトランジスタを書き込みトランジスタとし、書き込みトランジスタのドレインを書き込みビット線に、ソースをCMOSインバータの入力に接続し、読み出しトランジスタのドレインを読み出しビット線に、ソースをCMOSインバータの出力に接続したメモリセルを用いる。書き込みトランジスタのソースにはキャパシタを意図的に設けてもよいが、CMOSインバータのゲート容量あるいはCMOSインバータの正極や負極との間の寄生容量等を用いることもできる。データの保持はこれらのキャパシタに蓄積された電荷によっておこなえるため、CMOSインバータの電源間の電位差を0とできる。このため、CMOSインバータの正負極間を流れるリーク電流がなくなり、消費電力を低減できる。

(もっと読む)

81 - 100 / 629

[ Back to top ]