Fターム[5F083BS27]の内容

Fターム[5F083BS27]の下位に属するFターム

拡散層ゲート (1)

Fターム[5F083BS27]に分類される特許

141 - 160 / 629

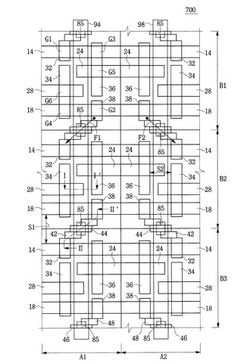

半導体セル構造物、上記半導体セル構造物を含む半導体装置、及び上記半導体装置を含む半導体モジュール

【課題】所定の整列関係を有する単位セルを含む半導体セル構造物を提供すること。

【解決手段】単位セルは、活性領域14、18、24、28、ゲートパターン32、34、36、38、ダミーパターン42、44、46、48、及び導電パターン94を有する。ゲートパターン32、34、36、38は活性領域14、18、24、28と交差する。ダミーパターン42、44、46、48は単位セルを電気的に接続する。選択された単位セル内のダミーパターン42、44、46、48は、選択された単位セル内のゲートパターン32、34、36、38との間に対角的に配置される。導電パターン94はダミーパターン42、44、46、48と電気的に接続する。これにより、半導体セル構造物は、行及び列に沿って互い突出しない単位セルを有することができる。上述した半導体セル構造物は半導体装置及び半導体モジュールに配置される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】注入マスクの低減が図られる半導体装置の製造方法と、そのような半導体装置を提供する。

【解決手段】レジストマスク31と他のレジストマスクを注入マスクとして、NMOS領域RNにボロンを注入することにより、アクセストランジスタおよびドライブトランジスタのハロ領域となるp型不純物領域が形成される。さらに他のレジストマスクを注入マスクとして、PMOS領域RPにリンまたは砒素を注入することにより、ロードトランジスタのハロ領域となるn型不純物領域が形成される。

(もっと読む)

半導体装置の製造方法

【課題】メモリセルレイアウトを提供する。

【解決手段】メモリセルレイアウトに特徴のある製造方法が開示される。一例として、ダミー層と、ダミー層の側壁に沿ったスペーサを形成するステップを含む。一旦、スペーサが形成されると、ダミー層が除去され、スペーサがマスクとして用いられる。標準のリソグラフィックプロセスに代わって、スペーサを用いることにより、リソグラフィックプロセスの固有の限界が回避され、フィンFET装置のさらなるスケーリングが達成される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】1メモリセルが6トランジスタを有するSRAMにおいて、コンタクトの微細化をするとリークの発生を回避できる半導体記憶装置及びその製造方法を提供する。

【解決手段】1メモリセルが第1及び第2ドライバトランジスタ(DTr1、DTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)並びに第1及び第2ロードトランジスタ(LTR1,LTr2)の6トランジスタを有するSRAMにおいて第1ドライバトランジスタと第2ドライバトランジスタのソースドレイン領域に基準電位を印加するための接地コンタクトCgと、第1ロードトランジスタと第2ロードトランジスタのソースドレイン領域に電源電位を印加するための電源電位コンタクトCcの径が、共通コンタクトCsを除く他のコンタクト(Cb,Cn,Cw)の径より大きく形成された構成とする。

(もっと読む)

集積回路およびその形成方法

【課題】製造コストを良好に減少できる集積回路およびその形成方法を提供する。

【解決手段】集積回路は、第1のメモリアレイ、および第1のメモリアレイに接続された論理回路を含み、第1のメモリアレイの全てのメモリセルの全ての活性トランジスタおよび論理回路の全ての活性トランジスタは、フィン電界効果トランジスタ(FinFET)であり、第1の縦方向に沿って配置されたゲート電極を有する。FinFETs300a〜300cは、基板301上に配置され得る。基板301は、複数の活性領域305a〜305cを含み得る。活性領域305a〜305cは、基板301の表面301a上の非平面活性領域であり得る。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体装置

【課題】SRAMを有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に形成された6つのnチャネル型トランジスタQNA1,QNA2,QNA3,QNA4,QND1,QND2と、2つのpチャネル型トランジスタQPL1,QPL2とによって構成されるメモリセルMC1を有する半導体装置である。シリコン基板1上には、行方向に見て、順に、第1pウェルPW1、第1nウェルNW1、第2pウェルPW2、第2nウェルNW2、および、第3pウェルPW3が配置されている。第1および第2正相アクセストランジスタQNA1,QNA2は第1pウェルPW1に配置され、第1および第2ドライバトランジスタQND1,QND2は第2pウェルPW2に配置され、第1および第2逆相アクセストランジスタQNA3,QNA4は第3pウェルPW3に配置されている。

(もっと読む)

半導体装置の製造方法、フラッシュメモリの製造方法、およびスタティックランダムアクセスメモリの製造方法ならびにフラッシュメモリ

【課題】同一のレジストパターンにより、ドライエッチングおよびウエットエッチングを連続的に行なう際に、変質したレジスト表面層を剥がれなくするように改良された、半導体装置の製造方法を提供することを主要な目的とする。

【解決手段】半導体基板1の上に、絶縁膜2と導電層3を順次形成する。導電層3の上にレジストパターン4を形成する。レジストパターン4をマスクに用いて、導電層3をドライエッチングする。レジストパターン4の表層部を一部削る。レジストパターン4をマスクに用いて、絶縁膜2をウエットエッチングする。

(もっと読む)

集積回路

【課題】マルチフィンを有するFinFETを利用したSRAM構造を提供する。

【解決手段】SRAMセルは、ストレートフィンと、ストレートフィンから物理的に切り離された屈曲フィンからなる。屈曲フィンは、ストレートフィンに平行な第一部分と第二部分を有する。屈曲フィンの第一部分とストレートフィンの間の距離は、屈曲フィンの第二部分とストレートフィンの間の距離より小さい。SRAMセルは、第一ゲートストリップの一部分を含むプルダウントランジスタからなり、それぞれ、ストレートフィンと屈曲フィンの第一部分を有する第一と第二サブプルダウントランジスタを形成する。SRAMセルは、更に、第二ゲートストリップの一部分を含むパスゲートトランジスタからなり、ストレートフィンを有する第一サブパスゲートトランジスタを形成する。プルダウントランジスタは、パスゲートトランジスタより多いフィンを有する。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

半導体装置

【課題】低酸素処理を施したシリコン基板は基板表面層が応力に対して非常にもろくなってしまい、ハンド津愛想うちの製造プロセスの過程でクラックや反りが発生する原因ともなってしまう。

【解決手段】チャネル形成領域に形成された不純物領域に応力を集中させるため、チャネル形成領域に対して人為的かつ局部的に不純物領域を設ける。チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)の領域は、低酸素処理を施したシリコン基板の応力を緩和する緩衝領域として機能する。

(もっと読む)

半導体装置

【課題】周辺回路に供給される電源電圧が変化しても、メモリセルの動作マージンを適切な値に調整することができる半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置100は、メモリセルアレイ201と周辺回路202とを有するSRAM200と、周辺回路202に供給されるコア電源電圧VDDの変化に応じて、当該コア電源電圧VDDのα倍(α>1)のメモリセル電圧VMMを生成し、メモリセルアレイ201に供給するメモリセル電圧生成部300とを備える。

(もっと読む)

集積回路構造、及び集積回路の製造方法

【課題】異なるフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、第1装置領域の第1部分と、第2装置領域の第2部分と、を有する半導体基板からなる。第1半導体フィンは半導体基板上にあり、第1フィン高さを有する。第2半導体フィンは半導体基板上にあり、第2フィン高さを有する。第1フィン高さは第2フィン高さより高い。

(もっと読む)

SRAM

【課題】微細かつ寸法ばらつきが小さいSRAM。

【解決手段】第1の方向に直線状に延設された第1及び第2のゲート電極G1、G2と、第1のゲート電極G1と直交して第1の負荷トランジスタLT1を構成するとともに、第2のゲート電極G2の一端近傍まで延設された第1の拡散領域PD11と、第2のゲート電極G2と直交して第2の負荷トランジスタLT2を構成するとともに、第1のゲート電極G1の一端近傍まで延設された第2の拡散領域PD21と、を備えるSRAM。第1の拡散領域PD11は、第2のゲート電極G2側かつ第2の拡散領域PD21側に第1の切欠領域A1を備え、第2の拡散領域PD21は、第1のゲート電極G1側かつ第1の拡散領域PD11側に第2の切欠領域A2を備え、第1の切欠領域A1と第2の切欠領域A2とは、少なくとも一部が互いに対向し合うように設けられている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

設計規則違反を低減するために多重露光及び遮断マスクの手法を用いる半導体デバイス製造

【解決手段】

半導体デバイス(400)を製造する方法は、半導体材質(402)の層及び半導体材質(402)の層の上の絶縁材質(404)の層を備える基板上に、ハードマスク材質(408)の層が絶縁材質(404)の層の上になるように、ハードマスク材質(408)の層を形成することによって開始する。多重露光フォトリソグラフィ手順が実行されて、ハードマスク材質(408)の層の上にフォトレジスト特徴部の結合されたパターンが作製され、またフォトレジスト特徴部の結合されたパターンを用いてハードマスク材質内に凹部線パターンが作製される。方法は、凹部線パターン(422)の指定された区画をフォトレジスト特徴部の遮断パターン(442)で覆い、そして溝(452)のパターンを絶縁材質(404)内に形成することによって継続し、ここで溝(452)のパターンは、フォトレジスト特徴部の遮断パターン(442)及びハードマスク材質(408)によって規定される。その後、電気伝導材質(472)が溝(452)内に堆積させられて、半導体デバイスのための導電線がもたらされる。

(もっと読む)

141 - 160 / 629

[ Back to top ]