Fターム[5F083EP00]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423)

Fターム[5F083EP00]の下位に属するFターム

Fターム[5F083EP00]に分類される特許

101 - 120 / 134

集積回路装置の製造方法

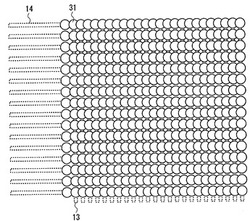

【課題】 本発明の目的は、リソグラフィー技術の限界を破ることのできる、微細な細線構造を備えた集積回路装置、特に集積記憶装置の製造方法を提供することにある。

【解決手段】 基板上に、絶縁体で分離された複数の素子を、第一の方向において50nm以下のピッチで配置し、第二の方向では前記ピッチの1.2倍以上かつ2倍以下のピッチで配置し、前記複数の素子が接続する下配線を用いて複数の素子に電位を付与して、素子表面に電解メッキ法により金属ドットを成長させて、第二の方向に並ぶ複数の素子に接続する金属配線を形成する工程を備えることを特徴とする集積回路装置の製造方法。

(もっと読む)

IC部品を保護するためのシステムおよび方法

1つの実施の形態は、集積回路(IC)(100)の少なくとも1つの部品を保護するためのシステムを提供する。システムは、ICの端子と少なくとも1つの部品(108)との間に電気的に接続された切断要素(104)を含む。切断要素は、端子から少なくとも1つの部品に電気信号が伝搬するのを許容する第1の状態と、端子を少なくとも1つの部品から電気的に切断する高インピーダンス状態に対応する第2の状態とを有するように構成される。制御システム(110)は、少なくとも1つの予め決められた起動条件に基づいて、切断要素を第1の状態から第2の状態に遷移させるように構成される。  (もっと読む)

(もっと読む)

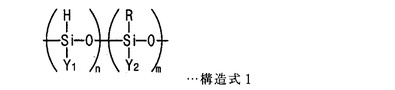

スピンオンガラス組成物、その製造方法、及びそれを用いた多孔性シリコン酸化膜の製造方法

【課題】接着特性が優秀な低誘電膜を形成するためのスピンオンガラス組成物、その製造方法、及びそれを用いた多孔性シリコン酸化膜の形成方法を提供する。

【解決手段】構造式1を有する3〜20質量%のシルセスキオキサンオリゴマー、3〜20質量%の気孔生成剤、及び残余の溶媒を含むスピンオンガラス組成物。そして、前記多孔性シリコン酸化膜を形成するために、前記スピンオンガラス組成物を基板上に塗布してスピンオンガラス薄膜を形成した後、前記薄膜を硬化して多孔性シリコン酸化膜を形成する。したがって、前記多孔性シリコン酸化膜は、接着特性が優秀であるのみならず、後続工程で過剰エッチングを招かない。 (もっと読む)

(もっと読む)

連結ノードのカップリング電圧の上昇を緩和する不揮発性半導体メモリ装置のレイアウト

【課題】カップリングによる電圧の上昇を低減させる不揮発性半導体メモリ装置のレイアウトを提供する。

【解決手段】本発明の不揮発性半導体メモリ装置のレイアウトは、左右方向に隣り合って配置される第1および第2レイアウトグループを含む。前記第1および第2レイアウトグループそれぞれは、多数のページバッファと、多数の分離素子と、多数の連結ノードと、多数のビットラインとを備える。前記特定のページバッファに対して最も遠い距離に位置する前記分離素子に対応する前記連結ノードは、最も下方に配置されるページバッファに連結される。隣接するビットラインのキャパシタンスにカップリングされる連結ノードのキャパシタンスの比を大幅増加させる。したがって、カップリングによる連結ノードの電圧の上昇を低減する。これにより、連結ノードに連結される遮断素子が破壊される危険が減少する。

(もっと読む)

メモリ素子の側壁スペーサの製造方法及び側壁スペーサを有する素子

本発明は、一般に、メモリ素子の側壁スペーサを製造する方法及びかかる側壁スペーサを有するメモリ素子に関する。一実施形態では、この方法は、第1の厚さを有する第1の側壁スペーサをメモリ素子中のワード線構造体に隣接して形成し、第1の厚さよりも大きな第2の厚さを有する第2の側壁スペーサを少なくとも1つの周辺回路中のトランジスタ構造体に隣接して形成し、第1の側壁スペーサ及び第2の側壁スペーサが、単一のスペーサ材料層を構成する材料から成るようにすることによって、メモリアレイ及び少なくとも1つの周辺回路で構成されたメモリ素子の側壁スペーサを形成する方法である。例示の一実施形態では、メモリ素子は、複数のワード線構造体で構成されたメモリアレイを有し、複数のワード線構造体の各々に隣接して第1の側壁スペーサが形成され、第1の側壁スペーサは、第1の厚さを有し、メモリ素子は、少なくとも1つのトランジスタで構成された周辺回路を更に有し、少なくとも1つのトランジスタに隣接して第2の側壁スペーサが形成され、第2の側壁スペーサは、第1の厚さよりも大きな第2の厚さを有し、第1の側壁スペーサ及び第2の側壁スペーサは、単一のスペーサ材料層を構成する材料から成る。  (もっと読む)

(もっと読む)

小さく、スペースの狭い構成物の配列を形成する方法

集積回路に用いるための、小さく高密度に間隔をあけた孔もしくは支柱の配列を形成するための方法を開示する。高密度に充填された構成物を形成するために、様々なパターン転写ステップ、および、エッチングステップを、ピッチ減少化技術と組み合わせて用いることができる。一つの層に統合することができる、交差し引き伸ばされた構成物のピッチが減少しているパターンの重ね合わせたものを形成するために、従来のフォトリソグラフィーステップをピッチ減少化技術と組み合わせて用いることができる。 (もっと読む)

記憶素子の製造方法、記憶装置の製造方法

【課題】 情報の記録及び読み出し及び書き込みにおける閾値電圧等の特性のばらつきを抑制して、適正な特性の記憶素子を製造することを可能にする記憶素子の製造方法を提供する。

【解決手段】 第1の電極2及び第2の電極5の間に記憶用薄膜4が挟まれて構成され、この記憶用薄膜4が酸化物層を含んで成り、この記憶用薄膜4内もしくは記憶用薄膜4と接している層に、Ag,Cu,Znから選ばれる、いずれかの元素が含まれている記憶素子10を製造する際に、記憶用薄膜4の界面を大気に露出させることなく、記憶素子10を構成する積層膜2,3,4,5を形成する。

(もっと読む)

記憶素子の製造方法、記憶装置の製造方法

【課題】 情報の記録及び読み出し及び書き込みにおける閾値電圧等の特性のばらつきを抑制して、適正な特性の記憶素子を製造することを可能にする記憶素子の製造方法を提供する。

【解決手段】 第1の電極1及び第2の電極4の間に記憶用薄膜2が挟まれて構成され、この記憶用薄膜2が希土類酸化物層を有して成り、この記憶用薄膜2内もしくは記憶用薄膜2と接している層3に、Ag,Cu,Znから選ばれる、いずれかの元素が含まれている記憶素子10を製造する際に、反応性スパッタ法により記憶用薄膜2を形成する。

(もっと読む)

スイッチング素子

【課題】高速動作及び3D化が可能なメカニカルスイッチを提案する。

【解決手段】本発明の例に関わるスイッチング素子は、第1入出力電極13と、第1入出力電極13に対して接触/非接触を繰り返す可動部14と、可動部14に接続される第2入出力電極15と、可動部14に絶縁層16を介して結合され、電荷が蓄積されるフローティングゲート電極17と、フローティングゲート電極17との間で静電力を発生させ、可動部14の動作を制御する第1ゲート電極FGとを備える。

(もっと読む)

異なるゲート酸化膜の厚さに関する方法および装置

パスゲートトランジスタのための向上されたオン−オフ変化を有する集積回路が、提供される。該集積回路は、コアトランジスタとパスゲートトランジスタとを含むコア領域を含む。コアトランジスタは、第1の厚さと関連付けられたゲート酸化膜を有し、パストランジスタは、第1の厚さよりも小さな厚さと関連付けられたゲート酸化膜を有する。一実施形態において、パスゲートトランジスタのゲート酸化膜のために用いられる材料は、4より大きな誘電率を有し、一方で、コアトランジスタのゲート酸化膜のために用いられる材料は、4以下の誘電率を有する。集積回路を製造するための方法も、提供される。  (もっと読む)

(もっと読む)

垂直方向のゲート電極を有する電界効果トランジスタ及びその製造方法

【課題】垂直方向のゲート電極を有する電界効果トランジスタ及びその製造方法を提供する。

【解決手段】半導体素子及びその半導体素子の製造方法において、平面型メモリ素子及び垂直に配向した薄いボディ素子が共通半導体層上に形成される。例えば、メモリ素子で、素子の周辺領域に平面型トランジスタを有し、素子のセル領域に垂直に配向した薄いボディトランジスタを有することが望ましい。これにより、素子の各形態の長所がメモリ素子のそれぞれの適当な機能に適用され得る。

(もっと読む)

半導体装置及びその製造方法

【課題】膜厚測定を簡易化出来る半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板10の第1領域に、設けられた第1の半導体層13と、半導体基板10の第2領域上に、絶縁膜11を介在して設けられた第2の半導体層12と、半導体基板10の第3領域上に、絶縁膜11及び第2の半導体層12を介在して設けられた第3の半導体層13とを備え、第3領域内の第3の半導体層13の上面の高さは第2領域内の第2の半導体層12の上面の高さよりも高いことを特徴としている。

(もっと読む)

半導体記憶回路、半導体記憶回路の構成方法、及び、半導体記憶回路のレイアウト生成方法

【課題】 システムLSIに含まれる半導体記憶回路のレイアウト面積を小さくすることによってシステムLSIをより小型化できる、半導体記憶回路及び半導体記憶回路の構成方法に関する。

【解決手段】 メモリマクロセル1は、第1及び第2のメモリセルアレイ10a及び10bとその周辺回路とを備える。周辺回路は、ロウデコーダブロック20、制御ブロック50、並びに、第1及び第2の入出力回路ブロック80a及び80bを備える。プリデコード信号配線ブロック30に形成された電源配線は、第1及び第2のロウデコーダ回路ブロックで共用される。また、制御ブロック50形成された書込パルス発生回路と遅延回路は、第1及び第2のメモリセルアレイ10a及び10bで共用される。また、制御回路ブロック70では、一つのクロック信号によってタイミング制御が行われる。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】タングステンハードマスク膜の酸化を防止することができるとともに、ビットラインキャパシタンスを減らしてビットラインスピードを向上させることができる、フラッシュメモリ素子の製造方法の提供。

【解決手段】所定の構造物が形成された半導体基板上にストップ窒化膜と酸化膜を形成する段階と、前記酸化膜とストップ窒化膜にトレンチを形成する段階と、前記トレンチの側面にALD法によってバリア酸化膜を形成する段階と、前記トレンチ内にビットラインを形成する段階とを含む、フラッシュメモリ素子の製造方法を提供する。

(もっと読む)

磁気抵抗メモリを有するシングルチップ

シングルチップは、基板と、少なくとも1つの磁気抵抗メモリ層とを有する。基板は、下地メモリ及び制御回路を有する。磁気抵抗メモリ層は、基板上に位置し、制御回路により制御された複数の磁気抵抗ランダムアクセスメモリセルを有する。 (もっと読む)

半導体装置の製造方法、製造装置、シミュレーション方法、及びシミュレータ

【課題】 半導体装置製造プロセスを、テストピースなしに、所望の工程通り又は修正しながら進行することを可能とする半導体装置の製造方法を提供すること。

【解決手段】 複数の工程からなる半導体装置の製造方法において、前記複数の工程の少なくとも1つにおける実観測データを得る工程と、abinitio分子動力学プロセスシミュレータ又は経験的ポテンシャルを与えた分子動力学ミュレータにより、前記複数の工程の少なくとも1つにおける予測データを得る工程と、前記予測データと実観測データとを逐次、実時間で比較検定する工程と、前記比較検定により、製造工程因子の設定値と、前記実観測データから推測される前記複数の製造工程因子との間に有意差が認められた場合、前記製造工程因子を逐次実時間で修正処理する工程とを具備することを特徴とする。

(もっと読む)

半導体素子の素子分離膜形成方法

【課題】素子分離膜形成工程で発生するプラズマ損傷Wを防止する半導体素子の素子分離膜形成方法を提供。

【解決手段】半導体素子の素子分離膜形成方法は、半導体基板上のパッド膜および半導体基板10の所定の深さをパターニングしてトレンチを形成する段階と、前記トレンチの側壁に側壁酸化膜18を形成する段階と、全面に第1トレンチ埋め込み用酸化膜を形成し、前記パッド膜が露出するまで平坦化工程を行い、非活性領域が定義される第1素子分離膜20を形成する段階と、前記パッド膜を除去し、活性領域を定義する前記半導体基板10を露出させる段階と、前記半導体基板10上に前記第1素子分離膜20の高さより高くシリコン層を形成する段階と、全面に第2トレンチ埋め込み用酸化膜を形成し、前記シリコン層が露出するまで平坦化工程を行って第2素子分離膜23を形成することにより、積層された素子分離膜を形成する段階とを含む。

(もっと読む)

半導体記憶装置の製造方法及び半導体設計装置

【課題】 設計の容易化、または設計期間の短縮を実現可能な半導体記憶装置の製造方法及び半導体設計装置を提供する。

【解決手段】 例えば、設計したメモリアレーを検証する際に、様々な分布を備えた各種パラメータVN(ΔVBDL),VN(ΔVTN),VN(IJ)の関数によって定式化されるメモリセルの読み出し信号量VS_EFFを用い、この読み出し信号量VS_EFFの値を各種パラメータ毎の分布からランダムに抽出した値を用いて算出し、この算出結果からメモリセルの良否判定を行い、これらの読み出し信号量VS_EFFの値の算出およびメモリセルの良否判定をメモリアレーが備える多数のメモリセルに対して行う。そして、これによって得られた不良ビットの総数などを、メモリアレーの評価基準に用いる。

(もっと読む)

半導体集積回路装置の設計方法

【課題】 メモリアレイに接続された周辺回路を構成するトランジスタにおけるゲート酸化膜の膜厚を最適化し、FNストレスによるデバイス劣化を大幅に低減する。

【解決手段】 シミュレーションによって、MGドライバのトランジスタにおけるゲート印加電圧を算出し、設定されたゲート酸化膜厚と算出したゲート印加電圧から、ゲート酸化膜印加電界を計算する(ステップS101)。算出したゲート酸化膜印加電界とゲート酸化膜厚との関係から、FN劣化発生臨界電界線以上のトランジスタがあるかを検出し(ステップS102)、FN劣化発生臨界電界以上のトランジスタがある場合には、ゲート印加電圧を再設計してゲート酸化膜印加電界を再計算し(ステップS103)、FN劣化発生臨界電界以上のトランジスタがあるか検出し(ステップS104)、FN劣化発生臨界電界以上のトランジスタがない場合には、トランジスタの設計が終了となる。

(もっと読む)

半導体装置の製造方法

【課題】ターゲット等、光学的に位置検出するための大きな面積のパターン領域での表面平坦性を向上する。

【解決手段】ウェハのスクライブ領域SRに形成されるターゲットT2領域の下層に大面積ダミーパターンDLを形成する。また、製品領域PRおよびスクライブ領域SRの素子として機能するパターン(活性領域L1,L2,L3、ゲート電極17等)のパターン間スペースが広い領域に下層の小面積ダミーパターンと上層の小面積ダミーパターンDs2を配置する。このとき、上層の小面積ダミーパターンDs2は、下層の小面積ダミーパターンに対してハーフピッチシフトさせて形成する。

(もっと読む)

101 - 120 / 134

[ Back to top ]