Fターム[5F083EP00]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423)

Fターム[5F083EP00]の下位に属するFターム

Fターム[5F083EP00]に分類される特許

61 - 80 / 134

不揮発性半導体記憶装置

【課題】 ワイヤボンドを用いてチップ積層を行う場合の課題から解放され、且つ、積層されるチップコストの低減が可能でコスト優位性のある大容量の不揮発性半導体記憶装置を提供する。

【解決手段】 1または複数の少なくともメモリアレイ11と行選択回路12と列選択回路13,14を備えるメモリアレイチップ10と、少なくとも制御回路25〜28と電圧供給回路29と入力インターフェース回路21〜23と出力インターフェース回路24を備えメモリアレイチップ10に対する制御を行う制御チップ20を積層してなり、メモリアレイチップ上の第1貫通電極T1と制御チップ上の第2貫通電極T2が、対応する同士が同位置に整合するように配置され、メモリアレイチップの第1貫通電極と制御チップの第2貫通電極の対応する同士が積層方向に積み重なって相互に電気的に接続し、メモリアレイチップと制御チップの各チップが相互に電気的に接続している。

(もっと読む)

半導体装置及びその形成方法

【課題】半導体装置及びその形成方法を提供する。

【解決手段】セルゲートパターン及び周辺ゲートパターン周辺に互いに異なる絶縁パターンをそれぞれ配置してセルゲートパターン及び周辺ゲートパターン周辺に互いに異なる熱処理負担(Heat Budget)をそれぞれ与えるための方策を提供する。そのために、セルアレイ領域及び周辺回路領域を有する半導体基板を準備する。セルアレイ領域に第1及び第2セルゲートパターンが配置される。周辺回路領域に位置して第2セルゲートパターンに隣り合う周辺ゲートパターンが形成される。第1及び第2セルゲートパターン周辺に埋め込み絶縁パターンが配置される。周辺ゲートパターンの周辺に平坦化絶縁パターンが配置される。

(もっと読む)

半導体素子の製造方法

【課題】エッチング工程時の感光膜の損傷率及びイオン不純物の浸透を防止すること。

【解決手段】半導体基板上にゲート絶縁膜パターン及びゲート電極膜パターンを形成する段階;前記ゲート電極膜パターンを含む前記半導体基板上に前記ゲートパターンの間の領域の一部を露出させる感光膜パターンを形成する段階;前記感光膜パターンの表面に前記半導体基板よりエッチング速度が遅い保護膜を形成する段階;前記保護膜及び前記感光膜パターンをエッチングマスクとして用いるエッチング工程で前記半導体基板に第1のトレンチを形成する段階;及び前記第1のトレンチが形成された前記半導体基板にイオン注入工程を行う段階を含む半導体素子の製造方法。

(もっと読む)

ビット線コンタクトプラグを形成する方法及びトランジスタ構造

【課題】ビット線コンタクト材料膜を直接にエッチングしてビット線コンタクトプラグを形成する方法を提供する。

【解決手段】方法は、ゲート構造と、基板内にありゲート構造の両側に隣接するソース/ドレインを備えるトランジスタを含む基板を設ける段階、基板の上に導電膜を形成し、導電膜の上にビット線コンタクト材料膜を形成し、ビット線コンタクト材料膜にハードマスク膜を形成する段階、導電膜をエッチングストップ膜として用い第一エッチング工程を行い、ハードマスク膜とビット線コンタクト材料膜をエッチングし、ソース/ドレインの上にビット線コンタクトプラグを形成する段階からなる。

(もっと読む)

三次元半導体デバイスの製造方法、基板生産物の製造方法、基板生産物、及び三次元半導体デバイス

【課題】金属からなる層間配線を容易に形成できる三次元半導体デバイスの製造方法、基板生産物の製造方法、基板生産物、及び三次元半導体デバイスを提供する。

【解決手段】この製造方法は、シリコン基板80の表面80aに有底の穴82を形成する穴形成工程と、犠牲材料85により穴82を埋め込む埋込工程と、集積回路層90をシリコン基板80の表面80aに形成する集積回路形成工程と、シリコン基板80の裏面80bよりシリコン基板80を薄化することにより、穴82を貫通させると共にシリコン基板80の裏面80bから犠牲材料85の一部を露出させる薄化工程と、犠牲材料85を除去して金属材料を埋め込むことにより層間配線を形成する配線形成工程と、シリコン基板80を他の基板上に積み重ね、集積回路層90の回路と他の基板上の回路とを層間配線を介して電気的に接続する積層工程とを備える。

(もっと読む)

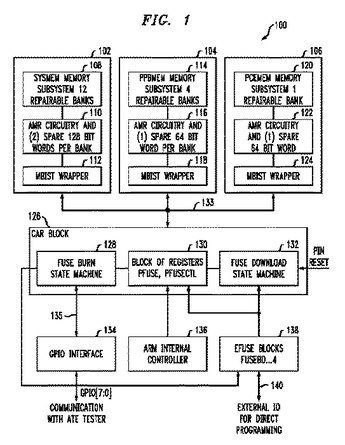

ヒューズ焼付け状態機械及びヒューズダウンロード状態機械に基づく内蔵メモリ修理方法

内蔵メモリ内の1以上の不良を修理するためのメモリ修理回路は少なくとも1つのヒューズレジスタ及び当該ヒューズレジスタに結合された状態機械回路を含む。状態機械回路は、(i)内蔵メモリ内の1以上の不良に関するステータス情報を受信し、(ii)ステータス情報に基づいてメモリが修理可能かを判断し、(iii)メモリが修理可能であるとみなされるときは、メモリの不良メモリセルに対応するアドレスを記憶し、(iv)メモリ修理回路に供給された電圧源を用いて、不良メモリセルに対応するアドレスをヒューズレジスタに焼き付け、及び(v)不良メモリセルに対応するアドレスがヒューズレジスタに焼き付けられたことを確認するように動作する第1の状態機械を実装する状態機械回路を備える。状態機械回路がさらに、(i)少なくとも1つのヒューズレジスタに記憶された情報を内蔵メモリに関連する少なくとも1つの修理レジスタにダウンロードし、及び(ii)アドレスが内蔵メモリ内の不良メモリ部分に対応する回路で受信されると、不良メモリ部分へのアクセスを少なくとも1つの修理レジスタに再ルーティングするように動作する第2の状態機械を実装する。  (もっと読む)

(もっと読む)

半導体構造の製造方法

【課題】積層メモリ・ダイを利用する半導体構造とその構造を形成する方法を提供する。

【解決手段】半導体構造は、第1の半導体ダイD1と、前記第1の半導体ダイと同一の第2の半導体ダイD2を有している。第1の半導体ダイは、第1の識別回路IDと、第1の半導体ダイの表面に、第1の複数個数の入出力パッドPIO1〜PIOnを有している。第2の半導体ダイは、第2の識別回路を有しており、第1および第2の識別回路は、互に異なるプログラムを書き込まれている。第2の半導体ダイは、また、第2の半導体ダイ表面において第2の複数個数の入出力パッドを有している。第1の複数個数の入出力パッドは、各々、垂直方向に一直線上に配列されており、各第2の複数個数の入出力パッドの1個に接続されている。第2の半導体ダイは、第1の半導体ダイに対して垂直方向に一直線上に配列され、第1の半導体ダイに固着されている。

(もっと読む)

半導体装置

【課題】STI(Shallow Trench Isolation)から受ける応力歪みによって変動するトランジスタの特性を考慮したレイアウト構造に適用して有効な、MOSトランジスタを有する半導体集積回路を提供する。

【解決手段】アレイ最外周の単位ブロック10の所定のトランジスタそれぞれが、STIの応力に応じたトランジスタサイズを有することを特徴とする。

(もっと読む)

半導体素子のコンタクトホール形成方法

【課題】既設露光装置における解像力以下のピッチを有するマスクを用いたコンタクトホール形成方法を提供する。

【解決手段】第1,第2パターンを用いたエッチング工程を行い、後工程で形成されるコンタクトホール領域である層間絶縁膜(103)の一部領域を露出させてハードマスクパターン(図6参照:111)を形成する。このハードマスクパターンを用いたエッチング工程で半導体基板(100)が露出されるコンタクトホール(112)を形成する。SOG膜による第2パターン(110)を形成すれば、例えば、60nmの解像能力を有するASML1400 ArF DRY装備を用いて30nmのピッチを有するハードマスクパターン(111)を形成できる。すなわち、高価な露光装置を装備投資する必要がなく、既存露光装備で最大2倍のピッチ縮小効果が得られる。

(もっと読む)

垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法

【課題】垂直方向のチャンネルを有するアクセス素子、これを含む半導体装置、及びアクセス素子の形成方法が開示される。

【解決手段】アクセス素子及びこれを形成する方法において、アクセス素子は、下部ソース/ドレイン領域と上部ソース/ドレイン領域を分離する垂直方向のチャンネル、チャンネル上に具備されるゲート絶縁膜、ゲート絶縁膜を横切って前記チャンネルを連結する一体型ゲート電極/連結ラインを含み、一体型ゲート電極/連結ラインはゲート絶縁膜と隣接するように具備され、下部ソース/ドレインの一部と少なくともオーバーレイされるディセンディングリップ領域を含むことができる。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】基板表面と基板上に形成された配線とで形成される段差部分にシリコン膜を形成した場合においても、メモリ素子の書き込み特性を低下させない半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】絶縁表面を有する基板10上に形成された第1の電極11と、第1の電極11の側壁部に形成されたサイドウォール絶縁層12と、第1の電極11上及びサイドウォール絶縁層12を覆って形成されたシリコン膜13と、シリコン膜13上に形成された第2の電極14と、を有し、第1の電極11又は第2の電極14は、シリコン膜13と合金化する材料で形成されているメモリ素子を複数有している。

(もっと読む)

半導体装置、半導体装置のデータ書き込み方法、及び半導体装置のデータ読み出し方法

【課題】メモリ素子に高い負荷を与えて化学反応を起こさせてデータの書き込みを行う半導体装置において、負荷をかけることによる回路素子およびメモリ素子にかかる負担を軽減し、各素子の劣化を防ぐことを課題とする。

【解決手段】メモリ部103において、直前のアドレスの記憶データが第1の負荷状態の場合には、前記入力データと同じデータを記憶データとして書き込み、直前のアドレスの記憶データが前記第1の負荷状態より高い電圧をかける第2の負荷状態の場合には、前記入力データを反転して記憶データとして書き込むよう制御する。

(もっと読む)

半導体メモリ素子の製造方法

【課題】エッチング方法を変化させてビットラインの損失を防止する半導体メモリ素子の製造方法を提供する。

【解決手段】第1の絶縁膜102上に金属配線層とエッチング停止膜112を形成する。金属配線層とエッチング停止膜112をパターニングして金属配線110を形成する。そして、第1の絶縁膜102上に第2の絶縁膜114を形成し、エッチング停止膜112が露出されるように第1のエッチングガスで第2の絶縁膜114の一部をエッチングする。続いて金属配線110が露出されるように第2のエッチングガスでエッチング停止膜112を除去する。それによって、たとえば比抵抗が低いアルミニウムを金属膜106として用い、そのアルミニウム金属膜106によるビットラインにビアホール120を連結する際、エッチングガスを変化させるだけで別途に追加膜を形成せずともアルミニウム金属膜106のエッチング損傷を抑制できる。

(もっと読む)

プロセスばらつき耐性メモリ設計

プロセスばらつき耐性メモリを設計するための方法及びシステムが開示される。メモリ回路が機能ブロックに分割される。前記機能ブロックの各々に関して統計的分布が計算される。次に、各ブロックの前記分布が結合されて前記回路の信頼性が検証される。前記信頼性は、前記回路が予め決められた歩留まりを満たす場合に検証される。 (もっと読む)

半導体記憶装置

【課題】行選択回路の小面積化と製造時の露光、エッチング等の影響を解消する半導体記憶装置を実現する。

【解決手段】アドレス入力に応じて所望のワード線を選択するように行アドレス信号と接続されたワード線選択回路と、疑似メモリセルのワード線に接続された疑似ワード線電位固定回路とを備え、疑似ワード線電位固定回路をワード線選択回路と同様にNANDゲートNANDR(i)(i=−1〜m+2)とインバータINVR(i)(i=−1〜m+2)で構成し、疑似ワード線電位固定回路の入力は疑似メモリセルのワード線を常に非選択となるように行アドレス信号と接続されている。これにより全てのワード線を選択駆動する回路の構成を同一とすることが可能となり、行選択回路の小面積化と製造時の露光、エッチング等の影響を解消することが可能となる。

(もっと読む)

メモリデバイス構造の洗浄製剤

【課題】キャッピング層及び絶縁層のマイクロ電子デバイスからの除去に関する改良された組成物を提供する。

【解決手段】シリコン含有層を、かかる層をその上に有するマイクロ電子デバイスから除去する除去組成物及び方法を開示する。除去組成物は、次のものに限定されないが、シリコン酸化物、プラズマエンハンスド・テトラエチルオルソシリケート(P−TEOS)、ボロホスホシリケートガラス(BPSG)、プラズマエンハンスド酸化物(PEOX)、高密度プラズマ酸化物(HDP)、ホスホシリケートガラス(PSG)、スピンオン誘電体(SOD)、熱酸化物、アップドープされたシリケートガラス、犠牲酸化物類、シリコン含有有機ポリマー類、シリコン含有ハイブリッド有機/無機材料類、有機シリケートガラス(OSG)、TEOS、フッ素化シリケートガラス(FSG)、半球状グレイン(HSQ)、炭素ドープされた酸化物(CDO)ガラス、及びこれらの組み合わせを含む総を、下部電極、デバイス基板、及び/又はエッチストップ層の材料に対して、選択的に除去する。

(もっと読む)

半導体素子のキャパシタ形成方法

【課題】キャパシタ内の揮発性副産物を除去して電極の伝導性を向上させ、より高い静電容量が得られる半導体素子のキャパシタ形成方法を提供する。

【解決手段】半導体基板上にストレージノード電極を形成する工程と、ストレージノード電極上に、高誘電定数を持つ誘電体膜を形成する工程と、誘電体膜上にプレート電極を蒸着する工程と、プレート電極上にキャッピング膜を蒸着しながら当該半導体基板上に水素原子(H)を含有するガスを供給して、当該電極内に残留する反応不純物を排出させる工程と、を含む構成とした。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】配線と半導体基板とを電気的に接続するコンタクトプラグを長方形に形成し、コンタクトプラグの電気的特性を向上させるフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板100の上に層間絶縁膜102と、第1,第2ハードマスク膜104,106、第1フォトレジストパターン108を順に形成する。第1フォトレジストパターンの周辺領域をシリコン含有物質層110に変換する。エッチングによりシリコン含有物質層の上部領域を除去すると同時に未変換のフォトレジストも除去しサイズとピッチの小さいシリコン含有物質層パターンを形成する。エッチングにより第2ハードマスク膜パターンを形成し、その上に一部領域が開放された第2フォトレジストパターンを形成する。エッチングにより長方形の第1ハードマスク膜パターンを形成する。これをマスクに層間絶縁膜をエッチングし、長方形のコンタクトホールを形成する。

(もっと読む)

61 - 80 / 134

[ Back to top ]