Fターム[5F083EP00]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423)

Fターム[5F083EP00]の下位に属するFターム

Fターム[5F083EP00]に分類される特許

21 - 40 / 134

昇圧回路及び半導体装置

【課題】半導体チップのチップ面積を小さくできる昇圧回路を提供する。

【解決手段】昇圧回路100は、N個(Nは2以上の自然数)の容量素子(容量素子C0〜C3)を備える。N個の容量素子のうち第K番目(1<K<N、Kは自然数)の容量素子(容量素子C2)は第(K−1)番目の容量素子(容量素子C1)によって昇圧された第(K−1)番目の昇圧電圧を受けて、第(K−1)番目の昇圧電圧を更に昇圧した第K番目の昇圧電圧を発生して第(K+1)番目の容量素子(容量素子C3)に供給し、第N番目の容量素子の一端(出力端子OUT)から第N番目の昇圧電圧を発生する。N個の容量素子の内、少なくとも1つの容量素子(容量素子C0及びC1)は他の容量素子(容量素子C2及びC3)が形成された第1のチップ(半導体チップCHIP2)とは異なる第2のチップ(半導体チップCHIP1)に形成され、第1及び第2のチップは互いに積層されている。

(もっと読む)

半導体装置、設計装置、及びプログラム

【課題】リングゲート型MOSトランジスタ間の領域だけでなく、リング内の領域においてもディッシング現象の発生を抑止する。

【解決手段】半導体装置1は、基板10と、基板10上に形成されたリング形状のゲート電極21を有するトランジスタ20bと、ゲート電極21の外側に配置され、ゲート電極21と同層に設けられる複数の外部ダミーパターン40と、ゲート電極21の内側に配置され、ゲート電極21と同層に設けられる少なくとも1つの内部ダミーパターン41とを備える。

(もっと読む)

記憶素子および記憶装置

【課題】複数の記憶素子の初期状態もしくは消去状態の抵抗値のバラツキを低減すると共に、複数回の書き込み・消去動作に対して書き込み・消去時の抵抗値を保持することが可能な記憶素子および記憶装置を提供する。

【解決手段】記憶層20に、酸化ガドリニウム(Gd−O)よりなる第1高抵抗層22Aと、酸化アルミニウム(Al−O)または酸化シリコン(Si−O)よりなる第2高抵抗層22Bとを設ける。第1高抵抗層22Aに存在する欠陥を第2高抵抗層22Bにより補完し、構造の均一性を向上させ、複数の記憶素子1の初期状態または消去状態の抵抗値のバラツキを低減する。書き込み・消去動作を繰り返し行った場合に、欠陥の増殖を抑え、複数回の書き込み・消去動作に対する抵抗値保持特性を向上させる。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置において、I/O構成の切り替えを容易とする。

【解決手段】互いに異なるチップ識別情報LIDが割り当てられた複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFとを備える。インターフェースチップIFは、外部との間で同時に入出力する単位外部データのビット数が可変であり、チップ識別情報LIDと比較するためのチップ選択情報SELを、単位外部データのビット数に応じて可変とする。これにより、I/O構成の変更に伴うページ構成の切り替えを不要とすることが可能となる。

(もっと読む)

半導体装置

【課題】アンチヒューズ素子セットAFSETに含まれるデコーダ回路の数を抑制する。

【解決手段】アンチヒューズ素子セットAFSETのビット記憶回路BMは、プログラム電圧が印加されたときに絶縁状態から導通状態へ変化する2つのアンチヒューズ素子AFを含む。この2つのアンチヒューズ素子AFの論理状態により、1ビット分のデータを表現する。2つのアンチヒューズ素子AFは、1つのデコーダ回路160により一元的に制御される。データ記録に際しては、デコーダ回路160は2つのアンチヒューズ素子AFを同時にプログラム電圧ライン16a、16bと接続することにより、2つのアンチヒューズ素子AFを同時に絶縁破壊する。

(もっと読む)

半導体装置の製造方法

【課題】被保護素子部、保護素子部及び周辺トランジスタ部を備える半導体装置において、周辺トランジスタ部のゲート絶縁膜と該ゲート絶縁膜よりも膜厚が薄い保護素子部の界面絶縁膜とを同一の工程において形成できるようにする。

【解決手段】半導体基板1の上に、被保護素子用ゲート絶縁膜2を形成し、保護素子部に形成された被保護素子用ゲート絶縁膜2の一部を除去して、開口部14を形成し、半導体基板1の上部に開口部14を通して不純物を注入して、保護素子部にダイオードを形成し、ダイオードの上部に酸化抑制材を注入して、酸化抑制層9を形成し、半導体基板1における周辺トランジスタ部の少なくとも一部とを露出し、露出した半導体基板1の上にゲート絶縁膜11を形成すると共に、酸化抑制層9の上に界面絶縁膜12を形成し、被保護素子用ゲート絶縁膜2、ゲート絶縁膜11及び界面絶縁膜12の上にゲート電極13を形成する。

(もっと読む)

積層メモリ素子

【課題】高集積化が容易な積層メモリ素子を提供する。

【解決手段】本願発明の積層メモリ素子は、基板と、基板上に互いに積層された、少なくとも1層のメモリ層をそれぞれ含む複数のメモリグループと、該複数のメモリグループのうち、複数の隣接した2つのメモリグループ間に介在する複数のXデコーダ層と、前記複数の隣接した2つのメモリグループ間に、複数のXデコーダ層と交互に介在される複数のYデコーダ層と、を具備する積層メモリ素子である。

(もっと読む)

パッケージされた集積回路装置及びその動作方法とこれを有するメモリ保存装置及び電子システム

【課題】減少した信号スキューを提供するマルチチップ・パッケージされた集積回路装置及びその動作方法を提供する。

【解決手段】本発明のパッケージされた集積回路装置は、導電性パッドを上に含む基板と、基板上に複数のチップを含むチップスタックと、1次導電性ラインと、2次導電性ラインと、を備える。1次導電性ラインは、基板上の導電性パッドと、チップスタックの複数のチップのうちの一つの上に設けられた導電性パッドとを電気的に連結する。2次導電性ラインは、チップスタック内の複数のチップのうちの一つの上に設けられた導電性パッドを、その上側にある複数のチップのうちの一つ、及び下側にある複数のチップのうちの一つの上に設けられた対応する導電性パッドに電気的に連結する。

(もっと読む)

積層メモリ素子

【課題】集積度を高めることが容易な3次元積層された多層構造メモリ素子を提供する。

【解決手段】本積層メモリ素子は、基板と、基板上に相互積層され、複数の群に分割された複数のメモリ層と、各群内のメモリ層と電気的に接続され、各群内のメモリ層の間に配された複数のインターデコーダと、複数のインターデコーダと電気的に接続され、複数のインターデコーダの間に配された少なくとも一つのプレデコーダと、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】メモリブロックを含んだ半導体装置において、高速化を実現する。

【解決手段】例えば、メモリブロックMB1内に複数のメモリアレイARY[0]〜ARY[3]が備わった構成において、ARY[0]〜ARY[3]のサイズA[0]〜A[3]が段階的に異なるように形成される。具体的には、MB1への内部制御信号(例えばクロック信号CLK)の入力パッドPD_CLKや、MB1からのデータ信号の出力パッドPD_DOからの距離が、ARY[0]<ARY[1]<ARY[2]<ARY[3]の場合、例えば、A[0]>A[1]>A[2]>A[3]となるように形成される。これによって、このパッドからの距離の違いに伴う伝送遅延時間の差分を各メモリアレイの動作遅延時間の差分で相殺することができ、MB1全体として高速化が図れる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の結晶欠陥発生を抑制することができる半導体装置の製造方法を提供する。

【解決手段】ウエハ上にSTI用のトレンチを形成し、そのトレンチに絶縁膜を埋め込む。次に、ウエハ表面に酸素を導入する。酸素導入は、酸素100%雰囲気下で、1100℃、60秒間、ウエハ表面にRTO(Rapid Thermal Oxidation)を行う。その後、高温アニールを行う。SRAM製造プロセスにおいて、転位が発生するおそれのある高温アニール工程とソース/ドレイン部のイオン注入工程の前に酸素導入を行うため、ウエハの結晶強度を高めることができ、アニール工程やイオン注入工程によって発生する転位を抑えることができる。

(もっと読む)

メモリ回路とその導電層の配線

【課題】メモリ回路のビットライン、電圧ライン、ワードラインの配線を提供する。

【解決手段】メモリ回路100のメモリアレイ100aは、データを記憶する少なくとも一つのメモリセル101aを含む。メモリセル101aは、ワードラインWL、ビットラインBL、ビットラインバー、第一電圧ライン、及び第二電圧ラインに結合される。メモリ回路100は、第一導電層、第一導電層に結合される第二導電層、及び、第二導電層に結合される第三導電層を備える。第三導電層は、ワードラインWLに対して配線され、メモリセル101a内で、ビットラインBL、ビットラインバー、第一電圧ライン、及び第二電圧ラインがない。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

半導体装置

【課題】本発明は、SOI基板を用い、1枚の基板上に実際の装置に独立して適用可能なドライバ機能を搭載した半導体装置を提供することを目的とする。

【解決手段】支持シリコン基板31の上面に酸化膜32が積層され、該酸化膜32の上面に活性シリコン層33が積層されたSOI基板30、30a、30bに形成された半導体装置50、50a〜50dであって、

前記SOI基板30、30a、30bの表面40は、前記支持シリコン基板31が露出した支持シリコン基板露出領域41と、前記活性シリコン層33が形成された活性シリコン層領域42、43とを有し、

前記支持シリコン基板露出領域41又は前記活性シリコン層領域42、43の一方には出力回路10、10a〜10eが形成され、他方には該出力回路10、10a〜10eを駆動制御する制御回路20、20a〜20dが形成されたことを特徴とする。

(もっと読む)

半導体素子及びそのセルブロック配置方法

【課題】長さの制限がなく、メモリセルブロックを密集配列させて高いパッキング密度を具現することができる半導体素子及びそのセルブロック配置方法を提供する。

【解決手段】セルアレイと、前記セルアレイの横及び縦方向に配置されたデコーダとを有する複数個の「L」字形状のセルブロックを有し、前記複数個の「L」字形状のセルブロックは、前記横及び縦方向と交差する斜線方向に指向配置されている。

(もっと読む)

半導体装置及び該半導体装置のレイアウト方法

【課題】半導体装置及び該半導体装置のレイアウト方法を提供する。

【解決手段】複数のビットラインパターンと、複数のビットラインパターンにそれぞれ連結されて形成される複数のパッドパターンと、パッドパターンに形成される少なくとも一つのコンタクトと、を備え、パッドパターンのピッチは、ビットラインパターンのピッチより長い半導体装置とする。

(もっと読む)

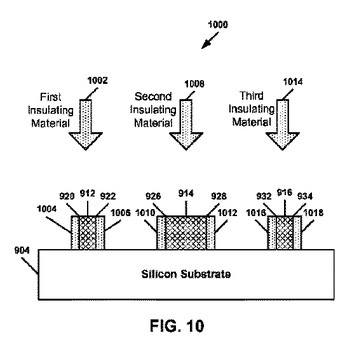

フィン電界効果トランジスタ(フィンFET)デバイスの製造方法

フィン電界効果トランジスタ(フィンFET)を用いた半導体の製造方法が開示される。特定の実施形態の方法は、第一の幅によって離隔された第一の側壁及び第二の側壁を有する第一のダミー構造体をシリコン基板上に堆積させるステップを含む。また、本方法は、第一のダミー構造体を堆積させるのと同時に第二のダミー構造体をシリコン基板上に堆積させるステップも含む。第二のダミー構造体は、第二の幅によって離隔された第三の側壁及び第四の側壁を有する。第二の幅は第一の幅よりも実質的に大きい。第一のダミー構造体を用いて略第一の幅によって離隔された第一の対のフィンを形成する。第二のダミー構造体を用いて略第二の幅によって離隔された第二の対のフィンを形成する。  (もっと読む)

(もっと読む)

半導体素子の製造方法および半導体素子

【課題】 半導体素子の微細パターン製造方法を提供する。

【解決手段】フィーチャー層310の第1領域Aには第1マスク構造物を形成し、第2領域Bには第2マスク構造物を形成する。各々デュアルマスク層とエッチングマスク層とを含むように第1マスク構造物及び第2マスク構造物を形成する。第1マスク構造物及び第2マスク構造物のエッチングマスクパターンを等方性エッチングし、第1マスク構造物からエッチングマスクパターンを除去する。第1マスク構造物及び第2マスク構造物の両側壁にスペーサ350A、350Bを形成する。第2マスク構造物上にあるエッチングマスクパターンをマスクとして第1領域Aで間にボイドが形成されるように側壁スペーサ350Aを含む第1マスクパターンと、第2領域Bで間に第2マスク構造物が介在するように側壁スペーサ350B、350Cを含む第2マスクパターンを形成する。

(もっと読む)

酸化ゲルマニウムの製造方法およびそれを用いた半導体デバイスの製造方法

【課題】熱的および化学的に安定な酸化ゲルマニウムの製造方法を提供する。

【解決手段】p型Geからなる基板1は、純水および0.1%HFによって洗浄され、その後、超純水によってリンスされる(工程(a)参照)。その後、基板1は、33%の過酸化水素水3に、60秒間、浸漬される(工程(b)参照)。これによって、酸化ゲルマニウム膜4が基板1の一主面に形成される。

(もっと読む)

21 - 40 / 134

[ Back to top ]