Fターム[5F083EP00]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423)

Fターム[5F083EP00]の下位に属するFターム

Fターム[5F083EP00]に分類される特許

81 - 100 / 134

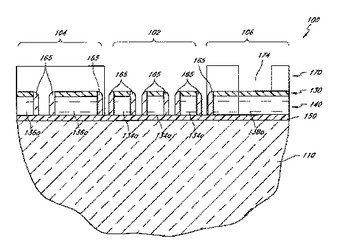

効率的なピッチマルチプリケーションプロセス

集積回路(100)の、ピッチマルチプリケーションされたフィーチャと、ピッチマルチプリケーションされていないフィーチャ、例えば、それぞれ集積回路(100)の、アレイ領域(102)、インターフェース領域(104)、および周辺領域(106)内のフィーチャが、マスクを通して基板(110)を処理することによって形成される。マスクは、フォトレジスト層をパターニングすることによって形成され、これは同時に、それぞれ集積回路(100)のアレイ領域(102)、インターフェース領域(104)、および周辺領域(106)内のフィーチャに対応するマスク要素を画定する。パターンは非晶質炭素層(140)に転写される。側壁スペーサー(165)が、パターニングされた非晶質炭素層(140)の側壁に形成される。保護材料の層(170)が堆積され、その後パターニングされ、アレイ領域(102)内、およびインターフェース領域(104)もしくは周辺領域(106)の選択部分内のマスク要素を露出する。アレイ領域内の非晶質炭素、もしくは他の露出された部分は除去され、その結果、アレイ領域(102)内にピッチマルチプリケーションされた自立スペーサー(165)を含むパターンを残す。保護材料(170)は除去され、アレイ領域(102)内のピッチマルチプリケーションされたスペーサーと、インターフェース領域(104)および周辺領域(106)内のピッチマルチプリケーションされていないマスク要素のパターンを残す。パターンはハードマスク層(150)に転写され、それを通して下にある基板(110)がエッチングされる。  (もっと読む)

(もっと読む)

半導体装置

【課題】メモリーにおいて波長以下の線幅を有する微細なワード線やデータ線をパターニングする際、メモリーアレーとサブワードドライバやセンスアンプの境界部において、パターン端部で生ずる回折光が干渉するためワード線やデータ線端がショートしたり、断線を起こす問題を解決するパターン形成方法を提供する。

【解決手段】ワード線やデーター線をパターニングするためのマスクパターン(a)において、終端部の隣り合うワード線WL1、WL2、WL5、WL6の長さを変えて先端をずらし、さらにワード線端WL1、WL2、WL5,WL6を斜めに角を落とす。レジストパターン内の分離やパターン同士の接触を防止することができ、パターニングする配線の断線や、配線間のショートを防止することができる。

(もっと読む)

半導体集積回路装置および不揮発性メモリ装置

【課題】 不揮発性メモリ装置にデータを電気的に書き込むときに、半導体集積回路基板には高電圧が印加されないようにする。

【解決手段】 1つの配線基板(51)上に、第1の電圧で電気的にデータを書込み可能な不揮発性メモリ装置(15B)と、第1の電圧よりも低い第2の電圧で動作する半導体集積回路基板(10E)とが搭載された半導体集積回路装置(20E)において、不揮発性メモリ装置は、第1の電圧が供給される第1の端子(15−3)と第2の電圧を出力する第2の端子(15−4)とを持ち、半導体集積回路基板(10E)は、第2の端子と電気的に接続された第3の端子(RES#)を持つ。不揮発性メモリ装置(15B)は、第1の端子と第2の端子との間に設けられて、第1の電圧を第2の電圧に変換する電圧変換回路を有する。不揮発性メモリ装置(15B)は、半導体集積回路基板(10E)上に積層されている。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】コンタクトホールのサイズの安定した減少を実現でき、素子の信頼性を向上させるフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板101上に層間絶縁膜105とハードマスク膜パターン106aを形成し、それらの表面を覆うようにしてスペーサ膜109を形成する。第1のエッチング工程で層間絶縁膜105にコンタクトホール(図4中の符号200)を形成し、スペーサ膜109も第1のエッチング工程にて除去し、ハードマスク膜パターン106aを除去するための第2のエッチング工程を実施する。それにより、コンタクトホールのサイズを減少させる必要がある場合、あるいは隣り合うコンタクトホールどうしの間隔スペースを減少させる必要がある工程にあって、リソグラフィ工程の限界を克服しつつ、コンタクトホールのサイズを安定して減少させ、ブリッジの発生を抑えて素子の信頼性を高める。

(もっと読む)

不揮発性メモリ構造

【課題】機能異常のビット線とセンス増幅器の間を開路にして、不揮発性メモリアレイのテスト工程を簡便化し得る新規の不揮発性メモリアレイ構造を提供する。

【解決手段】N本のビット線と、M本第1ワード線と、M×N個の第1記憶セルと、第2ワード線と、N個の第2記憶セルと、センス増幅器と、N個の第1トランジスタと、N個の第2トランジスタと、エネイブル線と、を包含する。その中で、MとNは自然数であって、第2記憶セルと、第1トランジスタは、対応するビット線とセンス増幅器の間が開路であるか否かを制御し、第2トランジスタとエネイブル線とは、不揮発性メモリアレイのテスト結果を書き込む。

(もっと読む)

半導体集積回路装置の検査装置

【課題】半導体集積回路装置の静的消費電流テストや複数の機能回路の電気的特性を複数の半導体集積回路装置で同時に行っても、半導体集積回路装置個々の静的消費電流特性や複数の機能回路の電気的特性を高い精度で測定可能とする。

【解決手段】電源電圧発生器(301A-301D)は、同時に検査される複数の半導体集積回路装置(1A-1D)に対応して設けられ、半導体集積回路装置毎に、半導体集積回路装置を夫々動作させるための電源電圧を発生する。制御回路(CPU)は、複数の半導体集積回路装置を同時に検査するため、夫々の半導体集積回路装置に対応して独立に設けられている。判定器(JUDGE)は、複数の半導体集積回路装置に夫々対応して設けられ、夫々の前記半導体集積回路装置の電気的特性の許容範囲を判定する。制御回路(CPU)は、複数の半導体集積回路装置の検査を独立に制御して同時に検査する。

(もっと読む)

フラッシュメモリのためのパッシベーション構造およびその製造方法

【課題】下に横たわる装置構成要素を効果的に保護するばかりでなく、従来的パッシベーション構造の形成方法よりも迅速かつ低廉に製造されるパッシベーション構造が必要である。

【解決手段】本発明によるパッシベーション構造は、最小限の層の数を用いて強化されたパッシベーション効果を供する高紫外線透過性珪素(UV−SiN)層を有する半導体装置のためのパッシベーション構造である。このUV−SiN層は実質的に形状に追随して、半導体基板の上に形成された複数の上部金属線上に横たわり、隣接する上部金属線の間に、形状的窪みが明確に示される。スピンオンガラス(SOG)材料が該形状的窪みに埋められる。比較的厚く、上面が実質的に平坦な酸窒化珪素層は、下に横たわる形態を水分から保護するのみならず、アルカリ金属イオンがそこを通ることを防ぐ。酸窒化珪素層は、続く湿潤エッチング処理の間、SOG材料を保護する。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】四角形のドレインコンタクトホールを形成することにより、コンタクトとコンタクトとの間に発生するブリッジの発生を抑制できるフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板にエッチング防止膜102、第1及び第2層間絶縁膜104,106、第1、第2及び第3ハードマスク膜108,110,112を順次形成する。第3ハードマスク膜をエッチングして第2ハードマスク膜の一部領域を露出し、この露出領域よりさらに狭く露出するフォトレジストパターンを形成し、これをマスクとして第2、第1ハードマスク膜をエッチングした後、残留する第3及び第2ハードマスク膜をマスクとして第2、第1層間絶縁膜をエッチングして四角形のホールを形成する。残留する第2及び第1ハードマスク膜をマスクとしてエッチング防止膜をエッチングし、基板を露出させてドレインコンタクトホールを形成する。

(もっと読む)

サラウンディングゲートを有するナノワイヤ・トランジスタ

本主題の態様のひとつは、トランジスタの形成方法に関する。本方法の或る実施形態では、結晶質基板上に、非晶質半導体材料でつくった柱をつくり、固相エピタキシー工程を施して、結晶質基板を結晶成長の種として使い、非晶質半導体材料を結晶化する。この柱の厚さは、リソグラフィ基準寸法以下となっている。トランジスタボディを、結晶化した半導体柱内の第一のソース/ドレイン領域と第二のソース/ドレイン領域の間につくる。サラウンディングゲート絶縁体を半導体柱の周りにつくってから、サラウンディングゲートを半導体柱の周りにそのサラウンディングゲート絶縁体を間に挟んでつくる。他の態様についても本明細書に開示してある。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】

デコーダ部の両側にそれぞれのワード線に対応したドライバを設けることは困難となってきていた。

【解決手段】

半導体記憶装置は、行デコーダ部と、前記行デコーダ部の一方に配置された第1のセルアレイと、前記行デコーダ部の他方に配置された第2のセルアレイと、前記行デコーダ部上に配置され、前記第1のセルアレイの所定の行アドレスに対応するワード線と前記第2のセルアレイの前記所定の行アドレスに対応するワード線を短絡する配線層とを有する。

(もっと読む)

露光方法及びデバイス製造方法

【課題】密集度の高いホールアレイの作製を可能にする。

【解決手段】 クロスポール照明条件下で所定のパターンが形成されたマスクRを照明し、該マスクから射出される光ILで投影光学系PLを介してウエハWを露光し、そのウエハ上にホールアレイを形成する。このため、ホールアレイパターンに対しても、L/Sパターンと同じk1ファクタの限界解像が適用可能となり、これにより、より密集度の高いホールアレイの作製が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】金属不純物捕獲能力の向上を図ることができ、且つ、素子分離構造のエッチングによる形状変化(片落ち)を抑制する。

【解決手段】シリコン酸化膜よりなる素子分離構造2が形成されたシリコン基板1上に、熱燐酸によりウェットエッチングに対するエッチング選択比が素子分離構造2に比較して高いシリコン窒化膜3を金属不純物捕獲膜として形成する。イオン注入後、熱燐酸によりウェットエッチングによりシリコン窒化膜3を除去する。

(もっと読む)

電子機器

【課題】ノイズ除去用素子以外の手段により、基板内のグランドの安定性を図る電子機器を得る。

【解決手段】CCDセンサ22から放出されるノイズは、CCDセンサ22のグランド端子22AからCCD基板16のグランド層16A、板バネ31、32、ヒートシンク24、及び、CCDブラケット20を経てフレーム12のフレームグランド14に至る。ここで、板バネ31、32は、CCDセンサ22のグランド端子22Aに近接して配置されるので、ノイズを効果的に除去できる。

(もっと読む)

半導体集積回路装置

【課題】 従来の半導体集積回路装置は、コア領域の一辺に対して最大数のI/Oユニットを配置するようにしていたため、例えば、配置すべきI/Oの数が少ない場合には、I/O領域に無駄な空きが生じて占有面積が増大することになっていた。

【解決手段】 コア領域11に接続された複数の第1のパッド23および複数の第2のパッド24を備える半導体集積回路装置1aであって、前記コア領域11の少なくとも一辺に設けられる前記各第1のパッド23および前記各第2のパッド24を、それぞれ当該一辺の長さ方向に並べて配置するように構成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート電極の中心に対して対称なMOS電界効果トランジスタの耐圧を劣化させず微細化を可能にするトランジスタ及びその製造方法を提供する。

【解決手段】ゲート電極103と対称的にゲートオーバーラップ構造の電界緩和層107A、107Bとパンチスルーストッパー層108を有するMOS電界効果トランジスタにおいて、N型パンチスルーストッパー層108の表面に、このパンチスルーストッパー層108とは反対導電型のP型層110を設け、しきい値電圧が上昇しないようにしたもの。

(もっと読む)

半導体集積回路装置

【課題】 2以上の半導体チップの高密度に実装することにより、スタックド構造のパッケージを大幅に小型化する。

【解決手段】 半導体集積回路装置1は、プリント配線基板2に半導体チップ3〜6がそれぞれ積層されたスタックド構造となっている。最下部に搭載されている半導体チップ3には、インタフェース回路7が設けられている。このインタフェース回路7は、バッファ、および静電保護回路などからなる。半導体チップ3〜6に入出力される信号は、すべて半導体チップ3のインタフェース回路7を介して入出力されることになる。これにより、半導体チップ4〜6にインタフェース回路が不要となり、半導体集積回路装置1を小型化することができる。

(もっと読む)

埋め込みFeRAM基盤のRFIDを有する集積回路

集積回路(IC)100は、予め定められた動作を行うように構成された高静電容量固体回路領域、データを格納するFeRAMブロック104、及びICを無線で識別する外部的に提供された固有IDをRFIDブロックに伝達するように構成されたインタフェースユニットを備え、固有IDは、FeRAMブロックに格納される。ICは、ICの予め定められた領域を通して延長される導電性トレースを更に備え、導電性トレースは、RFIDブロックに対するアンテナとして構成され、ここで、RFIDブロックは、情報を受信し、アンテナを介して外部ソースに情報を伝達するように構成される。  (もっと読む)

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 チップ接合後においても不良セルの救済が可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】 本発明に係る半導体記憶装置1は、スペアメモリセルを有するメモリICチップ10と、このメモリICチップ10が電気的接合部2を介して接続されているロジックICチップ20と、不良メモリセルからスペアメモリセルの選択動作を切り替える切替用素子部とを備えている。本発明では、スペアメモリセルの選択動作を切り替える切替用素子部を、ロジックICチップ20上であってメモリICチップ10との接続領域外方の切替用素子部形成領域24に配置しているので、メモリICチップ10の接合後においてもロジックICチップ20上の切替用素子部の処理あるいは操作を行うことで、不良セルの救済が可能となる。

(もっと読む)

フラッシュメモリ素子およびその製造方法

【課題】半導体素子の信頼性を向上させ、かつ集積度を向上させるフラッシュメモリ素子およびその製造方法を提供する。

【解決手段】メモリセル領域Aとペリ領域Cとの境界部分にゲートライン12が通るか否かによって、ゲートライン12が通る場合には、その境界部分を素子分離膜11aで構成し、ゲートライン12が通らない場合には、ダミーアクティブ(dummy active)で構成することにより素子の信頼性を改善し、ウェルピックアップ(well pick up)領域を上記ダミーアクティブ内に構成することで集積度を向上させる。

(もっと読む)

半導体技術における微細ピッチの製造方法

【課題】従来よりも小さいピッチを有した半導体デバイスにおいて周期パターンの製造方法を提供する。

【解決手段】周期的構造を有するパターン層の細片様構造の側壁にスペーサ5が形成される。そして、該パターン層が除去され、該スペーサが、第2の側壁スペーサとなる別のスペーサ層7によって覆われる。上記スペーサとスペーサとの間は補充層8によって充填される。上記第1のスペーサ5と、第2のスペーサ7と、上記補充層の残留部分8とが周期的に連続している部分を残して、表面を平坦化する。横寸法は、1つ以上の残留層を除去することによってピッチの小さい周期パターンが形成されるように調節される。

(もっと読む)

81 - 100 / 134

[ Back to top ]