Fターム[5F083GA10]の内容

Fターム[5F083GA10]に分類される特許

81 - 100 / 1,175

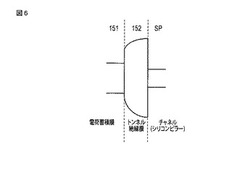

不揮発性半導体記憶装置

【課題】円筒型MONOSメモリセルで電荷保持特性の向上を図る。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に形成され、上面から下面まで達する円筒状の貫通ホールを有するコントロールゲートCGと、前記貫通ホール内における前記コントロールゲートの側面上に形成されたブロック絶縁膜150と、前記貫通ホール内における前記ブロック絶縁膜の側面上に形成された電荷蓄積膜151と、前記貫通ホール内における前記電荷蓄積膜の側面上に形成されたトンネル絶縁膜152と、前記貫通ホール内における前記トンネル絶縁膜の側面上に形成された半導体層SPと、を具備し、前記トンネル絶縁膜は、SiO2を母材とし、添加することで前記母材のバンドギャップを低下させる元素を含む第1絶縁膜を含み、前記元素の濃度および濃度勾配は、前記半導体層側から前記電荷蓄積膜側に向かって単調に増加する。

(もっと読む)

半導体記憶装置の製造方法

【課題】スループットの向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板上に、不純物濃度が第1濃度である第1シリコン層35、不純物濃度が第1濃度より低い第2濃度である第1犠牲層、不純物濃度が第1濃度である第2シリコン層35、および不純物濃度が第2濃度である第2犠牲層が順に積層された積層体を形成する工程と、積層体上に、第1絶縁膜を形成する工程と、積層体および第1絶縁膜内に、溝22を形成する工程と、溝内に、不純物濃度が第1濃度より低く、第2濃度より高い第3濃度である第3犠牲層90を埋め込む工程と、ウェットエッチングにより、溝内の第3犠牲層を上面から後退させて除去することで、第1犠牲層および第2犠牲層の端面を後退させる工程と、第1シリコン層および第2シリコン層の端面を第1犠牲層および第2犠牲層の端面に沿ってエッチングする工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】低コスト化を図ることができる半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上にボロンを含む膜を形成する工程と、前記ボロンを含む膜上に酸化シリコンを含む膜を形成する工程と、前記酸化シリコンを含む膜をパターニングする工程と、前記パターニングされた前記酸化シリコンを含む膜をマスクとして、前記ボロンを含む膜を、塩素を含むガスを用いてエッチングする工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

不揮発性半導体記憶装置

【課題】小型化が可能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、基板と、メモリ部と、非メモリ部と、を備える。メモリ部は、基板上に設けられる。非メモリ部は、基板上に設けられ基板の主面に対して平行な面内でメモリ部と並ぶ。メモリ部は、積層体と、半導体層と、メモリ膜と、導電膜と、を含む。積層体は、主面に対して垂直な第1軸に沿って積層された複数の電極膜と、第1軸に沿って隣り合う2つの電極膜の間に設けられた電極間絶縁膜と、を含む。半導体層は、複数の電極膜の側面に対向する。メモリ膜は、複数の電極膜と半導体層との間に設けられる。導電膜は、積層体の上に設けられ、積層体と離間している。非メモリ部は、導電膜と同層の抵抗素子部を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】カップリング比の増大と書き込み/消去時のリーク電流の低減とを実現する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、半導体層11と、半導体層11上の第1の絶縁層13と、第1の絶縁層13上の電荷蓄積層14と、電荷蓄積層14上の第2の絶縁層15と、第2の絶縁層15上の制御ゲート電極16とを備える。第2の絶縁層15は、電荷蓄積層14側から制御ゲート電極16側に向かって、第1のランタンアルミネート層LAO、ランタンアルミシリケート層LASO及び第2のランタンアルミネート層LAOを備える。

(もっと読む)

半導体記憶装置

【課題】十分な消去速度が得られる半導体記憶装置を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上にそれぞれ交互に積層された複数の電極層と複数の第1の絶縁層とを有する第1の積層体と、前記第1の積層体上に設けられ、選択ゲートとその上に設けられた第2の絶縁層とを有する第2の積層体と、前記第1の積層体を積層方向に貫通して形成された第1のホールの側壁に設けられたメモリ膜と、前記第1のホールと連通し、前記第2の積層体を積層方向に貫通して形成された第2のホールの側壁に設けられたゲート絶縁膜と、前記メモリ膜の内側および前記ゲート絶縁膜の内側に設けられたチャネルボディと、を備えている。そして、前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成され、前記チャネルボディの前記選択ゲートの上端近傍に位置する領域は、シリサイド化されている。

(もっと読む)

半導体記憶装置

【課題】データ保持特性に対する信頼性を回復させることができる半導体記憶装置を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体と、前記積層体を貫く半導体ピラーと、前記電極膜と前記半導体ピラーとの間に設けられた電荷蓄積層と、前記電荷蓄積層と前記半導体ピラーとの間に設けられたトンネル層と、前記積層体の積層方向に対して直交する一の方向において、前記半導体ピラー同士の間に設けられた前記電極膜を分離する分離溝と、前記分離溝の内部に設けられた加熱部と、を備えている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

分子メモリ装置の製造方法

【課題】LSIプロセスによって製造可能な分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、前記第1配線層上に犠牲膜を形成する工程と、前記第1配線層上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料によって形成された複数本の芯材を形成する工程と、前記芯材の側面上に第2配線を形成する工程と、前記犠牲膜における前記第2配線の直下域に相当する部分を除去する工程と、前記第1配線と前記第2配線との間に、メモリ材料となる高分子を埋め込む工程と、前記芯材間であって前記第2配線間の空間に絶縁部材を埋め込む工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】TSV構造を採用し複数のチップをスタックした半導体装置を、改良された入出力形式で提供できるようにする。

【解決手段】複数のチップをスタックしてなり、隣り合うチップ間の接続を、貫通電極を介して行なうTSV構造を持つ半導体装置に適用される。各チップは複数のチャンネルに対応した複数のTSVアレイ部を備え、該複数のTSVアレイ部は、スタックするチップの数に応じて入出力に寄与するTSVアレイ部と入出力回路に接続されないパススルーのTSVアレイ部とに分けられている。スタックするチップの数に応じて2段目以降のチップを面方向に回転させてスタックし、前記パススルーのTSVアレイ部を経由してデータの入出力を行なう構成とすることにより、前記データの入出力に寄与するTSVアレイ部にのみ共有の入出力回路を備える構成とし、入出力回路の数を低減させた。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

三次元集積回路を作製する方法

【課題】集積回路を作製する新規なタイプの方法を提供する。

【解決手段】少なくとも第3の層がその間に配置された、少なくとも半導体の第1および第2の層を備える基板を作製するステップと、少なくとも第1のMOSデバイスを作製するステップであって、その活性領域が半導体の第1の層の少なくとも一部に形成される、ステップと、少なくとも第2のMOSデバイスを作製するステップであって、その活性領域が半導体の第2の層の少なくとも一部に形成され、第2のMOSデバイスの活性領域が第2のMOSデバイスのゲートと第1のMOSデバイスの活性領域との間に配置される、ステップとを少なくとも含む、集積電子回路を作製する方法。

(もっと読む)

相変化メモリ

【課題】三次元構造を有する相変化メモリの熱ディスターブを抑制する。

【解決手段】三次元構造を有する相変化メモリにおいて、選択用MOSトランジスタのゲート絶縁膜として、高い熱伝導率を有する材料を使用し、相変化記録膜からSiチャネル層に伝達する熱を良好にゲート電極に拡散させる。これにより、記録ビットから発生する熱が非選択の隣接ビットに拡散し、隣接ビットのデータを消去する熱ディスターブを抑制する。高い熱伝導率を有するゲート絶縁膜材料としては、BN、Al2O3、AlN、TiO2、Si3N4、ZnOなどを挙げることができる。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

半導体装置

【課題】消費電力の低減と干渉の抑制を実現できる半導体装置を提供する。

【解決手段】半導体装置は、直列に多段接続された第1及び第2のチップと制御チップとを備える。第1及び第2のチップのそれぞれの転送制御部は、識別信号が制御チップから供給されると当該識別信号後段のチップへ伝送し、制御チップが供給するクロック信号のn番目のパルスに基づいて、識別信号が表す識別情報を第2の記憶領域に書き込み、書き込みが終了するまでクロック信号の後段のチップへの伝送を阻止する。制御チップは、コマンドによって第1及び第2のチップを排他的にアクセスし、第1及び第2のチップのスイッチ制御回路は、コマンド及び識別情報に応じてそれぞれ対応する第1のスイッチ回路を互いに排他的に制御する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】この不揮発性半導体記憶装置において、メモリストリングスは、基板に対して垂直方向に延びる一対の柱状部、及び前記一対の柱状部の下部を連結させるように形成された連結部を有する半導体層と、前記柱状部の側面を取り囲むように形成された電荷蓄積層と、前記柱状部の側面及び前記電荷蓄積層を含む第1の絶縁膜と、前記柱状部の側面及び前記第1の絶縁膜を覆うように形成された第1導電層と、前記連結部の周囲に形成される第2の絶縁膜と、前記連結部に前記ゲート絶縁膜を介して形成される第2導電層とを備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】生産性の高い不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態は、基板の主面に対して垂直な第1軸に沿って積層された複数の電極膜と、複数の電極膜を第1軸に沿って貫通する複数の半導体層と、複数の電極膜と半導体層との間に設けられたメモリ膜と、を含む不揮発性半導体記憶装置の製造方法であって、複数の電極膜となる複数の第1膜と複数の第2膜とを交互に積層して、第1積層体を形成する工程と、第1軸に沿い複数の第1膜を支持する支持部を形成する工程と、第1積層体を第1軸に沿って貫通する第1の孔を形成し、第1の孔を介して第2膜を除去し、複数の第1膜どうしの間に間隙が形成された第2積層体を形成する工程と、第2積層体の複数の第1膜を第1軸に沿って貫通する貫通孔を形成する工程と、複数の貫通孔の中に、メモリ膜及び半導体層を埋め込む工程と、を備える。

(もっと読む)

81 - 100 / 1,175

[ Back to top ]