Fターム[5F083JA03]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564)

Fターム[5F083JA03]の下位に属するFターム

シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA03]に分類される特許

161 - 180 / 619

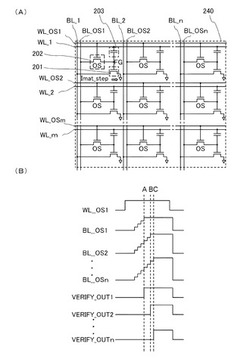

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体装置及びその製造方法、並びに吸着サイト・ブロッキング原子層堆積法

【課題】キャパシタの誘電体膜において、リーク特性改善のためのAlドープ層を設けても、誘電体膜がAlドープ層で分断されず、サイズ効果の影響を抑え、結晶性の良好な誘電体膜を提供する。

【解決手段】誘電体膜中に少なくとも1層のAlドープ層を有し、Alドープ層の1層におけるAl原子の面密度を1.4E+14[atoms/cm2]未満とする。また、その面密度を達成するため、通常のALDによる誘電体膜成膜と、Alソースの吸着サイトを制限するブロッカー分子の吸着を行った後、Alソースを吸着させ、反応ガスを導入して反応させる吸着サイト・ブロッキングALD法によるAl添加の組み合わせを採用する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】酸化膜の窒化速度を向上させる。

【解決手段】ガス流量制御部により処理ガス中の水素含有ガスと窒素含有ガスとの流量をそれぞれ調整し、処理ガス中に含まれる水素原子の数と窒素原子の数との総数に対する水素原子の数の比率Rを0%<R≦80%とする工程と、ガス供給部により処理ガスを処理室内に供給する工程と、プラズマ生成部により励起した処理ガスで酸化膜が形成された基板を処理する工程と、を有する。

(もっと読む)

不揮発性半導体記憶装置およびその制御方法

【課題】高速で高信頼動作できるようにした不揮発性半導体記憶装置およびその制御方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1のメモリセル、および、前記第1のメモリセルに対し第1方向に隣接して配置された第2のメモリセルを備えたセル群と、書込回路とを備え、第1および第2のメモリセルの一方をデータ記憶保持に、他方を一方の閾値調整に用い、書込回路が、セル群の前記第1のメモリセルにデータを書込むときには、セル群の第2のメモリセルに電圧を印加し、セル群の第1のメモリセルの閾値電圧を所望の第1閾値電圧より高く調整する。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化が進展しても読み出し動作時の電流を維持する。

【解決手段】複数のメモリサブブロックの各々は、第1ノードと第2ノードとの間に並列接続された複数のメモリトランジスタを含む。メモリサブブロックは、第1導電層と、第2導電層と、半導体層と、第3導電層とを備える。第1導電層は、層間絶縁膜を貫通して半導体基板に対し垂直な第1方向に延びるように形成され第1ノードとして機能する。第2導電層は、層間絶縁膜を貫通して半導体基板に対し第1方向に延びるように形成され第2ノードとして機能する。半導体層は、第1導電層と第2導電層とを接続するように半導体基板と平行な第2方向に延びるように形成されメモリトランジスタのチャネル層として機能する。第3導電層は、半導体層上にゲート絶縁膜を介して形成される。ゲート絶縁膜は、電荷蓄積膜を一部に含み第3導電層を囲う閉ループ状に形成される。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置を構成する回路を高集積度化する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、半導体基板と複数のメモリセルトランジスタを有する。前記複数のメモリセルトランジスタは、前記半導体基板に設けられた深溝にトレンチゲートが埋設され、直列接続される。メモリセルの書き込み動作及び読み出し動作のとき、トレンチゲートの周囲及び間の前記半導体基板の領域に、前記半導体基板とは逆導電型の反転層が形成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、電極膜及び絶縁膜が交互に積層され、端部の形状が前記電極膜毎にステップが設けられた階段状である積層体と、前記端部の上方から前記電極膜に接続されたコンタクトと、前記積層体の前記端部以外の部分に設けられ、前記積層体を積層方向に貫く半導体部材と、前記電極膜と前記半導体部材との間に設けられた電荷蓄積層と、前記端部を前記積層方向に貫く貫通部材と、を備える。そして、前記貫通部材には、前記電荷蓄積層を形成する材料と同種の材料が含まれていない。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 セル部のブロック絶縁膜の誘電率を低下させることなく、セル部のブロック絶縁膜を分断するセル間における絶縁膜中の欠陥を低減し、電荷保持特性の劣化を抑制する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態の不揮発性半導体記憶装置においては、半導体基板上にトンネル絶縁膜、前記トンネル絶縁膜上に電荷蓄積層、前記電荷蓄積層上にブロック絶縁膜が設けられる。前記半導体基板に設けられた素子分離溝部に埋め込まれ、底面が前記半導体基板と前記トンネル絶縁膜の接する面の高さよりも低く、かつ上面が前記電荷蓄積層および前記ブロック絶縁膜の接する面の高さよりも低い第1の素子分離絶縁膜が設けられる。前記第1の素子分離絶縁膜上に形成され、前記ブロック絶縁膜の側面と接して前記ブロック絶縁膜上面まで突出し、かつSi濃度が前記ブロック絶縁膜よりも高い第2の素子分離絶縁膜が設けられる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択トランジスタのカットオフ特性を維持しつつ、オフセット特性の悪化を抑制する。

【解決手段】半導体基板の表層部を活性領域に分離する素子分離絶縁膜と、前記半導体基板の活性領域上のゲート絶縁膜上に形成され第1の導電層、電極間絶縁膜および第2の導電層を有するメモリゲート電極および前記メモリゲート電極の両脇に位置する前記活性領域に形成された第1のソース/ドレイン領域を備えたメモリセルトランジスタと、前記メモリセルトランジスタに隣接して配置され、前記第1のゲート絶縁膜上に導電層を積層した選択ゲート電極および前記選択ゲート電極の両脇に位置する前記活性領域に形成された第2のソース/ドレイン領域を備えた選択ゲートトランジスタとを有し、前記活性領域に形成される少なくとも前記第2のソース/ドレイン領域は、前記活性領域の表層部が掘り下げられた凹部に設けられていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、溝内に残存する導電膜の高さばらつきを小さくすることで、半導体装置の特性のばらつきを低減可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】半導体基板13をエッチングして、幅W1とされた第1の溝部51を形成し、その後、第1の溝部51の下方に位置する半導体基板13をエッチングして、幅W1よりも狭い幅W2とされた第2の溝部52を形成することで、第1の溝部51、第2の溝部52、及び第1の溝部51の底面及び第2の溝部52の側面よりなる対向する一対の段差部54を有したビット線形成用溝を形成し、次いで、ビット線形成用溝15の内面を覆う絶縁膜16を介して、第2の溝部52を埋め込み、かつ第1の溝部51を埋め込まない厚さとされた第1の導電膜56を成膜し、その後、第1の導電膜56をエッチバックすることで、第2の溝部52の一部に第1の導電膜56を残存させる。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド層の成長に起因するゲート電極と半導体基板との間のショートの発生を抑制した上で、シリサイド層を厚く形成可能な半導体装置の製造方法を提供する。

【解決手段】ピラー26の側面にゲート絶縁膜27を介して、ゲート電極51、52を形成し、ピラー26の上端に上部不純物拡散領域36を形成し、上部不純物拡散領域36上に形成された層間絶縁膜39、68を貫通し、かつ上部不純物拡散領域36の上面を露出するシリンダ孔71を形成し、シリンダ孔71の底部に、上部不純物拡散領域36の上面を覆うと共に、シリンダ孔71の一部を埋め込むシリコン膜42を形成し、シリコン膜42の上面、シリコン膜42よりも上方に位置するシリンダ孔71の内面を覆うように下部電極57を形成すると共に、下部電極57を形成する際の熱により、シリコン膜42に含まれるSiと下部電極57に含まれる金属とを反応させてシリサイド層43を形成する。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼できる非常に小型の記憶素子を含む、3次元集積回路メモリ用の構造を低い製造コストで提供すること。

【解決手段】3次元メモリデバイスは、絶縁材料によって分離され、復号化回路を介してセンスアンプに結合可能なストリングとして配置された複数の隆起した形状スタック含む。ダイオードは、ストリングのストリング選択端部又は共通ソース選択端部のどちらか一方においてビット線構造に接続される。導電材料の帯片は、隆起した形状のスタックのサイドに側面を有する。ワード線として配列された複数の導電線は、行デコーダに結合することができ、複数の隆起した形状のスタックの上で直交して延びる。記憶素子は、スタック上の電導性帯片の側面と導電線との間の交点における界面領域の多層アレイに設けられる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、且つ書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば酸化物半導体材料を用いて半導体装置を構成する。また半導体装置の各メモリセルの酸化物半導体材料を用いたトランジスタを直列に接続する。更に、第j(jは2以上m以下の自然数)のメモリセルの容量素子の端子の一方に電気的に接続される配線と、第(j−1)のメモリセルのチャネルが酸化物半導体層に形成されたトランジスタのゲート端子に電気的に接続される配線と、を同じ配線(第jのワード線)とする。これによってメモリセルあたりの配線の数を減らし、メモリセルあたりの占有面積を低減する。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体集積回路

【課題】 不揮発記憶保持用途の電界効果トランジスタと、論理演算用途の電界効果トランジスタの製造工程を別々に設けることなく前記2用途の電界効果トランジスタを同一半導体基板上に同一構造に作製できるようにする。

【解決手段】 ゲート絶縁構造体12に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタで半導体集積回路のメモリ回路とロジック回路の両方を構成し、ゲート絶縁構造体に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタのゲート-基板領域間に印加する電圧の大きさと印加タイミングを制御することによって、論理演算状態と記憶書込み状態と不揮発記憶保持状態を電気的に切り替える。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】本発明の実施形態は、歩留まりを向上させることができる不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、第1方向にそれぞれ複数の電極間絶縁膜及び電極膜が交互に積層された積層体と、前記積層体を前記第1方向に貫通する半導体ピラーと、前記電極膜のそれぞれと前記半導体ピラーとの間に設けられ、前記第1方向に延びた記憶層と、前記記憶層と前記半導体ピラーとの間に設けられ、前記第1方向に延びた第1絶縁膜と、前記電極膜のそれぞれと前記記憶層との間に設けられ、前記第1方向に延びた第2絶縁膜と、を備え、前記第2絶縁膜は、前記電極膜同士の間に突出したことを特徴とする不揮発性半導体記憶装置が提供される。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】シリサイド層をゲート電極の一部に含む不揮発性半導体記憶装置において、シリサイド層の膜厚を制御することができる不揮発性半導体記憶装を提供する。

【解決手段】不揮発性半導体記憶装置は、チャネル半導体層上に、ゲート絶縁膜12、浮遊ゲート電極膜13、電極間絶縁膜14および制御ゲート電極15が順に積層されるメモリセルトランジスタMTを有する。制御ゲート電極15は、電極間絶縁膜14上に、半導体膜151、シリサイド相変化抑制膜152およびシリサイド膜154を順に積層した構造を有する。また、シリサイド相変化抑制膜152は、C,F,Nのうちの少なくともいずれか1つの元素が、1×1020〜5×1021[atom/cm3]の濃度範囲で添加された多結晶シリコン膜によって構成される。

(もっと読む)

161 - 180 / 619

[ Back to top ]