Fターム[5F083JA03]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564)

Fターム[5F083JA03]の下位に属するFターム

シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA03]に分類される特許

81 - 100 / 619

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

半導体装置

【課題】半導体装置を小型化する。また、メモリセルを有する半導体装置の駆動回路の面積を縮小する。

【解決手段】少なくとも第1の半導体素子を有する素子形成層と、素子形成層上に設けられた第1の配線と、第1の配線上に設けられた層間膜と、層間膜を介して第1の配線と重畳する第2の配線と、を有し、第1の配線と、層間膜と、第2の配線と、は、第2の半導体素子を構成し、第1の配線と、第2の配線と、は、同電位が供給される配線である半導体装置である。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

ルチル結晶構造を備えた酸化チタン膜の製造方法

【課題】高温のアニールを必要とせずに、誘電率の高いルチル結晶構造の酸化チタン膜を形成する。

【解決手段】非晶質の酸化ジルコニウム膜上に、チタンプリカーサとしてメチルシクロペンタジエニルトリスジメチルアミノチタンを用いてALD法により非晶質の酸化チタン膜を形成し、300℃以上の温度でアニールして結晶化することでルチル結晶構造を有する酸化チタン膜が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

酸化物材料および半導体装置

【課題】トランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。また、このような半導体装置を実現する酸化物材料を提供する。

【解決手段】それぞれ、c軸配向し、ab面、上面または被形成面に垂直な方向から見て少なくとも三角形状または六角形状の原子配列を有し、c軸においては、金属原子が層状または金属原子と酸素原子とが層状に配列しており、In2SnZn2O7(ZnO)m(mは0または自然数。)で表される、ab面(または上面または被形成面)においては、a軸またはb軸の向きが異なる二種以上の結晶部分を含む酸化物膜を用いる。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供すること。また、安定した電気的特性が付与された、信頼性の高い半導体装置を提供すること。

【解決手段】絶縁層に凸状構造体を形成し、該凸状構造体に接して酸化物半導体層のチャネル形成領域を設けることで、チャネル形成領域を3次元方向(基板垂直方向)に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、凸状構造体の上面と側面とが交わる上端コーナー部に曲面を形成し、酸化物半導体層が当該曲面に垂直なc軸を有する結晶を含むように形成する。これによって、酸化物半導体層の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

半導体記憶装置

【課題】電力の供給がない状況でも記憶内容の保持が可能かつ、書き込み回数にも制限がない新たな構造の半導体記憶装置を提供する。

【解決手段】第1のトランジスタのソースまたはドレインの一方が第2のトランジスタのソースまたはドレインの一方と接続し、第1のトランジスタのゲートが第3のトランジスタのソースまたはドレインの一方、およびキャパシタを構成する一対の容量電極の一方と接続し、第1のトランジスタのソースまたはドレインの他方および第3のトランジスタのソースまたはドレインの他方がビット線と接続し、第3のトランジスタのゲートがワード線と接続し、第2のトランジスタのゲートおよびソースまたはドレインの他方がソース線と接続し、キャパシタを構成する一対の容量電極の他方が共通配線と接続し、共通配線はGNDに接続し、共通配線は上面から見て網状に設けられ、第3のトランジスタはその網の目に設けられる半導体記憶装置。

(もっと読む)

半導体装置

【課題】隣接するメモリセル間およびメモリセルと選択トランジスタとの間に間隙を設け

つつ、選択トランジスタおよび周辺回路における短絡を抑制する。

【解決手段】本実施形態による半導体記憶装置は、ゲートを有する複数のメモリセルが直

列に接続されたメモリセルストリングを備える。選択トランジスタが、メモリセルストリ

ングの一端にある端部メモリセルに接続されている。側壁膜が、端部メモリセルと選択ト

ランジスタとの間において、端部メモリセルのゲートの側面および選択トランジスタのゲ

ートの側面を被覆する。端部メモリセルの側壁膜と選択トランジスタの側壁膜との間に空

隙がある。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接する、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタを有し、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第1の酸化絶縁膜上に位置する。

(もっと読む)

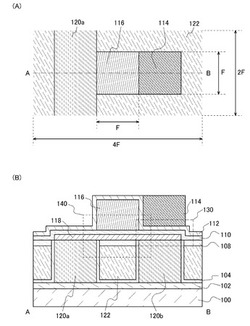

半導体装置及び半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または

、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶

縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と

、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁

層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)

粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層

表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】トランジスタの作製工程において、酸化物半導体層、ソース電極層、ドレイン電極層、ゲート絶縁膜、ゲート電極層、酸化アルミニウム膜を順に作成した後、酸化物半導体層および酸化アルミニウム膜に対して熱処理を行うことで、水素原子を含む不純物が除去され、かつ、化学量論比を超える酸素を含む領域を有する酸化物半導体層を形成する。また、酸化アルミニウム膜を形成することにより、該トランジスタを有する半導体装置や電子機器の作製工程での熱処理でも大気から水や水素が酸化物半導体層に侵入し、拡散することを防止することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

トンネル障壁の上に電界分布層を有する電荷捕獲装置

【課題】チャネル幅寸法に沿った電荷捕獲構造の電荷密度が一様でない場合でもチャネル幅寸法に沿ってしきい値電圧を一様に維持したフラッシュメモリセルおよびフラッシュメモリセルの製造方法を提供する。

【解決手段】ソース領域及びドレイン領域を有する表面を有し、前記ソース領域及び前記ドレイン領域がチャネル領域によって分離された半導体基板と、前記チャネル領域の上の前記基板の表面上に配置された3nmを超える実質的なゲート絶縁膜厚を有するトンネル障壁絶縁体構造105、前記トンネル障壁絶縁体構造及び前記チャネル領域の上に配置された導電層101、前記導電層及び前記チャネル領域の上に配置された電子捕獲構造106、並びに前記電子捕獲構造及び前記チャネル領域の上に配置された上側絶縁体構造107を有する、前記チャネル上の多層スタックと、前記上側絶縁体構造及び前記チャネル領域の上に配置された上側導電層108とを具える。

(もっと読む)

電界効果トランジスタおよびそれを用いたメモリおよび半導体回路

【課題】微細化した半導体集積回路において用いられる、オフ電流の小さな電界効果トランジスタ(FET)を提供する。

【解決手段】絶縁表面に略垂直に形成された厚さが1nm以上30nm以下の薄片状の酸化物半導体と、前記酸化物半導体を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜を覆って形成されたストライプ状の幅10nm以上100nm以下のゲートを有する電界効果トランジスタ。この構成では、薄片状の酸化物半導体の三方の面をゲートが覆うこととなるため、ソース、ドレインから注入される電子を効率的に排除し、ソースとドレインの間をほぼ空乏化領域とでき、オフ電流を低減できる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

記憶装置及び電子機器

【課題】メモリセル毎に選択動作を行う。

【解決手段】装置は、第1のメモリセルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、を具備し、前記第1及び第2のメモリセルのそれぞれは、第1のゲート及び第2のゲートを有し、オン状態又はオフ状態になることにより、メモリセルにおける少なくともデータの書き込み及びデータの保持を制御する電界効果トランジスタを備え、前記第1のメモリセル及び前記第2のメモリセルが備える前記電界効果トランジスタの前記第1のゲートのそれぞれに電気的に接続される行選択線と、前記第1のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第1の列選択線と、前記第2のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第2の列選択線と、をさらに具備する。

(もっと読む)

81 - 100 / 619

[ Back to top ]