Fターム[5F083JA03]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 酸化膜を含む複合膜 (2,564)

Fターム[5F083JA03]の下位に属するFターム

シリコン酸化膜とシリコン窒化膜による複合膜 (1,945)

Fターム[5F083JA03]に分類される特許

141 - 160 / 619

半導体装置の製造方法

【課題】ウィンドウ特性の向上とリテンション特性の向上とを同時に図ることのできる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上に、トンネル酸化膜、チャージトラップ膜、ブロッキング酸化膜、ゲート電極が、下側からこの順で形成された積層構造を有する半導体装置を製造する方法であって、前記ブロッキング酸化膜を形成する工程が、前記チャージトラップ膜上に結晶質膜を形成する結晶質膜形成工程と、前記結晶質膜の上層にアモルファス膜を形成するアモルファス膜形成工程とを具備し、前記結晶質膜形成工程と、前記アモルファス膜形成工程とを同一の処理容器内で連続的に行う。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

半導体記憶装置

【課題】チャネル領域にソース領域及びドレイン領域を形成せずに、信頼性が高い動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、第1の方向に延びる同一導電形のチャネル領域と、チャネル領域上に設けられた第1の絶縁膜と、第1の絶縁膜上に設けられた複数の浮遊ゲートと、浮遊ゲートの上に設けられた第2の絶縁膜と、第2の絶縁膜の上に設けられた制御ゲートとを備えている。複数の浮遊ゲートは第1の方向及びこれに交差する第2の方向に分断されている。制御ゲートは第1の方向に対して交差する第2の方向に延びている。浮遊ゲートのフリンジ電界によって、第1の方向で隣り合う浮遊ゲート間の下のチャネル領域の表面に反転層が形成される。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】空隙AG1の埋め込み絶縁膜4が除去される前に側壁保護膜3´にてトンネル絶縁膜5の側壁を覆うことにより、埋め込み絶縁膜4とトンネル絶縁膜5との間でウェット処理のエッチング選択比が確保できない場合においても、トンネル絶縁膜5を保護できるようにする。

(もっと読む)

3次元半導体素子及びその製造方法

【課題】工程不良を無くして収率を向上させることができる3次元半導体素子及びその製造方法が提供される。

【解決手段】3次元(3D)半導体メモリー素子は、基板に隣接する下段から上段まで伸張して、複数個のメモリーセルと連結された垂直チャンネルと、前記複数個のメモリーセルを有し、前記基板上に配置された階段形構造のゲートスタック形態にアレイされたセルアレイと、を含む。前記ゲートスタックは、前記下段に隣接する下部非メモリートランジスターに連結された下部選択ラインを含む下部膜と、前記上段に隣接する上部非メモリートランジスターに各々連結され、互いに連結されて単一の導電性ピースになって上部選択ラインをなす導電ラインを有する複数個の上部膜と、各々ワードラインを有し、セルトランジスターと連結され、前記下部選択ラインと前記上部選択ラインの間に配置される複数個の中間膜と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】誘電体膜のクラック発生が抑制され、リーク電流特性に優れたキャパシタを有する半導体記憶装置を提供する。

【解決手段】半導体記憶装置の製造方法は、半導体基板上に窒化チタン膜を有する立体構造の下部電極を形成した後、下部電極の表面に誘電体膜を形成する。誘電体膜の表面に、誘電体膜が結晶成長しない温度で第一の上部電極を形成した後、誘電体膜が結晶成長する温度で熱処理し、誘電体膜の少なくとも一部を多結晶状態に変換する。この後、第一の上部電極表面に第二の上部電極を形成する。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】高誘電率を有する薄膜を改質する半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】高誘電体膜が形成された基板を処理室へ搬入する工程と、基板にマイクロ波を照射することにより、高誘電体膜を加熱して改質する工程と、基板を前記処理室から搬出する工程と、を有する半導体装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】半導体装置に用いられるキャパシタを効率よく、しかも少ない占有床面積で行うことができる半導体装置の製造方法および基板処理装置を提供する。

【解決手段】基板200上に下電極を形成する工程(S104)と、下電極の上に、それぞれ異なる金属元素を含む3種の金属酸化膜を積層して誘電膜を形成する工程(S106、S108、S110)と、誘電膜の上に、上電極を形成する工程(S112)と、を有し、各工程は同一の装置で行う。

(もっと読む)

3次元半導体記憶素子

【課題】優れた信頼性を有し、高集積化のために最適化された3次元半導体記憶素子が提供される。

【解決手段】本発明の素子によれば、積層構造体が基板上に配置されて第1の方向に延長される。積層構造体は交互に反復的に積層されたゲートパターン及び絶縁パターンを含む。垂直形活性パターンが積層構造体を貫通する。積層構造体は第1の部分及び第2の部分を含み、積層構造体の第2の部分は第1の方向と垂直である第2の方向に第1の部分より小さい幅を有する。積層構造体の第2の部分の横にストラッピングコンタクトプラグが配置されて、共通ソース領域と接触される。

(もっと読む)

半導体装置

【課題】パーコレーションリークを抑制可能な構造を有する半導体装置を提供する。

【解決手段】ソース領域18、ドレイン領域18及びチャネル領域を有する半導体領域と、チャネル領域上に形成された第1のトンネル絶縁膜12と、第1のトンネル絶縁膜上に形成され、エネルギー障壁を有する障壁層13と、障壁層上に形成された第2のトンネル絶縁膜14と、第2のトンネル絶縁膜上に形成され、SiY(SiO2)X(Si3N4)1-X (ただし、0≦X≦1、Y>0)で表される絶縁膜を具備する電荷蓄積部15と、電荷蓄積部上に形成され、エネルギー障壁の高さを制御する制御電極17とを備え、X及びYは、[2×2X/(4−2X)+(4−4X)/(4−2X)]×[Y/(Y+7−4X)]≧0.016 なる関係を満たし、障壁層は、クーロンブロッケイド条件を満たす導電性微粒子を含んだ微粒子層で形成されている。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

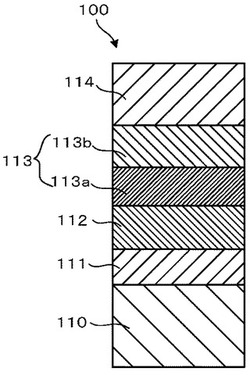

半導体装置の製造方法

【課題】 信頼性に優れた半導体装置を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 シリコンを主成分として含む半導体領域11と、シリコン及び酸素を主成分として含み半導体領域に隣接する絶縁領域12とを有する下地領域の表面を窒化して、窒化膜を形成する工程と、窒化膜に対して酸化処理を施して、窒化膜の絶縁領域上に形成された部分を酸化膜12aに変換するとともに窒化膜の半導体領域上に形成された部分を電荷蓄積絶縁膜の少なくとも一部13aとして残す工程と、電荷蓄積絶縁膜上にブロック絶縁膜15を形成する工程と、ブロック絶縁膜上にゲート電極膜16を形成する工程とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置10は、半導体基板1の表層に第一の方向に延在するように形成された複数の活性領域1aと、前記活性領域1aの表層から深さ方向に形成されたn型不純物拡散層15と、前記複数の活性領域1aを横切り第二の方向に延在するように形成された複数の埋め込みゲート用の溝部13a,bと、ゲート絶縁膜25a,bを介して前記活性領域1a上を跨ぐように前記埋め込みゲート用の溝部13a,bに埋め込まれたゲート電極31およびダミーゲート電極32とを構成すると共に、前記半導体基板1の面上において前記第二の方向に延在する複数のワード配線層と、を具備し、前記ダミーゲート電極32の上面32cが、前記n型不純物拡散層15と前記活性領域1aとの界面よりも下方に位置していることを特徴とする。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】ワード線とコンタクトプラグとの短絡や、ワード線とビット配線との短絡を防ぐことが可能な半導体装置を提供する。

【解決手段】本発明の半導体装置100は、半導体基板50と、前記半導体基板50の表層に、形成された複数の活性領域Kと、前記活性領域Kの表層から深さ方向に形成された不純物拡散層22,24と、前記複数の活性領域Kを横切るように形成された複数の溝部7に、セルゲート絶縁膜7Aを介して前記半導体基板50の上面50aよりも下方に位置するように埋め込まれたワード9線と、前記ワード線9上を埋め込むように形成された窒化シリコンからなる埋込絶縁膜11と、前記不純物拡散層22,24に接続するビット配線と容量コンタクトプラグと、を具備し、前記ビット配線15と容量コンタクトプラグ19の少なくとも一方が、前記埋込絶縁膜11上の一部に重なるように配置されていることを特徴とする。

(もっと読む)

不揮発性メモリー装置の製造方法

【課題】不揮発性メモリー装置の製造方法であって、特に半導体パターン厚さの均一性が向上される3次元半導体装置の製造方法、及び当該製造方法によって製造された3次元半導体装置を提供する。

【解決手段】この製造方法は、基板10の上に複数の第1の膜(鋳型膜)120及び複数の第2の膜(犠牲膜)が交互に積層された積層膜構造体を形成する段階、積層膜構造体を貫通する開口部、及び開口部周囲にアンダーカット領域を形成する段階、アンダーカット領域に局所的に配置される絶縁スペーサー155を形成する段階、絶縁スペーサー155が形成された開口部内に半導体パターン165を形成する段階を含む。

(もっと読む)

半導体不揮発性メモリ装置

【課題】トンネル絶縁膜にエッジ部があることによるトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル絶縁膜の上部であって、トンネル領域のエッジ部から離間した位置に、電荷受け渡し用電極を配置し、電荷受け渡し用電極とフローティングゲート電極とが、電気的に接続されるようにした。

(もっと読む)

金属−絶縁体−金属キャパシタおよびその製造方法

【課題】等価酸化膜厚(EOT)が薄く、漏洩電流の小さいDRAM用のMIMキャパシタを提供する。

【解決手段】基板を準備するステップと、前記基板上に第1電気導電性層上を設けるステップと、原子層堆積法によって、前記導電性層上に層のサブスタックを設けるステップであって、前記サブスタックの少なくとも一層はTiO2層であり、サブスタックの他層は、ペロブスカイト相を形成するのに好適な組成を有する誘電体材料層であるステップとを含む。前記層のサブスタックを含む基板に熱処理を施し、結晶化した誘電体層を得る。サブスタックに存在する一連のTiO2層として改善した特性を有する金属−絶縁体−金属キャパシタを得るために、第2導電性層を熱処理の前または後に製造する。特に、本発明に係るMIMcapにおいて、誘電体層のk値は50〜100であり、MIMキャパシタのEOTは0.35nm〜0.55nmである。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

141 - 160 / 619

[ Back to top ]