Fターム[5F083JA36]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | Al、Al系合金 (2,881)

Fターム[5F083JA36]に分類される特許

121 - 140 / 2,881

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

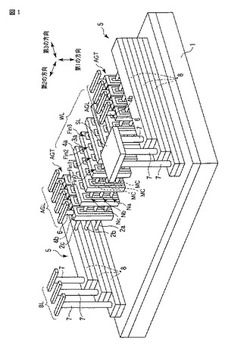

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

マンガン酸化物、マンガン酸化物を備える強誘電体メモリ素子、および強誘電体メモリ装置

【課題】主成分として有害物質鉛元素を含まずに、強誘電性を示しかつ外部磁場によって分極の大きさを制御可能な新規なマンガン酸化物、およびそのメモリへの利用を提供する。

【解決手段】マンガン酸化物は、ペロブスカイト構造を有する、式(1)Sr1−xBaxMnO3(1≧x>0.4)・・・(1)で表されるマンガン酸化物である。単位格子1の対称中心には磁性イオンであるMnイオン3が存在する。単位格子1の対称中心をMnサイトとする。単位格子1が有する8個の頂点には、SrイオンおよびBaイオンのうちいずれか一方が存在している。単位格子1が有する頂点をSrサイト2とする。単位格子1が有する6面の面心には、Oイオン4が存在する。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】消費電力の増大を抑制し且つ微細化を達成した半導体装置および当該半導体装置の作製方法を提供する。また、安定した電気的特性が付与された、信頼性の高い半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜に電界で加速されたイオンを照射して、当該酸化物半導体膜の表面の平均面粗さを低減することにより、トランジスタのリーク電流の増大および消費電力の増大を抑制することができる。さらに、加熱処理を行って、酸化物半導体膜が当該酸化物半導体膜表面に垂直なc軸を有する結晶を含むように形成することにより、酸化物半導体膜の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

半導体記憶装置

【課題】 ビット線選択回路の小型化を図るとともにビット線の駆動時間を高速に行うことができる半導体記憶装置を提供する。

【解決手段】 フラッシュメモリ10は、セルユニットNUが行列状に複数配置されたメモリアレイ100と、セルユニットNUに接続されたビット線を選択するビット線選択回路200とを有する。ビット線選択回路200は、偶数ビット線GBL_e、奇数ビット線GBL_oをセンス回路に選択的に接続するための選択トランジスタSEL_e、SEL_o、BLSを含む第1の選択部210と、偶数ビット線GBL_eおよび奇数ビット線GBL_oに選択的にバイアス電圧を印加するためのバイアストランジスタYSEL_e、YSEL_oとを含む第2の選択部220とを有する。第2の選択部220のバイアストランジスタYSEL_e、YSEL_oは、記憶素子と共通のウエル内に形成される。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、MTJ素子がコンタクトプラグ内のシームまたはボイドの影響を受けることなく、MTJ素子の特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数のセルトランジスタは、半導体基板上に設けられている。コンタクトプラグは、隣接するセルトランジスタ間に埋め込まれ、該隣接するセルトランジスタ間にある拡散層に電気的に接続されている。層間絶縁膜は、複数のコンタクトプラグ間を埋め込む。記憶素子は、コンタクトプラグの上方に設けられておらず、層間絶縁膜の上方に設けられている。側壁膜は、記憶素子の側面の少なくとも一部を被覆し、半導体基板の表面上方から見たときに、コンタクトプラグに重複するように設けられている。下部電極は、記憶素子の底面と層間絶縁膜との間、および、側壁膜とコンタクトプラグとの間に設けられ、記憶素子とコンタクトプラグとを電気的に接続する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と該酸化物半導体膜と接する下地となる膜との界面の電子状態が良好なトランジスタ。

【解決手段】下地となる膜は酸化物半導体膜と同様の原子配列を有し、下地となる膜と酸化物半導体膜とが接している面において、面内の下地膜の最隣接原子間距離と酸化物半導体の格子定数の差を、下地となる膜の同面内における最隣接原子間距離で除した値は0.15以下、好ましくは0.12以下、さらに好ましくは0.10以下、さらに好ましくは0.08以下とする。例えば、立方晶系の結晶構造を有し(111)面に配向する安定化ジルコニアを含む下地となる膜上に酸化物半導体膜を成膜することで、下地となる膜の直上においても結晶化度の高い結晶領域を有する酸化物半導体膜が得られる。

(もっと読む)

半導体装置の作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、メモリアレイのレイアウト面積を低減する。

【解決手段】給電領域において、メモリゲートシャント部が形成される領域の素子分離部に溝25が形成されており、選択ゲートシャント部に備わる選択ゲートシャント電極VCは、メモリセル形成領域に形成された選択ゲート電極CGに繋がる第1導電膜からなり、メモリゲートシャント部に備わるメモリゲートシャント電極VMは、給電領域に形成された選択ゲート電極CGの延長部の片側面の一部および素子分離部に形成された溝25の側面の一部に絶縁膜6b,6tおよび電荷蓄積層CSLを介してサイドウォール状に形成され、メモリセル形成領域に形成されたメモリゲート電極MGに繋がる第2導電膜からなる。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し

、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形

成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことによ

り、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成

し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面

に水素を供給する。

(もっと読む)

半導体装置の製造方法

【課題】充分なキャパシタ容量を有する半導体装置を提供する。

【解決手段】半導体装置100の製造方法は、次の工程を含む。まず、基板(半導体基板102)上に下部電極152を形成する。次いで、下部電極152を第1結晶化処理する。次いで、第1結晶化処理後の下部電極152の上に容量絶縁層154を形成する。次いで、容量絶縁層154を第2結晶化処理する。この後、容量絶縁層154上に上部電極156を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

121 - 140 / 2,881

[ Back to top ]