Fターム[5F083JA38]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 白金族元素、Au、及び、その合金 (2,740)

Fターム[5F083JA38]に分類される特許

201 - 220 / 2,740

半導体装置および半導体装置の駆動方法

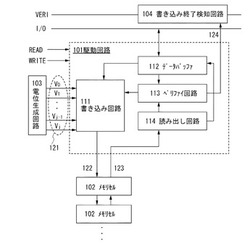

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置

【課題】実動作キャパシタとダミーキャパシタとが形成された半導体装置において、水素・水分、不均一なストレスによる実動作キャパシタの性能劣化を抑制し、FeRAMの寿命特性を向上する。

【解決手段】半導体基板10上の実動作キャパシタ部26の下部電極30と強誘電体膜32と上部電極34を有する複数の実動作キャパシタ36aと、半導体基板10上の実動作キャパシタ部26の外側のダミーキャパシタ部28の下部電極30と強誘電体膜32と上部電極34を有する複数のダミーキャパシタ36bと、複数の実動作キャパシタ36a上の複数の配線40と、複数のダミーキャパシタ36b上の配線40を有し、ダミーキャパシタ36bのピッチの実動作キャパシタ36aのピッチに対する比は、0.9〜1.1の範囲にあり、ダミーキャパシタ36b上の配線40のピッチの実動作キャパシタ36a上の配線40のピッチに対する比は、0.9〜1.1の範囲にある。

(もっと読む)

セラミックス前駆体薄膜の製造方法および前駆体溶液

【課題】単一配向の結晶配向性が高いセラミックス薄膜を得ることができるセラミックス前駆体薄膜の製造方法および前駆体溶液を提供する。

【解決手段】本発明に係るセラミックス前駆体薄膜の製造方法は、金属アルコキシド溶液を希釈した希釈溶液に、アモルファス粉末を混合し、金属アルコキシド系化合物を含む前駆体溶液を作製する前駆体溶液作製工程と、前記前駆体溶液を用いてゲル膜を成膜するゲル膜成膜工程と、を含むことを特徴とする。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】可変抵抗素子のデータ保持特性を向上させることのできる半導体記憶装置及びその製造方法を提供する。

【解決手段】一の実施の形態に係る半導体記憶装置は、基板上に配置された複数の第1配線と、第1配線と交差するように配置され、第1配線と基板との間に位置する複数の第2配線と、第1配線と第2配線との各交差部に配置され、電流整流素子及び可変抵抗素子を直列接続してなる第1のメモリセルを含む第1のメモリセルアレイとを備える。第1のメモリセルの可変抵抗素子は、第1の金属材料の酸化物により形成された第1記録層と、第1の金属材料により形成され、且つ、第1記録層と接するように形成された第2記録層とを有する。第2記録層は第1記録層に比べ第1配線に近い側に設けられる。

(もっと読む)

抵抗メモリ素子および関連する制御方法

【課題】電圧制御されたプログラム可能な抵抗層を有する抵抗メモリ素子とプログラミング方法を提供する。

【解決手段】参照面に平行な面に横たわり、参照面上の垂直な投影で上部電極投影を有する上部電極素子12と、参照面に平行な面に横たわり、参照面上の垂直な投影で下部電極投影を有する下部電極素子14と、上部電極素子12と下部電極素子14との間に挿入された可変性の抵抗率を有する活性層16を含む抵抗メモリ素子10において、上部電極投影と下部電極投影との間にオーバーラップ領域L3があり、オーバーラップ領域L3は少なくとも上部電極投影のコーナーおよび/または少なくとも下部電極投影のコーナーを含み、オーバーラップ領域L3の面積は、参照面上の、上部電極素子12と下部電極素子14の全投影面積の10%以下を構成する。

(もっと読む)

記憶装置およびその製造方法

【課題】メモリセルの構造を最適化することにより、更なる微細化を可能にする記憶装置を提供する。

【解決手段】複数の第1の電極配線と、第1の電極配線と交差する複数の第2の電極配線と、1本の第2の電極配線と、互いに隣接する2本の第1の電極配線との間に形成される1個のビアプラグであって、前記第1の電極配線に対向する底面の、第1の電極配線の伸長方向に垂直な方向の最大径が、第1の電極配線幅の2倍と第1の電極配線間の幅を加えた長さよりも小さいビアプラグと、ビアプラグと2本の第1の電極配線の一方との間に形成される第1の記憶素子と、ビアプラグと2本の第1の電極配線の他方との間に形成される第2の記憶素子とを有する記憶装置。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

メモリセルキャパシタ構造におけるメモリセルキャパシタプレートの形成方法

【課題】酸素にさらされても絶縁膜を形成しない材料からメモリセルキャパシタプレートを製造するための形成方法を提供する。

【解決手段】メモリセルキャパシタプレートの形成方法は、犠牲層を堆積する工程と、その犠牲層内に開口部を形成する工程とを含む。続いて、酸素にさらされても相当の導電性を維持する導電性料を含む電極材料層702を、犠牲層の上面に堆積し、開口部の少なくとも一部を充填する。次に、電極材料層702の一部を少なくとも犠牲層の上面と同じ略同じ高さにまで除去することによりメモリセルキャパシタプレートの上面を画定し、その後、犠牲層を除去する。

(もっと読む)

記憶素子および記憶装置

【課題】低電流動作に優れると共に良好な保持特性を有する記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20はテルルを(Te)を最も多く含む層を有する抵抗変化層22と、アルミニウム(Al)を27.7原子%以上47.4原子%以下の範囲内で含有するイオン源層21とを有する。これにより、消去時に抵抗変化層22中に析出した金属元素がイオン源層21へ溶解しやすくなると共に、書き込みおよび消去後の抵抗状態が維持される。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

不揮発性半導体記憶装置及びフォーミング方法

【課題】フォーミング処理の時間を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】複数の不揮発性メモリセルは、可変抵抗素子及び整流素子が直列接続されている。制御部は、第1のタイミングにおいて、Nを1以上の整数とするとき複数のワードラインからN本おきに第1のラインを多重選択して選択電位に設定するとともに、少なくとも多重選択されたワードラインに隣接する非選択のワードラインの電位を固定する。制御部は、第2のタイミングにおいて、上記の多重選択されたワードラインを浮遊状態にする。第2のタイミングは、第1のタイミングより後のタイミングである。制御部は、第3のタイミングにおいて、複数のビットラインから1本の第2のラインを選択してフォーミング電位に設定する。第3のタイミングは、第2のタイミングより後のタイミングである。

(もっと読む)

抵抗変化型不揮発性記憶装置

【課題】メモリセルのトランジスタのサイズを最適化可能とした抵抗変化型不揮発性記憶装置を提供する。

【解決手段】下部電極309aと上部電極309cと抵抗変化層309bとからなる抵抗変化素子309と、トランジスタ317とを直列に接続してなるメモリセル300において、トランジスタ317は、ゲート303bと、下部電極309aに電気的に接続されたドレイン又はソース302bと、ソース線SL0に電気的に接続されたソース又はドレイン302aとを有し、ソース線SL0は、互いに平行に配置されかつ1つ以上のビアで接続された複数のレイヤーで形成される配線層305、307からなり、抵抗変化素子309はいずれの配線層305、307よりも半導体基板301からより遠い側に配置され、ビット線BL0は、抵抗変化素子309に対し、半導体基板301からより遠い側に配置され上部電極309cと接続される。

(もっと読む)

記憶素子および記憶装置

【課題】低電圧および低電流動作時における繰り返し特性が向上した記憶素子および記憶装置を提供する。

【解決手段】下部電極10、記憶層20および上部電極30をこの順に積層した記憶素子1において、記憶層20は、2.8mΩcm以上1Ωcm未満の抵抗率を有するイオン源層21と、抵抗変化層22とを有する。これにより、低電圧または低電流パルスを印加した際の記録状態から消去状態への抵抗変化層の抵抗値の回復が改善され、繰り返し特性が向上する。

(もっと読む)

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイに用いられる配線の抵抗を低減することができる半導体記憶装置の製造方法を提供する。

【解決手段】一の実施の形態に係る半導体記憶装置の製造方法は、第1配線層を積層する工程と、第1配線層の上方にメモリセル層を積層する工程と、メモリセル層の上方に、後の研磨工程を減速させるためのストッパ膜を積層する工程とを備える。また、製造方法は、ストッパ膜、メモリセル層、及び第1配線層をエッチングする工程と、ストッパ膜、メモリセル層、及び第1配線層を層間絶縁膜により埋め込んだ後、ストッパ膜に達するまで研磨する工程と、ストッパ膜及び層間絶縁膜に窒化処理を実行して、ストッパ膜及び層間絶縁膜の表面にそれぞれ調整膜及びブロック膜を形成する工程とを備える。そして、製造方法は、調整膜の上方に、エッチングされた第1配線層と交差して各交差部にメモリセルが配置されるように、第2配線層を形成する工程を備える。

(もっと読む)

不揮発性抵抗変化素子

【課題】電極との間で金属の出し入れが行われることで可逆的に抵抗が変化される抵抗変化層の絶縁性の劣化を抑制する。

【解決手段】抵抗変化層2は半導体元素を有し、第2電極4の金属元素が出し入れされることで可逆的に抵抗変化が可能で、誘電体層3は、第2電極4と抵抗変化層2との間に挿入され、抵抗変化層2よりも第2電極4の金属元素の拡散係数が小さい。

(もっと読む)

201 - 220 / 2,740

[ Back to top ]