Fターム[5F083JA38]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 白金族元素、Au、及び、その合金 (2,740)

Fターム[5F083JA38]に分類される特許

2,721 - 2,740 / 2,740

不揮発性メモリデバイス

選択的な横方向の電導率を有する活性層を含むことができるメモリデバイスである。活性層は複数のナノ粒子を含む。 (もっと読む)

ナノクラスターを備えた半導体デバイス

ナノクラスターを備えたデバイスを形成するプロセス。本プロセスは、ナノクラスター(例えばシリコンナノ結晶)を形成する段階と、デバイスの誘電体を形成する次の段階中に酸化剤によるナノクラスターの酸化を抑制するためにナノクラスターを覆って酸化バリア層を形成する段階とを含む。酸化バリア層の少なくとも一部は、誘電体の形成後に除去される。1つの実施例では、本デバイスは、ナノクラスターがメモリの電荷蓄積トランジスタの電荷蓄積位置として利用されるメモリである。この実施例では、酸化バリア層が、メモリの高電圧トランジスタ用のゲート誘電体を形成することにより、ナノクラスターを酸化剤から保護する。 (もっと読む)

記憶装置用材料及びセル構造

本発明はメモリ用組成物に関し、同組成物と、2つの電極とからなるメモリセルに関する。さらに本発明は、微細電子部品の製造方法及び微細電子部品の製造における本発明の組成物の使用に関する。 (もっと読む)

縦型強誘電体キャパシタの形成方法

縦構造を持つ強誘電体キャパシタが、絶縁層(31)上に強誘電体層(33)が堆積されるプロセスによって形成される。第1のエッチング工程では、上記強誘電体材料がエッチングされて、その内部に開口部(35)が形成される。このとき、上記絶縁層は実質的にそのままにしておく。次に、上記強誘電体層内に形成された上記開口部内に、導電性の層(39)が堆積されて、上記開口部の側面に電極が形成される。さらにエッチングが行われて、上記Al2O3層(31)内にギャップが形成されて、その下にある導電性素子(3)と接触させる。従って、第2のエッチング工程が行われる時点までには、既に電極が上記強誘電体材料の側面を覆っていて、その間に絶縁フェンスは形成されない。  (もっと読む)

(もっと読む)

強誘電体キャパシタおよびFeRAMデバイスの形成方法

導電性材料を堆積し、そしてこの導電性材料をエッチングして電極を形成することによって、FeRAMデバイスの縦型キャパシタが形成される。上記電極は、絶縁層内にある開口部の上に配置されるため、上記構造の低い位置に電気的に接続される。上記電極の側面に強誘電体材料の層が形成され、そして所望の均一な厚みになるまでエッチングされる。上記強誘電体材料の上に導電性材料が堆積されて、別の絶縁層を堆積できる均一な表面が形成される。上記プロセスは、上記電極の形成と上記強誘電体材料の堆積との間に絶縁層をエッチングする工程を含んでいないため、これらの間に絶縁材料のフェンスが形成されることがない。形状を正確に制御して、均一な電界と信頼性のある動作パラメータを得ることができる。  (もっと読む)

(もっと読む)

縦型ナノトランジスタおよび該トランジスタの製造方法ならびにメモリ装置

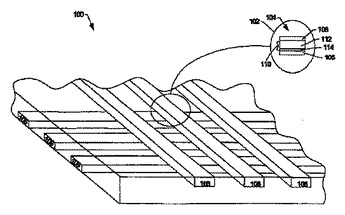

本発明の課題は、機械的応力に対し良好な耐性をもち、その製造が公知の従来技術よりも煩雑でない縦型ナノトランジスタを提供することである。本発明によればこの課題は、以下の特徴を備えた縦型ナノトランジスタによって解決される。すなわちソースコンタクトと、ドレインコンタクトと、ゲート領域と、ソースコンタクトとドレインコンタクトの間に配置され半導体特性をもつ円筒状のチャネル領域が設けられており、この円筒状チャネル領域は絶縁性フレキシブル基板に埋め込まれており、この領域は、ゲート領域とチャネル領域上部が同軸構造を成すよう、フレキシブル基板上およびチャネル領域上部の金属層により形成されたゲート領域により取り囲まれている。さらにソースコンタクトと半導体特性をもつチャネル領域とドレインコンタクトは縦方向に配置されていて、ソースコンタクトとドレインコンタクトと半導体特性をもつチャネル領域に対向するゲート領域と、基板の上側および下側は電気的に絶縁性の部材を有している。メモリ装置は多数のこの種の縦型ナノトランジスタから成る。本発明はこの種のトランジスタの製造方法にも関する。  (もっと読む)

(もっと読む)

縦型ナノトランジスタおよび該トランジスタの製造方法ならびにメモリ装置

本発明の課題は、機械適応力に対する耐性が良好であり、公知の従来技術よりも製造が煩雑でない縦型ナノトランジスタを提供することである。本発明によればこの課題は、以下の特徴を備えた縦型ナノトランジスタによって解決される。すなわちソース領域と、ドレイン領域と、ゲート領域と、ソース領域とドレイン領域との間に配置され半導体特性をもつチャネル領域が設けられており、ゲート領域は金属シートにより形成されており、ゲート領域と半導体特性をもつチャネル領域により同軸構造が形成されるよう、この金属シートにトランジスタが埋め込まれていている。この場合、ソース領域と半導体特性をもつチャネル領域とドレイン領域は垂直方向に配置されており、ゲート領域は、ソース領域とドレイン領域と半導体特性をもつチャネル領域に対向して電気的絶縁部材を有している。さらに本発明はこの種のトランジスタの製造方法ならびにメモリ装置にも関する。  (もっと読む)

(もっと読む)

酸化物薄膜製造方法及びその製造装置

酸化物薄膜の酸素欠損の低下とエピタキシャル成長との促進を図ることにより、優れた特性を有する酸化物薄膜を製造する薄膜製造方法であって、原料ガス、キャリアガス及び酸化ガスを混合して得た混合ガスを、加熱手段により原料の液化、析出、成膜が起こらない温度に維持されたガス活性化手段を通してシャワープレートから反応室内の加熱基板上に供給して反応させ、基板上に酸化物薄膜を製造する。その際、酸化ガスの割合を混合ガス基準で60%以上とする。また、核形成による初期層を形成する場合、その成膜プロセスにおける酸化ガス流量割合を60%未満とし、その後の成膜プロセスにおける酸化ガス流量割合を60%以上として行う。また、酸化物薄膜製造装置において、混合器とシャワープレートとの間に加熱手段を備えてなる。 (もっと読む)

メモリ用相変化アクセス装置

メモリは、カルコゲナイド材料を用いて形成されたアクセス装置を有する。アクセス装置は、アクセスされた対応メモリ素子の読み出しを妨害するスナップバック電圧を生じない。相変化メモリ素子の場合、スナップバック電圧は、層変化メモリ素子の閾値電圧よりも小さい。  (もっと読む)

(もっと読む)

スイッチング素子

【課題】 転移確率を高くしてスイッチング特性を安定化した、双安定特性を持つスイッチング素子を提供する。

【解決手段】 少なくとも2つの電極間に、印加される電圧に対して2種類の安定な抵抗値を持つ有機双安定化合物を含む有機双安定材料層を配置してなるスイッチング素子であって、基板10上に、第1電極層20a、金属微粒子含有層40、有機双安定材料層30、第2電極層20bの順に薄膜として形成され、金属微粒子含有層40が、金属微粒子と有機双安定化合物とを含む層である。

(もっと読む)

FeRAMキャパシタの製造方法及び該方法により作成されたFeRAMキャパシタ

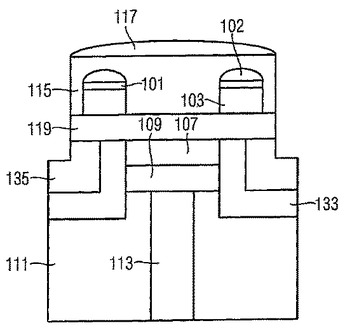

強誘電体デバイスは底部電極119を含んでいる。底部電極119の上には強誘電体キャパシタ素子103が形成され、この強誘電体キャパシタ素子103の上に頂部電極101が形成されている。底部電極119は、導電性プラグ113を介して、該デバイスの下側層に接続されている。そして、プラグ113と底部電極119とは、Ir及び/又はIrO2からなるバリア素子107、109によって離間させられている。両バリア素子107、109は、底部電極119よりも狭く、個別のエッチング処理により形成される。これは、底部電極119のエッチング時にはIrの囲いが形成されないということを意味する。また、Ir及び/又はIrO2が、底部電極119を介して強誘電体キャパシタ素子に拡散することはほとんどない。それゆえ、強誘電体材料に損傷が生じる危険性はほとんどない。  (もっと読む)

(もっと読む)

メモリデバイス及びこのデバイスの使用方法ないし製造方法

2つの電極(106、206、108、204)間に制御可能な導電媒体(110)を備える2つの電極で作られるメモリセル(104)を開示する。制御可能な導電媒体(110)は、活性低導電層(112)及び受動層(114)を備える。制御可能な導電媒体(110)は、電界の印加のような外部刺激が供給されると、インピーダンスか変わる。メモリデバイス/セルの作製方法、メモリデバイス/セルの使用方法、及び、メモリテバイス/セルを含むコンピュータのようなテバイスの使用方法も開示する。  (もっと読む)

(もっと読む)

FETベースの磁気ランダム・アクセス・メモリ・デバイス用の自己整列型導電線およびこれを形成する方法

【課題】下部メタライズ線(302)に導電的に結合された横方向の金属ストラップ(326)を含む、電界効果トランジスタ(FET)ベースの磁気ランダム・アクセス・メモリ(MRAM)デバイス用の導電線構造を提供すること。

【解決手段】金属ストラップ(326)上に磁気トンネル接合(MTJ)スタック(316)が形成され、MTJスタック(316)を覆って金属シールド(324)が形成され、金属シールド(324)は金属ストラップ(326)に対して自己整列される。上部メタライズ線(332)は金属シールド(324)に導電的に結合され、金属シールド(324)は上部メタライズ線(332)の形成時にエッチ・ストップとして働く。

(もっと読む)

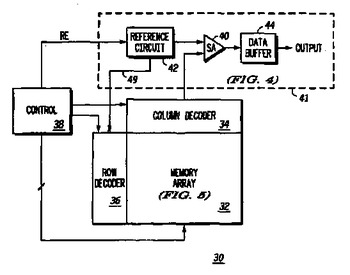

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

強誘電体膜およびその製造方法ならびに半導体装置

【課題】 低温の結晶化により良好な特性を有するBi層状ペロブスカイト構造を有する強誘電体膜の製造方法を提供する。

【解決手段】 本発明の強誘電体膜の製造方法は、第1の原料液と、第2の原料液とを含む強誘電体の原料液を結晶化することにより、強誘電体膜を形成する工程を含み、前記第1の原料液と前記第2の原料液とは、種類が異なる関係にあり、前記第1の原料液は、Bi系層状ペロブスカイト構造を有する強誘電体を生成するための原料液であり、前記第2の原料液は、AサイトがPbであるABO3系酸化物を生成するための原料液である。

(もっと読む)

トリス(オクタン−2,4−ジオナト)イリジウム、これを含有してなる化学気相成長用原料及び薄膜の製造方法

【課題】 CVD法に適する液体イリジウム化合物、これを用いたCVD用原料、及び該CVD用原料を用いたイリジウム薄膜の製造方法を提供すること。

【解決手段】 トリス(オクタン−2,4−ジオナト)イリジウム。

(もっと読む)

磁気抵抗効果型素子ならびにこれを用いた磁気記憶素子および磁気ヘッド

【課題】 ペロブスカイト型酸化物を用いて良好なトンネル接合を実現し、低磁場でも大きな磁気抵抗効果を発現する磁気抵抗効果型素子を提供する。

【解決手段】 式L2(A1-zRz)2An-1MnO3n+3+xにより表される組成を有し、結晶構造内に(L-O)2層を有する層状ペロブスカイト型酸化物と、この酸化物を挟むようにこれに接して形成された一対の強磁性体と、を含む磁気抵抗効果型素子とする。ただし、AはCa、SrおよびBaから選ばれる少なくとも1種の元素を、LはBi、TlおよびPbから選ばれる少なくとも1種の元素を、MはTi、V、Cu、Ru、Ni、Mn、Co、FeおよびCrから選ばれる少なくとも1種の元素を、Rは希土類元素をそれぞれ示し、nは1、2または3であり、x、zは、それぞれ、−1≦x≦1、0≦z<1により示される範囲内の数値である。

(もっと読む)

強誘電体膜を有する半導体装置の製造方法

【課題】強誘電体膜をエッチングする際に生じる反応副生成物を形成される素子に悪影響を与えることなく除去する。

【解決手段】強誘電体膜をエッチングしたあと、燐酸水溶液を用いてウェット処理をする。レジストをマスクとして強誘電体膜をエッチングしたあと、レジストアッシング後またはアッシング前後の両方に燐酸水溶液を用いてウェット処理をする。

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

半導体装置の製造方法、強誘電体キャパシタ、およびその製造方法

【課題】 強誘電体キャパシタを有する半導体装置の製造において、強誘電体膜の自発分極を最大化する。

【解決手段】 下側電極を形成後、強誘電体膜を堆積する前に、前記下側電極を不活性雰囲気中において急速熱処理する。

(もっと読む)

2,721 - 2,740 / 2,740

[ Back to top ]