Fターム[5F083JA38]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 白金族元素、Au、及び、その合金 (2,740)

Fターム[5F083JA38]に分類される特許

141 - 160 / 2,740

半導体装置および半導体装置の駆動方法

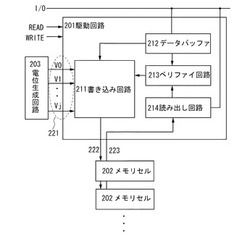

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、を有し、駆動回路は、

データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

半導体装置及びその駆動方法

【課題】消費電力を低減することが可能な新たな構造の半導体装置及びその駆動方法を提供する。

【解決手段】メモリセルは、容量素子と、第1のトランジスタと、第1のトランジスタよりオフ電流の小さな第2のトランジスタとを有する。第1のトランジスタは、第2のトランジスタよりもスイッチング速度が速い。第1のトランジスタと第2のトランジスタと容量素子とは直列に電気的に接続されている。容量素子への電荷の蓄積、及び容量素子からの電荷の放出は、第1のトランジスタと第2のトランジスタの両方を介して行われる。こうして、半導体装置の消費電力を少なく、且つ情報の書き込み及び読み出し速度を高速化することができる。

(もっと読む)

記憶素子及び記憶装置

【課題】極性の異なる電気パルスを印加する場合でも書き込みディスターブの発生を防止することが可能であり、かつ抵抗変化素子に大電流を流すことが可能である、データを問題無く書き込み可能な(即ち、書き込みディスターブが発生しない)記憶素子及びそれを備える記憶装置を提供する。

【解決手段】

極性が正又は負の電気パルスの印加によりその電気抵抗値が変化しかつ該変化した後の電気抵抗値を維持する抵抗変化素子1と、抵抗変化素子1に電気パルスの印加時に流れる電流を抑制する電流抑制素子2と、を備え、抵抗変化素子と電流抑制素子2とが直列に接続された記憶素子3であって、電流抑制素子2は、第1の電極と、第2の電極と、第1の電極と第2の電極との間に配設された電流抑制層と、を備え、電流抑制層が、SiNx(0<x≦0.85)でかつアモルファス半導体により構成されている。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

不揮発性抵抗変化素子

【課題】信頼性の高い整流機能を有する不揮発性抵抗変化素子を提供する。

【解決手段】Ag,Ni,Co,Al,Zn,Ti,Cuのうち少なくともいずれかを含む上部電極1と、下部電極2と、上部電極1と下部電極2とに挟まれた抵抗変化層3と、下部電極2と抵抗変化層3との間に配置され、抵抗変化層3を構成する元素と、Ag,Ni,Coのうち少なくともいずれかの元素とを含む整流機能層4を備える。上部電極1と下部電極2間に印加する電圧に応じて、上部電極1と下部電極2間の電気抵抗が可逆的に変化する。

(もっと読む)

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法

【課題】少ない工程数で製造でき、フラットバンド電圧のシフトを抑制できる選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法を提供すること。

【解決手段】直列接続された複数のメモリトランジスタを備えたメモリ装置で用いられる選択トランジスタであって、半導体基板上に形成されたトンネル絶縁層と、トンネル絶縁層上に形成された電荷蓄積層と、電荷蓄積層上に形成され、アルゴンをソースガスとするガスクラスタイオンビームが照射されたブロッキング絶縁層と、ブロッキング絶縁層上に形成されたゲート電極と、ゲート電極の両側の半導体基板中に形成されたソース/ドレイン領域と、を具備する。

(もっと読む)

半導体記憶装置の製造方法

【課題】クロスポイント型セル構造の配線構造を正確に形成する。

【解決手段】

第1の配線を形成する第1配線層及びメモリセルを形成するメモリセル層を順次積層してなる第1積層構造を第1方向に延びるストライプ状にエッチングする。このとき、第1ストライプ部の側部から第2方向に突出する第1フック部を形成する。そして、第1積層構造の上層に第2積層構造を形成し、この第2積層構造を2方向に延びるストライプ状にエッチングする。このとき、第2ストライプ部の側部から第1方向に突出する第2フック部を形成する。上記を所定数繰り返す。そして、第1又は第2フックの側面に接するコンタクトプラグを形成する。第2フック部が形成されるべき領域では、第1積層構造を除去し、また、第1フック部が形成されるべき領域では、第2積層構造を除去する。

(もっと読む)

ルチル結晶構造を備えた酸化チタン膜の製造方法

【課題】高温のアニールを必要とせずに、誘電率の高いルチル結晶構造の酸化チタン膜を形成する。

【解決手段】非晶質の酸化ジルコニウム膜上に、チタンプリカーサとしてメチルシクロペンタジエニルトリスジメチルアミノチタンを用いてALD法により非晶質の酸化チタン膜を形成し、300℃以上の温度でアニールして結晶化することでルチル結晶構造を有する酸化チタン膜が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

配向性圧電セラミックス、圧電素子、液体吐出ヘッド、超音波モータおよび塵埃除去装置

【課題】圧電性能が良好な(1−x)NaNbO3−xBaTiO3の配向性圧電セラミックスを提供する。また本発明は、前記(1−x)NaNbO3−xBaTiO3の配向性圧電セラミックスを用いた圧電素子、ならびに前記圧電素子を用いた液体吐出ヘッド、超音波モータおよび塵埃除去装置を提供する。

【解決手段】下記一般式(1)で表わされる金属酸化物を主成分として含み、鉛とカリウムの含有量は各々1000ppm以下であることを特徴とする配向性圧電セラミックス一般式(1) (1−x)NaNbO3−xBaTiO3(式中、 0 < x < 0.3)。

(もっと読む)

不揮発性記憶装置

【課題】低コストで量産性に優れた不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、下側電極膜と、前記下側電極膜の上に設けられ、第1酸化物を含有する第1記憶素子膜と、前記第1記憶素子膜の上に設けられた上側電極膜と、を有する第1状態と、もしくは、前記下側電極膜と、前記下側電極膜の上に設けられた前記第1記憶素子膜と、前記第1記憶素子膜の上に設けられ、第2酸化物を含有する第2記憶素子膜と、前記第2記憶素子膜の上に設けられた前記上側電極膜と、を有する第2状態と、を維持することが可能である。前記第2記憶素子膜に含まれる酸素濃度は、前記第1記憶素子膜に含まれる酸素濃度よりも高い。前記第2状態における前記下側電極膜と前記上側電極膜との間の抵抗は、前記第1状態における前記下側電極膜と前記上側電極膜との間の抵抗よりも高い。

(もっと読む)

抵抗変化素子の制御方法、および、半導体装置

【課題】抵抗変化素子の閾値電圧のばらつきを生じさせることなく、閾値電圧を低電圧化すること。

【解決手段】印加されたパルス電圧の極性に応じて抵抗値の異なる第1の状態と第2の状態との間で遷移する抵抗変化層と、抵抗変化層の一端に接続された第1の電極と、他端に接続された第2の電極とを備えた抵抗変化素子の制御方法であって、抵抗変化層を第1の状態から前記第2の状態へ遷移させる第1の極性とは逆の第2の極性を有する第1のパルス電圧を、抵抗変化層を第1の状態に保ちつつ、両電極間に印加した後、第1の極性を有する第2のパルス電圧を両電極間に印加して、抵抗変化層を第1の状態から第2の状態へ遷移させる。

(もっと読む)

不揮発性記憶素子及びその製造方法並びに不揮発性記憶装置

【課題】不揮発性記憶素子の初期化電圧のばらつきの発生を抑えつつ、従来に比べて初期化電圧の低減を図ることができる抵抗変化型の不揮発性記憶素子を提供する。

【解決手段】第1の層間絶縁層102、下部電極105、上部電極107及び抵抗変化領域106を備え、抵抗変化領域106は積層された第1の抵抗変化領域106bと第2の抵抗変化領域106aを有し、第1の抵抗変化領域106bは第1の遷移金属酸化物で構成され、第2の抵抗変化領域106aは第2の遷移金属酸化物で構成され、第2の遷移金属酸化物の酸素不足度は第1の遷移金属酸化物の酸素不足度より小さく、抵抗変化領域106の上面は上部電極107と接し、抵抗変化領域106の底面は下部電極105及び第1の層間絶縁層102と接し、抵抗変化領域106の底面と下部電極105の接する面の面積は抵抗変化領域106の上面と上部電極107の接する面の面積より小さい。

(もっと読む)

不揮発性抵抗変化素子

【課題】抵抗を可逆的に変化させことを可能としつつ、データ保持特性を向上させる不揮発性抵抗変化素子を提供する。

【解決手段】第1電極1と、第2電極3と、可変抵抗層2とを備え、第2電極3は、Al元素が添加された1B族元素を有し、可変抵抗層2は、第1電極1と第2電極3との間に配置され、シリコン元素を有する。可変抵抗層2は非晶質シリコン層であってもよいし、多結晶シリコン層であってもよいし、単結晶シリコン層であってもよい。第1電極1は不純物ドープシリコンおよびTi、Ni、Co、Fe、Cr、Cu、W、Hf、Ta、Pt、Ru、ZrまたはIrや、その窒化物あるいは炭化物あるいはカルコゲナイド材料などを用いることができる。

(もっと読む)

高誘電性ナノシート積層体、高誘電性ナノシート積層体、高誘電体素子、および高誘電体薄膜素子の製造方法

【課題】コンデンサなどに好適な、非常に薄くしても高い誘電率と良好な絶縁特性を同時に実現する高誘電体薄膜を提供する。

【解決手段】上記課題は、ペロブスカイト構造を有する酸化物ナノシートなどの高誘電体により構成される薄膜により達成される。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

141 - 160 / 2,740

[ Back to top ]