Fターム[5F083JA38]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 白金族元素、Au、及び、その合金 (2,740)

Fターム[5F083JA38]に分類される特許

61 - 80 / 2,740

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

半導体記憶装置

【課題】記憶素子の加工が容易であり、かつ、記憶素子が安定した特性を有するメモリを提供する。

【解決手段】本実施形態によるメモリは、半導体基板を備える。複数のアクティブエリア列は、半導体基板上に設けられ第1の方向に配列された複数のアクティブエリアをそれぞれが含む複数のアクティブエリア列であり、第1の方向に対して直交する第2の方向に隣接するアクティブエリアは互いに半ピッチずつずれて配置されている。複数のセルトランジスタは、アクティブエリアのそれぞれに対応して設けられている。複数の記憶素子は、複数のセルトランジスタの一端に電気的に接続されている。上部電極は、複数のアクティブエリア列のうち第2の方向に隣接する第1および第2のアクティブエリア列に対応する複数の記憶素子に交互に接続されている。ビット線は、第1および第2のアクティブエリア列に含まれる複数のセルトランジスタの他端に電気的に接続されている。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

半導体記憶装置

【課題】十分な消去速度が得られる半導体記憶装置を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上にそれぞれ交互に積層された複数の電極層と複数の第1の絶縁層とを有する第1の積層体と、前記第1の積層体上に設けられ、選択ゲートとその上に設けられた第2の絶縁層とを有する第2の積層体と、前記第1の積層体を積層方向に貫通して形成された第1のホールの側壁に設けられたメモリ膜と、前記第1のホールと連通し、前記第2の積層体を積層方向に貫通して形成された第2のホールの側壁に設けられたゲート絶縁膜と、前記メモリ膜の内側および前記ゲート絶縁膜の内側に設けられたチャネルボディと、を備えている。そして、前記選択ゲートの側面と前記第2の絶縁層との間に段差部が形成され、前記チャネルボディの前記選択ゲートの上端近傍に位置する領域は、シリサイド化されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

不揮発性半導体記憶装置

【課題】カップリング比の増大と書き込み/消去時のリーク電流の低減とを実現する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、半導体層11と、半導体層11上の第1の絶縁層13と、第1の絶縁層13上の電荷蓄積層14と、電荷蓄積層14上の第2の絶縁層15と、第2の絶縁層15上の制御ゲート電極16とを備える。第2の絶縁層15は、電荷蓄積層14側から制御ゲート電極16側に向かって、第1のランタンアルミネート層LAO、ランタンアルミシリケート層LASO及び第2のランタンアルミネート層LAOを備える。

(もっと読む)

液体噴射ヘッド及び液体噴射装置並びに圧電素子

【課題】クラックの発生が抑制された圧電体層を有する圧電素子を具備する液体噴射ヘッド及び液体噴射装置並びに圧電素子を提供する。

【解決手段】ノズル開口21から液体を吐出する液体噴射ヘッドIであって、圧電体層70と圧電体層70に設けられた電極60,80を備えた圧電素子300を具備し、圧電体層70は、ビスマス、鉄、バリウム及びチタンを含みペロブスカイト構造を有する複合酸化物からなり、平均結晶粒径が120nm以上252nm以下である液体噴射ヘッドIとする。

(もっと読む)

記憶装置及び記憶装置の製造方法

【課題】低電圧で動作する分極率の高い強誘電体メモリを提供する。

【解決手段】基板の上に形成された下部電極と、前記下部電極上に形成された強誘電体膜と、前記強誘電体膜上に形成された上部電極と、を有し、前記強誘電体膜は、第1の強誘電体膜と第2の強誘電体膜とを有しており、前記第1の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料により形成されており、前記第2の強誘電体膜は、チタン酸ジルコン酸鉛を含む材料にRuがドープされているものにより形成されており、前記第2の強誘電体膜において、前記Ruは前記第2の強誘電体膜におけるPb、Zr、Tiのいずれかと置換しているものであることを特徴とする記憶装置により上記課題を解決する。

(もっと読む)

抵抗変化型素子の抵抗状態変化方法

【課題】素子の耐久性の向上を図る。

【解決手段】抵抗変化型素子20に1回以上の第1のパルス電圧を印加することによって抵抗変化型素子20の抵抗状態を高抵抗状態から低抵抗状態に切り替えるセットと、抵抗変化型素子20に1回以上の第1のパルス電圧とは異なる第2のパルス電圧を印加することによって抵抗変化型素子20の抵抗状態を高抵抗状態から低抵抗状態に切り替えるリセットと、の実行によって抵抗変化型素子20の抵抗状態を変化させるものにおいて、リセットを実行する際には、第2のパルス電圧のパルス幅を徐々に大きくする。

(もっと読む)

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートトランジスタや周辺回路部のトランジスタの下部電極の抵抗値を低減し、しきい値電圧の増加も図れるようにする。

【解決手段】ゲート電極の加工時に、選択ゲートトランジスタのゲート電極SGD−SGD間の側壁部と、周辺回路部のトランジスタのゲート電極PGの両側壁とに、多結晶シリコン膜4の上部に段差形状を形成し、傾斜部4dを設ける。ゲート電極の多結晶シリコン膜6のシリサイド加工時に、多結晶シリコン膜4の傾斜部4dからもシリサイド化を進行させ、シリサイド膜7および7aを形成する。これにより、ゲート電極SGDおよびPGの下部電極においても低抵抗化を図ることができる。多結晶シリコン膜4に分断層4aを設けることで、シリサイド反応を停止させたり、設けないでゲート絶縁膜3の部分までシリサイド反応させてしきい値電圧を増加させたりできる。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

強誘電体膜の作製方法

【課題】 良好な規格化保持時間を有するエピタキシャル成長させて得られた強誘電体膜の作製方法を提供すること。

【解決手段】 チタン酸ストロンチウム単結晶基板又はシリコン単結晶基板上に、電極層を介して、強誘電体膜をエピタキシャル成長させて形成し、次いでエピタキシャル成長させて形成された強誘電体膜を冷却する強誘電体膜の作製方法において、この冷却を、少なくとも冷却を開始した後から該強誘電体のキュリー温度より15%高い温度〜15%低い温度の範囲までの冷却速度をその範囲の温度から室温までの冷却速度より遅くして実施する第1冷却工程と、次いで該第1冷却工程の冷却速度より早い冷却速度で室温まで冷却する第2冷却工程とで実施する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

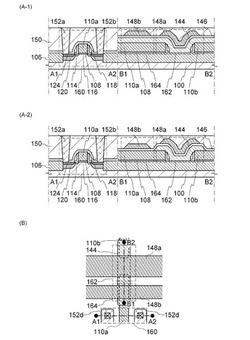

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

光不揮発性メモリ

【課題】光信号を直接不揮発的に記憶する光不揮発性メモリを提供すること。

【解決手段】第1導電型を有する第1半導体層12と、前記第1導電型とは異なる第2導電型を有する第2半導体層16と、前記第1半導体層と前記第2半導体層とに挟まれ、逆バイアスが印加されることにより受光し、順バイアスが印加されることにより発光する活性層14と、前記活性層の受光する光の強さによって磁化方向が変化する強磁性体層20と、を具備する光不揮発性メモリ。

(もっと読む)

61 - 80 / 2,740

[ Back to top ]