Fターム[5F083JA38]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 白金族元素、Au、及び、その合金 (2,740)

Fターム[5F083JA38]に分類される特許

81 - 100 / 2,740

抵抗変化メモリおよびその製造方法

【課題】イオン源電極を構成する金属の凝集を防止することができる抵抗変化メモリおよびその製造方法を提供する。

【解決手段】本実施形態の抵抗変化メモリは、第1配線と、第1配線の上方に設けられ第1配線と交差する第2配線と、第2配線の上方に設けられ第2配線と交差する第3配線と、第1配線と第2配線との交差領域に設けられた第1抵抗変化素子であって、第1配線上に設けられた第1抵抗変化層と、第1抵抗変化層上に設けられ第2配線を貫通するとともに第2配線に接続し金属イオン源を含むイオン源電極と、を有する第1抵抗変化素子と、第2配線と第3配線との交差領域に設けられた第2抵抗変化素子であって、イオン源電極上に設けられた第2抵抗変化層を有する第2抵抗変化素子と、を備えている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性を向上させることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、積層して設けられた複数のゲート電極と、前記ゲート電極の間に設けられた絶縁膜と、を有した積層体と、前記積層体を貫く半導体ピラーと、前記半導体ピラーと前記ゲート電極との間に空隙を介して設けられた電荷蓄積層と、前記電荷蓄積層と前記ゲート電極との間に設けられたブロック絶縁層と、を有したメモリセルを積層方向に複数備えている。そして、前記複数の各メモリセル毎に、前記電荷蓄積層と前記半導体ピラーとの間の距離を保つ支持部が設けられている。

(もっと読む)

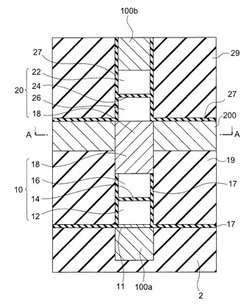

光不揮発性メモリ

【課題】光信号を直接不揮発的に記憶する光不揮発性メモリを提供すること。

【解決手段】第1導電型を有する第1半導体層12と、前記第1導電型とは異なる第2導電型を有する第2半導体層16と、前記第1半導体層と前記第2半導体層とに挟まれ、逆バイアスが印加されることにより受光し、順バイアスが印加されることにより発光する活性層14と、前記活性層の受光する光の強さによって磁化方向が変化する強磁性体層20と、を具備する光不揮発性メモリ。

(もっと読む)

抵抗変化メモリ

【課題】隣接するセル間の電流のリークを防止することができる抵抗変化メモリを提供することを可能にする。

【解決手段】本実施形態による抵抗変化メモリは、第1配線と、前記第1配線と交差する第2配線と、前記第1配線と前記第2配線との交差領域に設けられ、前記第1配線に接続する第1電極と、前記第2配線に接続し、前記第1電極に対向する第2電極と、前記第1電極と前記第2電極との間に設けられた抵抗変化層と、前記第2電極の側部に設けられ、前記第2電極の側部との間に空隙を形成する第1絶縁層および第1半導体層のいずれか一方と、を備えている。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体記憶装置

【課題】TFTなどのトランジスタ特性がばらつく状況や、RF回路から電源が供給され

電源が安定しない状況で、SRAMを作製する場合、従来の1つのメモリセルに6つのト

ランジスタの構成では読み出し時にメモリセルが保持する値が書き換わる誤書き込みが発

生してしまう。

【解決手段】SRAMのメモリセルは、書き込みの回路と読み出しの回路を分離する事に

より、SRAMの誤書き込みを防ぎ、安定した動作を行うことを可能にする。また、書き

込みのタイミングを考慮する事により、誤書き込みを起こさず、より確実に書き込みの動

作を行うことが可能なSRAMを提供する。

(もっと読む)

電解質メモリ素子

【課題】 低電圧駆動可能で低消費電力型の不揮発性メモリ素子およびその製造方法を提供する。

【解決手段】 本発明のある態様においては、対向配置された第1基体10Aおよび第2基体20Aと、第1基体および第2基体に挟まれる電解質層30とを備えるメモリ素子1000が提供される。第1基体の基板12の一の面12Sの上には、二酸化バナジウムを主成分とするメモリ層100Aが形成され、メモリ層に接している第1電極部110Aと第2電極部120Aとを有している。第2基体の対向基板22は、第1基体に対向する面の上に第3電極部230Aを有している。そして電解質層30は、第1電極部と第2電極部との間においてメモリ層に近接している。本発明のある態様においては、一方の基体に第1〜第3電極部とメモリ層とが形成された別の典型的なメモリ素子2000も提供される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】SiN膜等の犠牲膜の残存を防止する。

【解決手段】一の実施形態による不揮発性半導体記憶装置の製造方法では、基板上に、複数のメモリセルトランジスタと、複数の選択トランジスタとを形成する。さらに、前記方法では、前記メモリセルトランジスタ間と、前記メモリセルトランジスタと前記選択トランジスタとの間と、前記選択トランジスタ間に、第1から第5の絶縁膜を順に埋め込む。さらに、前記方法では、前記選択トランジスタ間の前記第2及び第4の絶縁膜が一部残存するように、第1のエッチング処理により、前記第2及び第4の絶縁膜を除去する。さらに、前記方法では、前記選択トランジスタ間に残存した前記第2及び第4の絶縁膜を、前記第1のエッチング処理後に行う第2のエッチング処理により除去する。

(もっと読む)

マンガン酸化物、マンガン酸化物を備える強誘電体メモリ素子、および強誘電体メモリ装置

【課題】主成分として有害物質鉛元素を含まずに、強誘電性を示しかつ外部磁場によって分極の大きさを制御可能な新規なマンガン酸化物、およびそのメモリへの利用を提供する。

【解決手段】マンガン酸化物は、ペロブスカイト構造を有する、式(1)Sr1−xBaxMnO3(1≧x>0.4)・・・(1)で表されるマンガン酸化物である。単位格子1の対称中心には磁性イオンであるMnイオン3が存在する。単位格子1の対称中心をMnサイトとする。単位格子1が有する8個の頂点には、SrイオンおよびBaイオンのうちいずれか一方が存在している。単位格子1が有する頂点をSrサイト2とする。単位格子1が有する6面の面心には、Oイオン4が存在する。

(もっと読む)

不揮発性抵抗変化素子

【課題】デバイス特性の劣化やバラツキを低減でき、整流機能を有する不揮発性抵抗変化素子を提供する。

【解決手段】金属元素を含む上部電極1と、n型半導体を含む下部電極2と、上部電極1と下部電極2との間に配置され、上部電極1が含む金属元素から構成される導体部を有する抵抗変化層3とを備える。抵抗変化層3が有する導体部は下部電極2との間に離間を有している。

(もっと読む)

電気化学素子および電気化学素子を用いた相補型回路

【課題】従来の電気化学素子とは逆極性でオンオフ動作を行うイオン移動型電気化学素子を提供する。この素子を従来型の電気化学素子とを組合せれば、低消費電力の相補型回路を構成できる。

【解決手段】イオン拡散材料として使用する酸化タンタルを挟んで一方にゲート電極を配置し、もう一方に絶縁物材料によって隔てられたソース電極とドレイン電極を配置する。このとき、ソース・ドレイン電極間の電気的接続を実現するゲート電圧(オン電圧)がオフ状態を実現するゲート電圧(オフ電圧)よりも低い電気化学素子が得られる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】充分なキャパシタ容量を有する半導体装置を提供する。

【解決手段】半導体装置100の製造方法は、次の工程を含む。まず、基板(半導体基板102)上に下部電極152を形成する。次いで、下部電極152を第1結晶化処理する。次いで、第1結晶化処理後の下部電極152の上に容量絶縁層154を形成する。次いで、容量絶縁層154を第2結晶化処理する。この後、容量絶縁層154上に上部電極156を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、MTJ素子がコンタクトプラグ内のシームまたはボイドの影響を受けることなく、MTJ素子の特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数のセルトランジスタは、半導体基板上に設けられている。コンタクトプラグは、隣接するセルトランジスタ間に埋め込まれ、該隣接するセルトランジスタ間にある拡散層に電気的に接続されている。層間絶縁膜は、複数のコンタクトプラグ間を埋め込む。記憶素子は、コンタクトプラグの上方に設けられておらず、層間絶縁膜の上方に設けられている。側壁膜は、記憶素子の側面の少なくとも一部を被覆し、半導体基板の表面上方から見たときに、コンタクトプラグに重複するように設けられている。下部電極は、記憶素子の底面と層間絶縁膜との間、および、側壁膜とコンタクトプラグとの間に設けられ、記憶素子とコンタクトプラグとを電気的に接続する。

(もっと読む)

記憶素子およびその製造方法ならびに記憶装置

【課題】低電流動作に優れると共に良好な保持特性を有する記憶素子および記憶装置を提供する。

【解決手段】本開示の記憶素子は、第1電極、記憶層および第2電極をこの順に有し、記憶層は、第1電極側に設けられた抵抗変化層と、少なくとも1種の金属元素を含むと共に、第2電極側に設けられたイオン源層とを備え、イオン源層は、テルル(Te),硫黄(S)およびセレン(Se)のうちの少なくとも1種のカルコゲン元素を含むと共に、抵抗変化層側に設けられた第1イオン源層と、第1イオン源層とはカルコゲン元素の含有量が異なると共に、第2電極側に設けられた第2イオン源層とからなる。

(もっと読む)

半導体装置

【課題】プロセス技術が比較的簡単、且つ、少ない素子数で多値情報を記憶することがでるメモリを提供する。

【解決手段】メモリ素子426において、第1の記憶素子における第1の電極417の形状の一部を、第2の記憶素子における第1の電極417の形状と異ならせることで、第1の電極417と第2の電極420の間の電気抵抗が変化する電圧値を異ならせて、1ビットを越える多値の情報の記憶を一つのメモリセルで行う。第1の電極417を部分的に加工することで単位面積当たりの記憶容量を増大することができる。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

パターン形成用基板、圧電アクチュエータ製造方法、圧電アクチュエータ、液滴吐出ヘッド、および、液滴吐出装置

【課題】流動体を付着させて熱処理を行う工程を繰り返し行うことにより微細パターンの膜を所望の膜厚で精密に作製可能とするパターン形成用基板と、パターン形成用基板を用いた圧電アクチュエータの製造方法を提供する。

【解決手段】所定の流動体を特定領域に付着させて熱処理を行うことによりパターン化された膜を形成するためのパターン形成用基板10で、特定領域を親和性とし、それ以外の領域を非親和性とする表面改質をおこなう。パターン形成用基板10の表面改質処理対象となる金属膜はPt膜53を積層し、基体として、Ti,Ta,Zr,V,Nb,Mo,Wから選ばれる少なくとも1つの金属元素、酸素元素および炭素元素から構成されるMOC膜52を用いる。

(もっと読む)

81 - 100 / 2,740

[ Back to top ]